RAM(Random Access Memory)

특징: volatile memory(휘발성 메모리)

CPU는 실행하고 싶은 프로그램을 보조기억장치에서 RAM으로 복사하여 저장한 뒤 실행한다.

RAM의 종류

1. DRAM(Dynamic RAM)

저장된 데이터가 동적으로 변하는 RAM

-> 그렇기때문에 데이터의 소멸을 막기 위해 일정 주기로 데이터를 다시 저장하는 과정이 필요하다.//소비전력이 낮고 저렴하고 집적도가 높아 일반적으로 많이 이용

2. SRAM(Static RAM)

저장된 데이터가 정적이다. 시간이 지나도 변하지 않는다.

-> 데이터 재활성화가 필요없어 일반적으로 속도가 더 빠르다.//집적도, 소비전력, 가격 등 DRAM보다 소모값이 크다.

3. SDRAM(Synchronous Dynamic RAM)

클럭 신호와 동기화된 DRAM

-> DDR SDRAM(Double Data Rate SDRAM)은 대역폭을 넓혀 속도를 빠르게 한 SDRAMSDR -> DDR2 ->...DDR5 식으로 대역폭이 두배씩 증가하게 된다.

메모리 주소공간의 구조

Physical address(물리 주소)

-> 정보가 실제로 저장된 HW상의 구조

Logical address(논리 주소)

-> 실행 중 프로그램 각각에게 부여된 주소

MMU(Memory Management Unit)

논리 주소와 물리 주소 간의 변환을 수행하는 하드웨어

CPU와 주소 버스 간 사이에 있다.

MMU안에는 base register가 있어 이 base register 값(가장 작은 Physical address)을 기반으로

MMU는 물리 주소에 접근하게 된다.

이 때 프로그램이 논리 주소 범위를 벗어나는 명령어를 실행하는 것을 방지하기 위해 (다른 프로그램을 침범하지 않도록) Limit register가 존재한다.

e.g)

base register: 200

limit register: 300

-> 해당 프로그램의 logical address 범위는 200~500이 된다.

Cash Memory

Cash를 사용하는 이유

-> 메모리 접근 시간을 절약하여 CPU의 효율을 높이기 위함

그렇다면 메모리로부터 어떤 기준으로 데이터를 가져 올 것인가?

-> Locality of Reference, principle of locality(참조 지역성의 원리)

- CPU는 최근 접근한 메모리공간에 다시 접근하려는 경향

-> 시간 지역성(temporal locality)- CPU는 접근한 메모리 공간 근처를 접근하려는 경향

-> 공간 지역성(spatial locality)

Cash hit

-> 캐시 메모리 내 데이터가 CPU에서 활용될 경우

Cash miss

-> 예측이 틀려 필요한 데이터를 직접 메모리에서 가져와야 할 경우

Cash hit/(Cash hit + Cash miss)을 Cash hit ratio(캐시

적중률)이라고 한다.

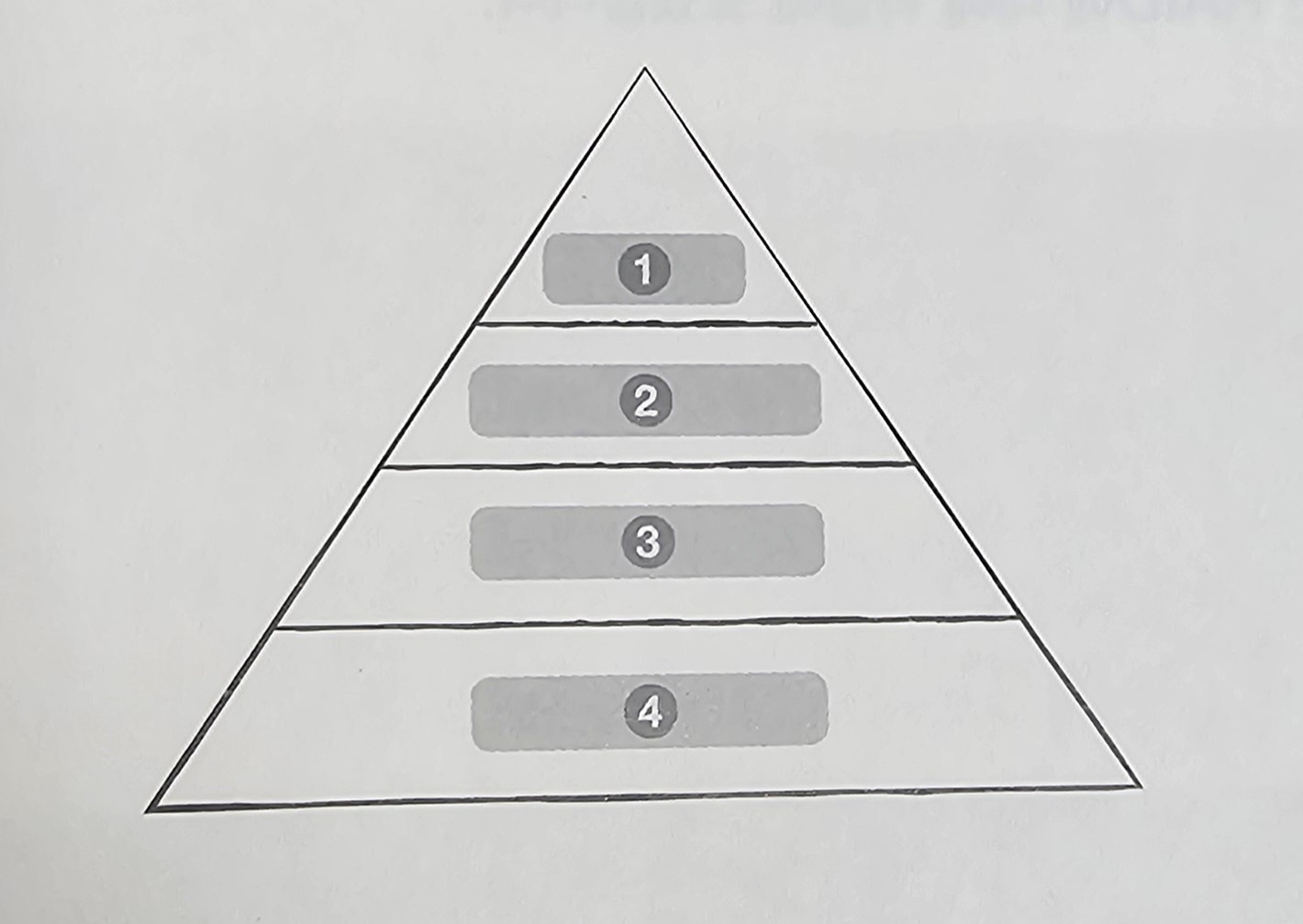

memory hierarchy(저장 장치 계층 구조)

//register -> cash memory -> memory -> auxiliary storage(보조기억장치) 순으로

비싼 가격, 높은 속도, 작은 용량의 성격을 지닌다.

Cash memory는 CPU와 memory 사이에 위치하여 register보다 용량이 크고 memory보다 빠른 SRAM(Static RAM) 기반의 저장 장치이다.

//마치 proxy server처럼 작동한다.Cash memory의 구성

코어로부터 가까운 순서대로 L1, L2...이런식이며

memory hierarchy처럼 코어와의 거리에 따라 가격 등의 특징이 유사하다.

통상적으로 L1,L2 cash는 보통 코어 내부에, L3는 외부에 위치한다.

HDD(Hard Disk Device)

자기적인 방식으로 데이터를 저장하기 때문에 Magnetic Disk(자기 디스크)의 일종으로 지칭하기도 한다.

용어정리

Platter(플래터) -> 하드 디스크에서 실질적 데이터 저장소인 원판

Spindle(스핀들) -> 플래터 회전기

RPM(Revolution per minute) -> 분당 회전속도

Head(헤드) -> 데이터 Read/Write

Disk Arm(디스크 암) -> 헤드 이동기

Track(트랙) -> 플래터의 동심원 한개

Sector(섹터) -> 트랙 중 한 조각(512~4096byte등의 크기)

//하나 이상의 섹터를 묶어 block이라고도 한다.cylinder(실린더) -> 여러 겹의 플래터 상 같은 트랙이 위치한 곳을 모은 논리적 단위

Seek Time(탐색시간) -> 데이터가 저장된 트랙까지 헤드 이동시간

Rotational Latency(회전 지연) -> 헤드 있는곳으로 플래터 회전시간

Transfer Time(전송 시간) -> HDD와 컴퓨터 간 데이터 전송시간

Flash memory

-> USB, SD card, SSD등 전기적으로 데이터를 읽고 쓸 수 있는 반도체 기반 저장장치

SLC type -> 한 cell당 1비트 저장가능

아래 두 타입보다 상대적으로 빠른 IO가 가능하고 수명 또한 길지만 용량 대비 가격이비싸다.MLC type -> 한 cell당 2비트 저장가능

TLC type -> 한 cell당 3비트 저장가능

위 두 종류는 SLC 타입보다 속도, 수명 등에서 약점을 보이지만

용량 대비 가격이 싸다는 장점이 있다.Flash memory의 데이터 크기 단위

cell -> 플래시 메모리에서 데이터를 저장하는 가장 작은 단위

page -> 셀들이 모여 만들어지 단위

block -> 페이지가 모여 만들어진 단위

plane -> 블록이 모여 만들어진 단위

die -> 플레인이 모여 만들어진 단위

garbage collection

-> 메모리 삭제는 블록 단위로 수행되기 때문에

SSD 등의 플래시 메모리에서 쓰레기값 정리를 위해 도입된 기능

(유효 page만 복사 -> 새 블록에 해당 page만 옮기기 -> 기존 블록 삭제)

RAID(Redundant Array of Independent Disks)

하드 디스크와 SSD를 사용하는 기술이며 데이터의 안전성 혹은 높은 성능을 위해 여러 개의 물리적 보조기억장치를 마치 하나의 논리적 보조기억장치처럼 사용하는 기술이다.

level 0~6...등 다양한 종류가 있다.

Device controller(장치 컨트롤러)

IO device와 CPU는 전송률(transfer rate)이 달라 통신이 어려움

-> Device controller는 다음 기능들을 통해 위와같은 통신 문제들을 해결한다.

1. CPU와 IO device간의 통신 중개

2. 오류 검출

3. Data buffering

-> 주고받는 데이터 buffer라는 임시 저장공간에 저장했다 전송해 두 기기 간 전송률을 맞추는 방법

Device controller의 내부 구조 중 대표적 3가지

1. Data register -> io간 데이터 담기는 레지스터(buffer)

2. Status register -> io디바이스 상태 정보 저장

3. control register -> io디바이스 수행할 내용 제어정보, 명령 저장

Device Driver(장치 드라이버)

device controller의 동작 감지, 제어하면서

cpu와 io device간 소프트웨어적인 통로의 역할을 수행한다.

그렇다면 어떻게 정보를 주고받는지??

-> 크게 3가지 방법

1. Programmed I/O

프로그램 속 명령어로 IO device를 제어한다.

이 때 메모리 맵 입출력, 고립형 입출력 등의 방법이 있다.

메모리 맵 입출력-> 메모리에 접근하기 위한 주소 공간과 IO device에 접근하기 위한 주소 공간을 하나의 주소 공간으로 간주하는 방법

고립형 입출력 -> 메모리를 위한 주소 공간과 IO device를 위한 주소 공간을 분리하는 방법

2. Interrupt-Driven I/O

CPU가 입출력 명령을 Device controller에게 보내면 IO 작업이 끝난 후에 Device controller가 interrupt를 걸어 CPU가 interrupt service routine을 실행하는 구조

동시에 여러 IO Device로부터 여러 interrupt가 발생하면

PIC(Programmable Interrupt Controller)라는 하드웨어를 사용하여 여러 Device controller로부터의 interrupt의 우선순위를 판단한 뒤 CPU에게 알려준다.

e.g)

PIC -> CPU (인터럽트 요청)

CPU -> PIC (인터럽트 확인 신호)

PIC -> CPU (interrupt vector)

CPU -> (interrupt service routine)

3. DMA(Direct Access Memory) I/O

DMA controller를 통해 DMA가 CPU와 IO devices 중간에서 작업 수행한 뒤 작업 끝나면 CPU에게 interrupt거는 구조

IO device와 메모리 사이 전송되는 모든 데이터가 반드시 CPU를 거쳐야 한다면 CPU연산부담이 증가 -> DMA도입

그러나 DMA를 위해 시스템 버스를 너무 자주 사용하면 CPU가 시스템 버스를 사용할 때 지장이 가므로 DMA와 IO device를 PCI버스, PCI Express버스 등 별개의 버스를 통해 연결하는 방식이 존재한다.

숙제

1. P185 확인문제 3번

주로 캐시 메모리로 활용됩니다. -> SRAM

주로 기억장치로 활용됩니다. -> DRAM

대용량화하기 유리합니다. -> DRAM

집적도가 상대적으로 낮습니다. -> SRAM

2. P205 확인문제 1번

1. 레지스터

2. 캐시 메모리

3. 메모리

4. 보조기억장치

Ch.07(07-2) RAID의 정의와 종류를 간단히 정리해 보기

RAID란?

Redundant Array of Independent Disks의 약자로써

하드 디스크와 SSD를 사용하는 기술이며 데이터의 안전성 혹은 높은 성능을 위해 여러 개의 물리적 보조기억장치를 마치 하나의 논리적 보조기억장치처럼 사용하는 기술이다.

RAID는 구성 방법에 따라 RAID 0, RAID 1,... RAID 50등 RAID level로 나뉘게 되는데

RAID 0은 단순히 데이터를 하드 디스크 개수만큼 나누어 저장하는 것이다. 속도는 빠르나 오류에 취약하다.

RAID 1은 미러링(mirroring)이라고도 불리우며 복사본을 만들어 복구에 초점을 두었으나 복사본 만큼의 용량을 추가적으로 사용한다는 단점이 존재한다.

RAID 4는 parity bit를 통해 오류를 검출하고 복구하는 방식이다.

RAID 5는 RAID 4에서 parity를 저장하는 장치가 bottleneck현을 겪는 것을 보완하기 위해 parity 정보를 분산 저장하게 된다.

RAID 6는 RAID 5에서 parity를 2개로 저장한다는 점이 추가된 방식이다.

RAID 50은 하위 배열은 RAID 5, 상위 배열은 RAID 0 방식을 취한 방식이다.

이번 주차 간 공부하면서 궁금했던 점들 Q&A

Q1. 캐시 메모리가 마치 네트워크에서 프록시 서버와 비슷한 성격을 느끼는 것 같은데 개념적으로 타당한 생각인가?

A: 컴퓨터 구조에서의 캐시 메모리와 네트워크에서의 프록시 서버는

데이터 접근 속도, 부하 분산 등의 관점에서 효율성을 증진시킨다는 점에서 비슷하다고 한다.

Q2. 멀티 레벨 캐시 메모리에 대해 더 자세히 알아보면?

A: CPU에 데이터가 필요한 경우 먼저 연결된 코어의 L1 캐시를 검색한다.

이를 찾을 수없는 경우 L2 및 L3 캐시가 다음에 검색된다.

필요한 데이터가 발견되면 이를 cash hit라고 하며

반면에 데이터가 캐시에 없으면 CPU는 데이터를 주 메모리 또는 스토리지에서 캐시로 로드하도록 요청한다. 이것이cash miss라고 한다.

(캐시 히트와 캐시 미스의 발생 상황을 구체적으로 알 수 있었다.)

마지막 레벨의 칩 내에 위치한 캐시를 LLC(Last Level Cash)라고 한다.

Q3. HDD에서의 플래터 read/write방식이 CD의 data를 read/write하는 방식과 유사한지?

A: 디스크가 회전하는 방식이라는 점. 트랙과 섹터라는 단위를 사용한다는 점이 유사하지만HDD는 자기 기록 방식이고 CD는 광학 기록 방식이라는 큰 차이가 존재한다고 한다.

또한 HDD는 random access가 가능하지만 CD는 sequential access에 가까워 접근 속도가 상대적으로 느리다고 한다.

이 외에도 다양한 차이가 있기 때문에 원형으로 저장된 데이터를 읽고 쓴다는 점 말고는

서로 차이가 굉장히 큰 데이터 저장 방식인 것 같다.

느낀 점 및 4주차 목표

velog를 통해 정리하면서 새로운 기능을 알게 되었다!

컴구+운체를 공부하는 만큼 블로그 기능 또한 스킬업 하는 것 같아 뭔가 사은품 받은 기분이다ㅋㅋㅋ 이번 주차는 비도 너무 많이오고 또 그만큼 날씨가 후덥지근해서 너무 힘들었지만 그래도 다 공부하고 이렇게 velog로 작성까지 마치니 성취감이 더 컸던 것 같다. 그럼 4주차도 화이팅!!