Quartus

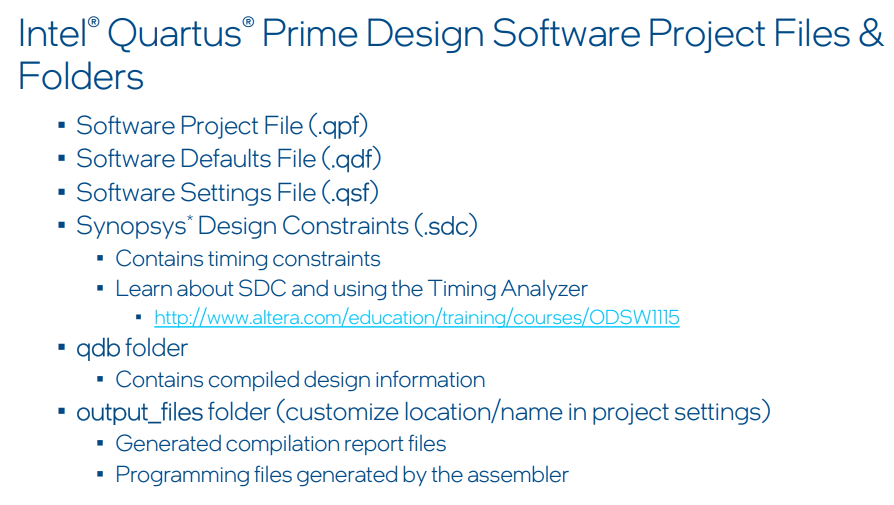

1.Quartus 확장자

2.Quartus의 개략적 순서

https://blog.naver.com/jinsoo91zz/220415179380

3.Quartus - user IP 경로 추가

좌측 네비게이터에서 우클릭 -> Setting -> IP and Development Board Search Settings -> 경로 추가

4.Quartus - Platform Designer에서 Generate HDL할시 옵션

언어 : VHDLSimulation : modelsim 체크Output Directory : Clear~ 체크

5.Quartus IP 생성 대략적인 순서

IP 블록 생성(자체로는 Top의 인스턴스로 넣을 수 없음) -> entity 또는 Module을 만들어 IP Block을 감싼다 -> entity 또는 Module의 내부 신호들을 만들고 연결한다.테스트 진행을 위해 TestBench를 만들어 만들어놓은 IP블럭용 e

6.platform designer = block design

쿼터스의 플랫폼 디자이너는 비바도의 블록 디자인과 같다여기서 ip들을 불러와서 설계 할 수 있다만들어놓은 디자인을 새롭게 만들 디자인 밑에 붙이려면 만들어놓은 디자인의 저장 경로를 쿼터스의 assignment메뉴에서 setting에서 ip관련 설정에 들어가서 위와 아래

7.template-컴포넌트 선언 없이 사용

쿼터스에서 기본 제공하는 템플릿을 사용하면 vhdl에서 컴포넌트를 선언하지 않아도 portmap만 연결하여 모듈을 바로 사용 가능new -> vhdl file -> 새로 열린 탭의 메뉴에서 insert template

8.입출력 값이 같은 Clock Source

입출력 값이 같은데 굳이 clock source ip를 사용하는 이유는 platform design에서 클락이나 리셋 값을 사용하려면 해당 ip (clock source나 reset bridge)사용 해야하는것 같다 (아마 해당 신호 값이 클락 또는 리셋값임을 plat

9.Achive

achive로 프로젝트를 하나로 압축?묶어서 다른 환경에서 achive파일을 실행하면 진행했던 프로젝트를 다시 온전히 압축해제해서 사용할 수 있는데 이때 전에 해놨던 ip generate, 등 다 같이 그대로 담겨있어서 compile을 해도 그대로 잘 되지만 바뀐 환경

10.example design

ip catalog -> 각 탭들에서 parameter 설정 -> example design 탭 설정 -> 우상단 Generate example design 버튼 클릭xilinx에서는 거의 다 되지만 quartus에서는 지원되는 ip가 있고 안되는 것도 꽤 있다.

11.example design을 시뮬레이션 보기

example design을 이용한 questa 사용은 questa 항목으로

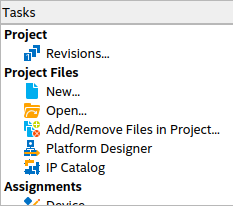

12.quartus의 소스파일, ip파일 추가

기본적으로 Add/Remove Files in Project에서 파일들을 추가 제거를 한다이때 프로젝트에 사용되는 소스파일 모두(하위 모듈의 소스파일도)를 추가한다(.v, .vhdl, .sv) 사용된 IP는 .ip파일을 추가하면 되고(IP파일 하위의 소스파일은 추가하는

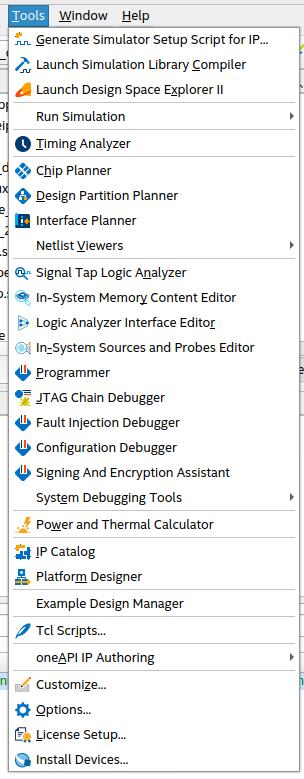

13.라이센스 등록 설정

라이센스 셋업 클릭오른편 라이센스 파일의 오른 끝쪽 드롭다운하여 라이센스가 있는 경로를 추가 라이센스가 여러개라면 경로들 사이에 ; 를 추가하여 여러개 등록 (ex))home/folder1/license1; home/folder1/folder2/license2; hom

14.IP사용시 예제 얻기

쿼터스에서도 가끔 지원해 주는것이 있다.