SoC와 PMIC(power management IC)를 연결하여 전력소모를 줄이는 MIPI interface

power를 monitor 하고 조절하는 역할을 함

효율성 높이는 방법: dynamic frequency, voltage scaling

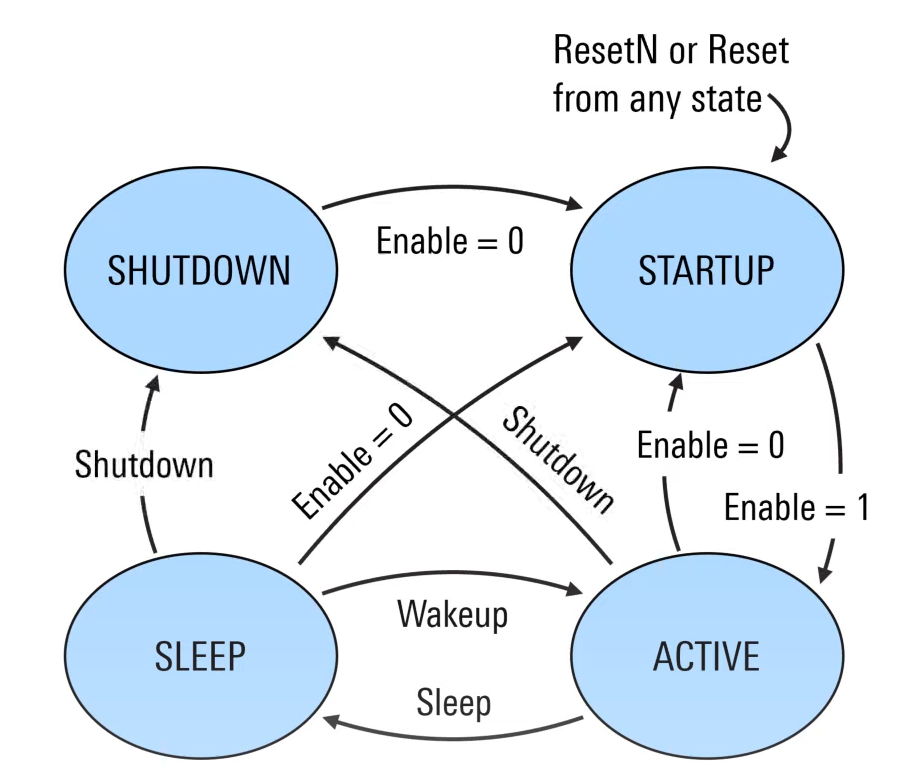

power 줄이는 방법: sleep, shutdown, wake등

SPMI technical overview

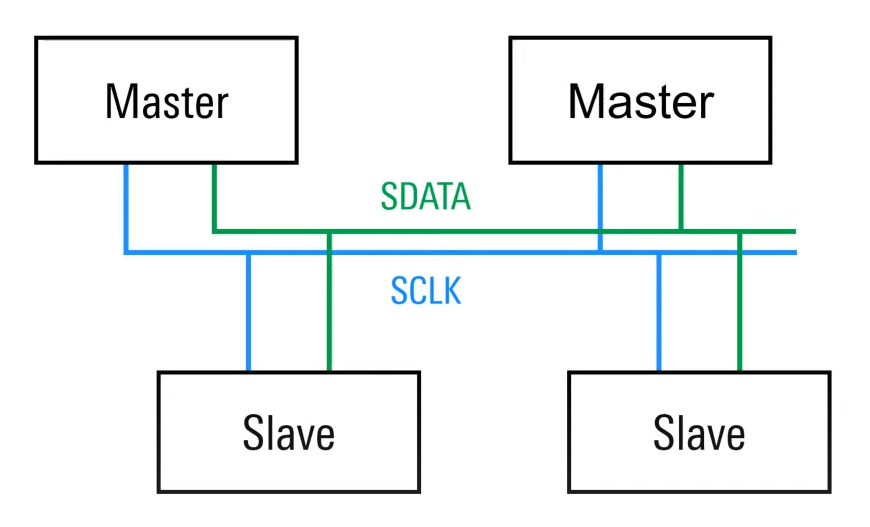

2 wire shared serial bus

- SCLK : 단방향 serial clock

- SDATA : 양방향 serial clock

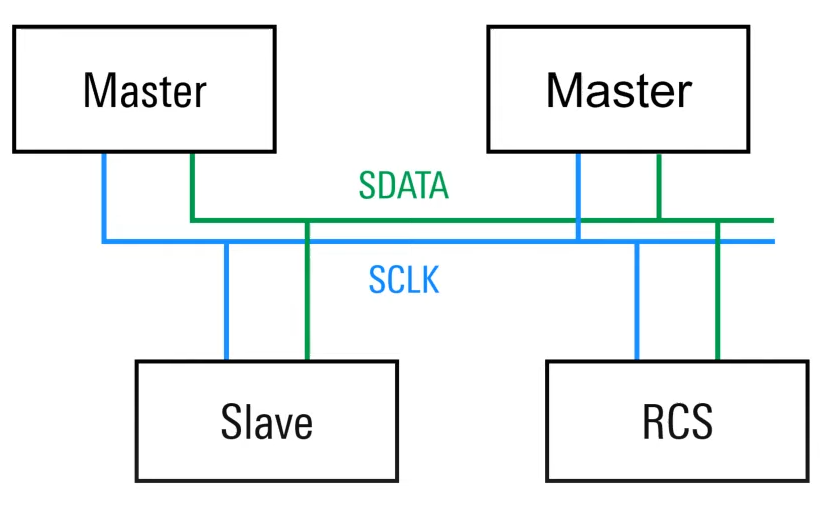

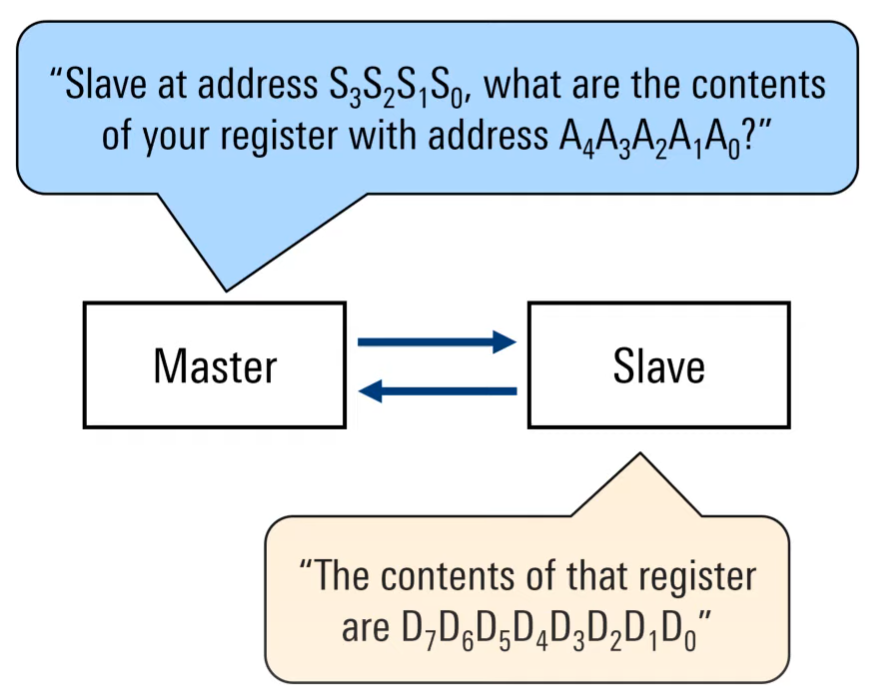

master-slave operation

- 4개의 master, 16개 slave

- bus owner master가 bus control, SCLK 생성

- some slaves may be request-capable(RCS)

two signal levels (+1.2V and +1.8V)

two speed classes

- High speed(HS) : 32 kHz to 26 MHz

- Low speed(LS) : 32kHz to 15MHz

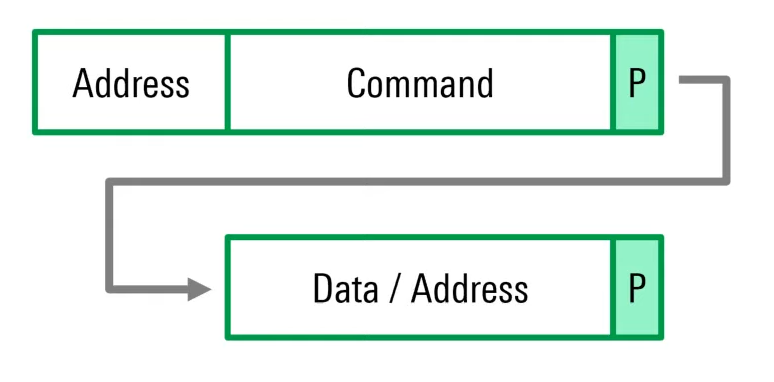

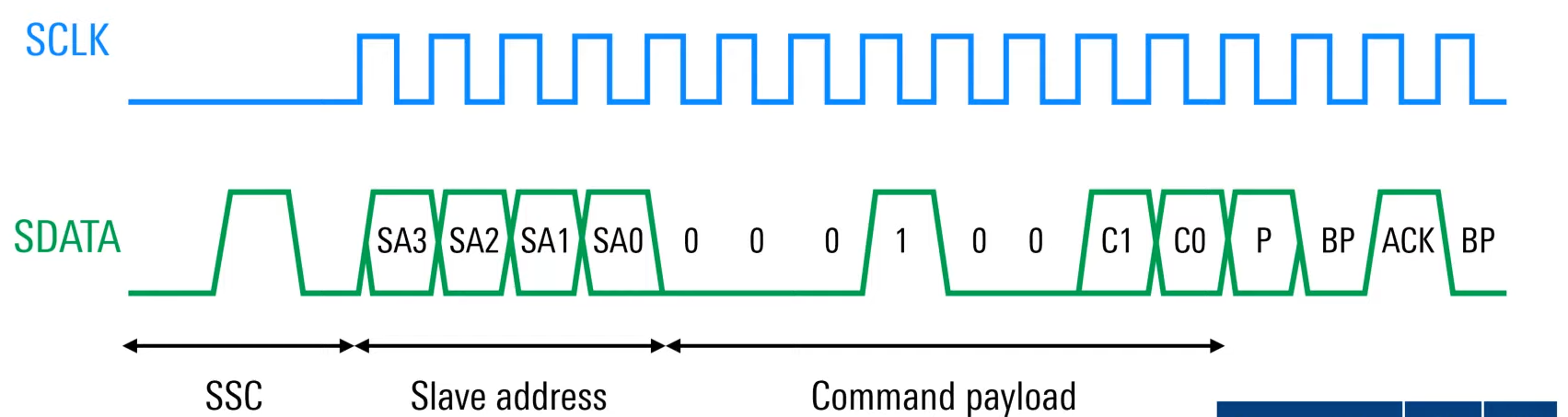

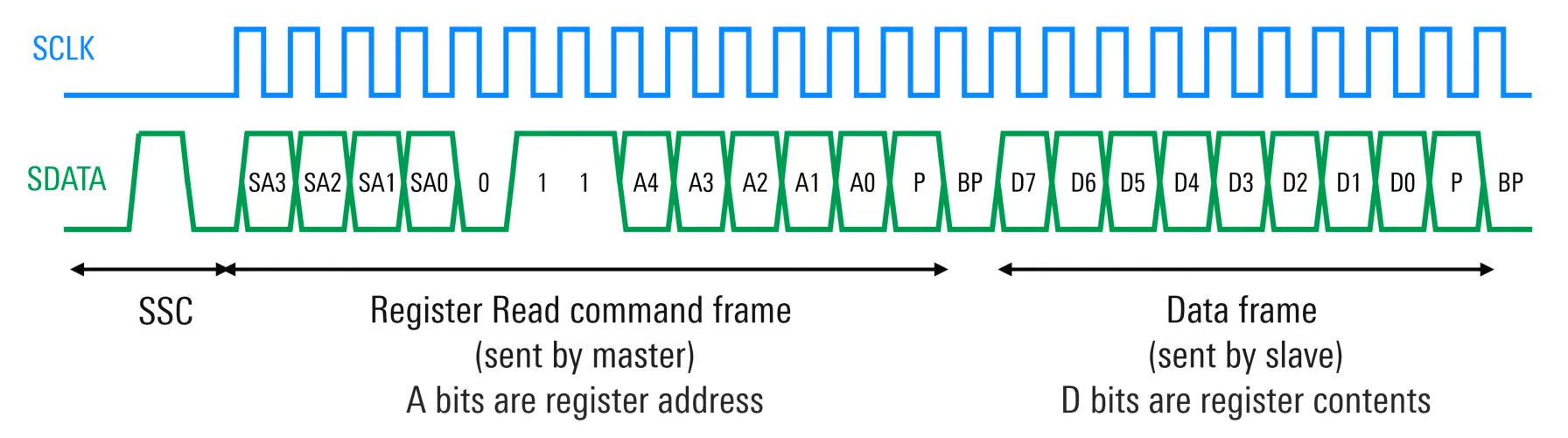

command sequence

bus transaction은 command sequence에서 발생

- sequence 사이에서 bus는 idle(SCLK, SDATA : 0)

command sequence는 4parts로 구성

- sequence start condition (SSC)

- Frame Transmission

addr, command, data/addr byte, parity bit - bus park cycle

- ACK bit

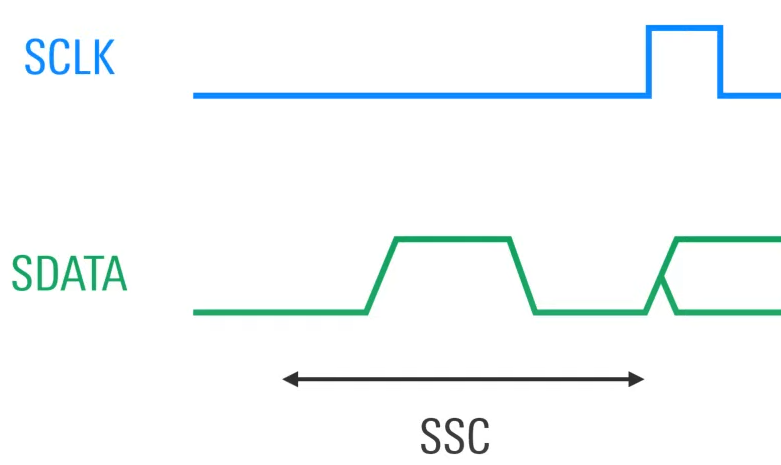

sequence start condition(SSC)

command sequence의 시작을 나타냄

SCLK가 0일 때 SDATA가 0-1-0이 되면 SSC

SSC이후, bus owner master가 clock, frame전송 시작

Frame Transaction

3type of SPMI frames

- command frames

master or slave address + command type(sleep, R/W등) - Data/ Address frame

Data(D) or Address(A) bits

read or write register data - No response frames

SDATA가 low일 때 clock만 발생

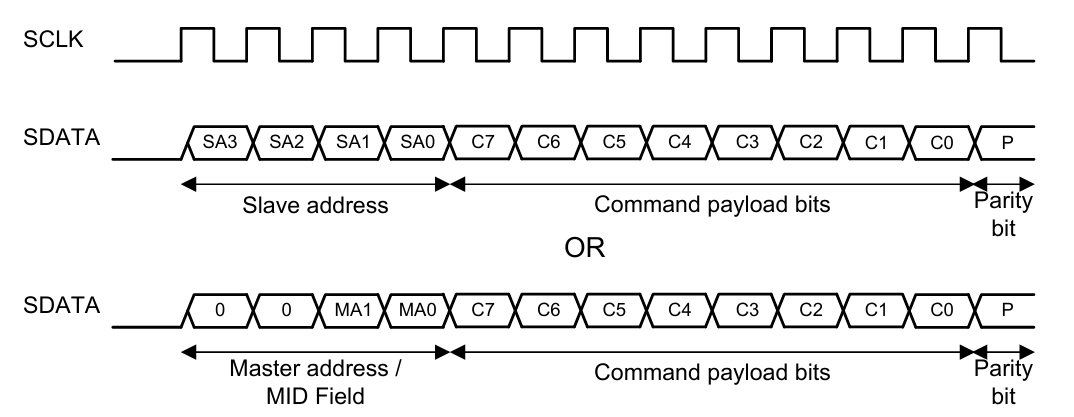

Command Frame

4bit address field + 8bit command paload + parity bit

all bus device have unique address

address type

- Master identifier(MID) : 2it

- Slave identifier : 4bit

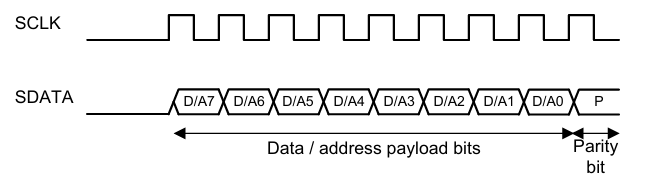

Data and Address Frames

8bit Data or address + parity bit

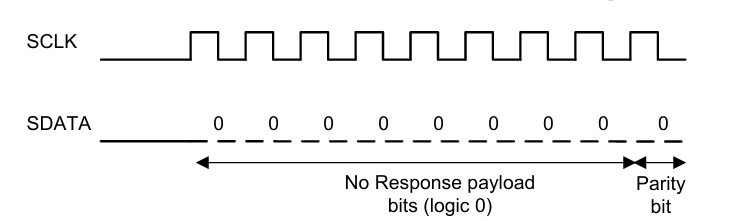

No Response Frame

parity bit를 포함한 모든 bit는 0(SDATA가 pull-down됨)

Data frame인 경우 9bits, Command frame인 경우 13bits

parity bit

error check를 위해 odd parity 사용

parity bit(P)를 사용해 frame에 총 1의 갯수가 홀수가 되게 만듦

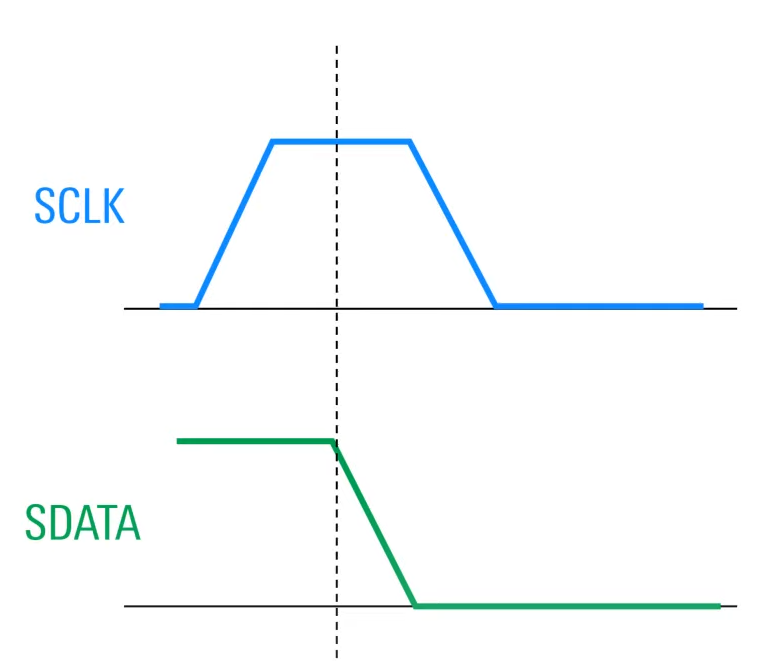

Bus Park

bus park(BP)를 이용해 bus를 release함

SCLK 중간에 SDATA가 0이 되면 BP신호

BP신호 이후 bus가 idle state가 되고, 다른 device가 bus를 사용 가능

ACK Bit

Master가 Frame을 보내고 BP신호를 보내면 slave가 SDATA control 가능.

frame을 받았으면 slave가 ACK신호를 보내고 BP를 통해 bus release

ACK/NACK 는 Read, Authenticate, Transfer Bus Ownership Command를 제외한 모든 동작에서 사용.

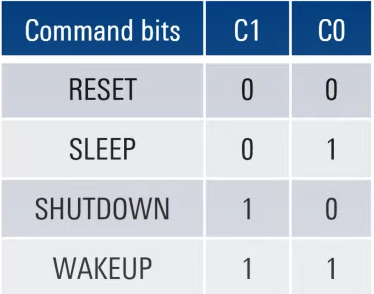

SPMI commands

- state management commands

- Register access commands

- Authentication command

- Transfer bus ownership command

state management commands

외부 signal(enable, resetn)이 slave의 state 변경

- Reset : slave를 STARTUP state로 만듦

- Sleep : slave를 SLEEP state(lower power state)로 만듦

- Wakeup : slave를 SLEEP state에서 ACTIVE state로 변경

- Shutdown : slave를 SHUTDOWN state로 변경

state management command format

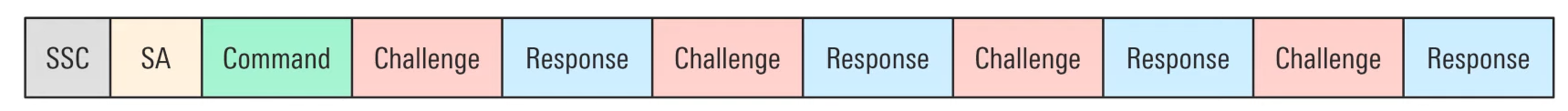

Authentication command

Master와 Slave가 신원을 확인하여 보안기능을 하는 역할

SSC - SA - Command - 동장 과정에서 command에 0x14를 입력하면 authentication 이 수행됨

Master가 4개의 challenge frame을 입력, Slave가 4개의 response frame을 입력.

challenge/response frame은 교차로 나타나며 제조사에서 정하고 암호화됨

Register access commands

read or write data to/from registers on a device

data/address commands contain Master/slave address, register address, register contents

register access command가 다양한 주소범위, data크기에 따라 다양하게 설계될 수 있음

Transfer bus arbitration

Bus owner master (BOM) manages arbitration

ownership은 다른 master에게 transfer bus ownership command로 넘길 수 있음