CPU

앞으로 배울 내용은 '중앙 처리 장치(central processing unit)' 또는 'CPU'이다. CPU는 램에 들어 있는 바이트를 이용해서 어떤 일을 수행하고, 수행한 결과를 램에 보내준다. 한 마디로 말하면 CPU는 바이트를 '처리하는' 장치.

- 램은 오른쪽

- 버스는 램에 있는 a 단자부터 시작해서 커다란 루프 형태로 외곽을 순환하여 i/o 단까지 연결.

- 레지스터 6개(R0, R1, R2, R3, TMP, ACC) - 모두 버스 연결

- CPU는 바이트를 '처리'하는 장소로 레지스터를 사용.

- 제어 장치는 CPU와 램 안에 들어있는 입력 제어 단자 s와 출력 제어 단자 e에 들어오는 비트를 0이나 1로 만들어서 입력과 출력을 통제하는 장치

- R0, R1, R2, R3는 단기 기억용 레지스터 / CPU가 어떤 일을 수행하는 데 필요한 바이트를 임시로 기억하는 용도로 쓰임. (= 범용 레지스터)

- TMP : 버스를 통해 들어오는 바이트를 일시적으로 기억하는 용도로 쓰임. 입력 제어 단자 s를 1로 만들어 주면 버스를 통해 들어오는 바이트가 TMP로 설정. 동시에 TMP 안에 설정된 바이트가 그대로 출력되어 아래쪽으로 내려가 물음표가 쓰인 상자 2개로 들어감. s 단자는 있지만, e 단자는 없으므로 항상 데이터를 출력.

- ACC(accumulator) : 커다란 물음표가 붙은 상자에서 나오는 바이트 하나를 일시적으로 저장하는 장치. 버스로 출력되어 다른 부품에 입력으로 들어감.

CPU와 램 안에 들어 있는 레지스터는 컴퓨터가 작동하는 과정에서 바이트 데이터를 보내고 받는 장소. 레지스터는 버스로 출력을 보낼지 여부를 제어할 수 있고, 버스에 있는 바이트 데이터를 받아들일지 여부도 제어할 수 있음.

OR, XOR 게이트

OR 게이트

두 입력을 부정해서 NAND 게이트에 보냄.

입력 2개가 모두 0이라면 출력도 0. a나 b가 1이거나 두 입력이 모두 1이면 출력은 1.

다수의 입력을 취할 수 있도록 확장 가능.

원래 있던 2입력 OR 게이트에서 나오는 출력을 추가된 OR 게이트의 첫 번째 입력으로 연결.

새로운 입력 와이어를 추가된 OR 게이트의 두 번째 입력으로 연결.

추가된 OR 게이트에서 나오는 출력이 바로 3입력 OR 게이트의 최종 출력.

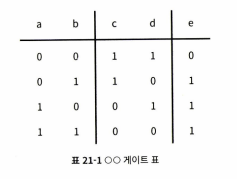

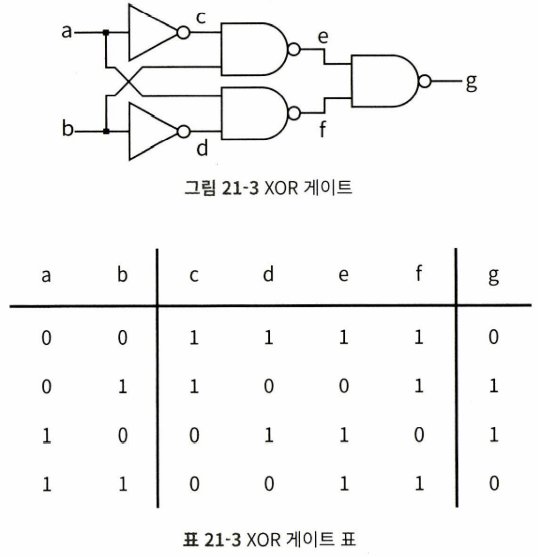

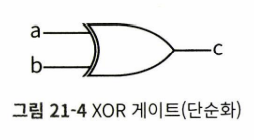

XOR(exclusive OR) 게이트

OR 게이트와 달리 입력이 둘 다 1일때 출력이 0

한쪽 입력만 배타적으로 1이어야 출력이 1이 됨.

바이트 연산

컴퓨터가 실제로 바이트 단위의 작업을 수행하기 위해 하는 모든 일

1. 하나의 레지스터에서 다른 레지스터로 바이트를 이동할 때 바이트 안에 들어있는 내용물, 즉 '데이터'를 바꿀 수 있는 세 가지 연산,

2. 바이트 데이터를 2개 입력해서 어떤 상호 작용을 거친 후 새로운 바이트를 출력할 수 있는 네 가지 연산.

비트 시프트 장치

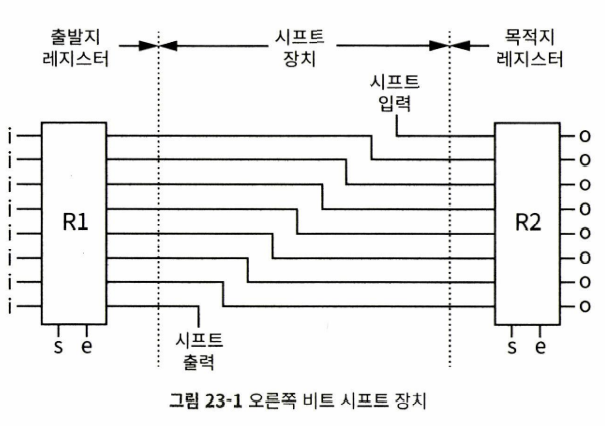

그림 23-1은 레지스터 2개를 연결해서 만든 오른쪽 비트 시프트 장치의 구조를 보여줌.

입력 비트 8개를 의미하는 i 라인은 아래에서 위로 갈수록 상위 비트를 나타냄. 오른쪽 비트 시프트 장치를 만들려면 R1의 모든 출력 비트를 각각 1비트 내려서 R2의 입력에 연결.

R1에 있는 출력 제어 비트 e가 1이 되고, R2에 있는 입력 제어 비트 s가 1이 되었다가 바로 0이 됨. 전체적으로 오른쪽으로 한 자리씩 상위 비트로 밀려서 복사됨.

0100 0010 -> 0010 0001

R1의 '시프트 출력'이 R2의 '시프트 입력'과 연결되어 있다면, 오른쪽 비트 시프트 장치는 0001 1001 입력 1000 1100을 출력

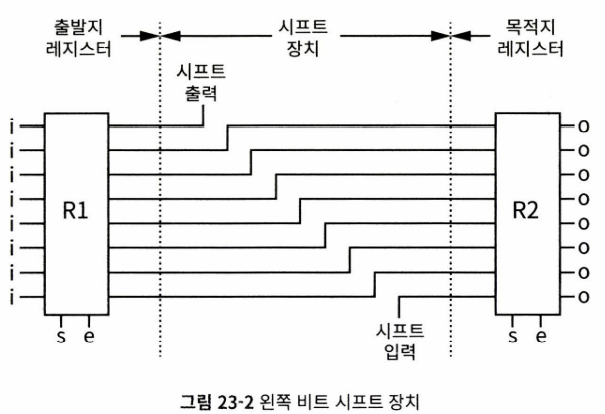

왼쪽 비트 시프트 장치가 R1에서 0100 0010을 입력받으면 R2에 1000 0100을 출력

왼쪽 비트 시프트 장치를 만들려면 R1의 모든 출력 비트를 각각 1비트 올려서 R2의 입력에 연결

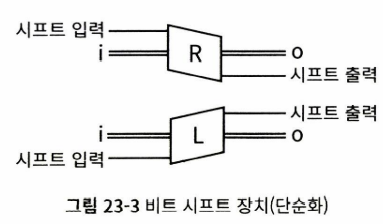

'R'은 오른쪽 비트 시프트 장치, 'L'은 왼쪽 비트 시프트 장치

사용

0000 0110 (6)을 왼쪽 방향 비트 시프트 장치에 입력한 후 결과를 R2로 출력하면 R2에는 이진수 코드 0000 1100 (12)이 저장된다. 2를 곱하는 연산을 한 것.

비트 시프트는 컴퓨터가 곱셈 연산을 수행하는 토대.

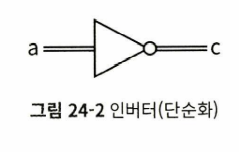

인버터(Inverter)

레지스터 2개 사이에 NOT 게이트 8개를 끼워서 연결한 장치.

앞쪽 레지스터에서 오는 a 바이트 안의 비트는 각각 반전되어 c로 출력.

NOT 게이트 장치는 다른 말로 '인버터'라고 부름.

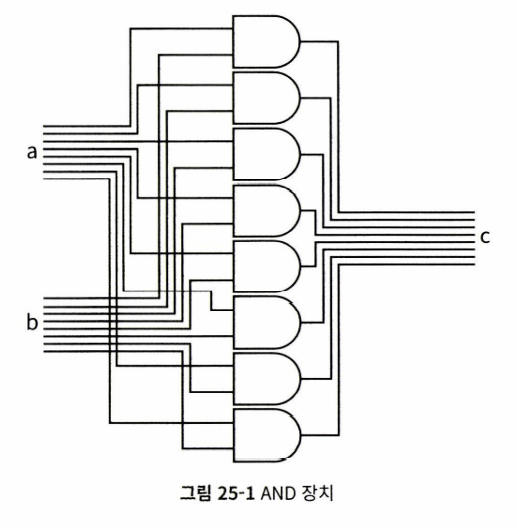

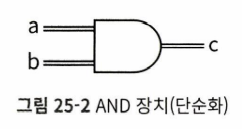

AND 장치

바이트 단위로 된 입력 2개를 받아 개별적으로 AND 연산 8개를 수행한 후에 그 결과를 바이트 단위로 묶어 출력. 결론적으로 바이트 2개를 AND 연산하여 세 번째 바이트를 만들어 내는 장치.

사용

-

아스키 문자 코드를 대문자로 변환할 때 사용.

R0 안에 알파벳 'e'를 나타내는 코드 0110 01010 들어 있고, 대문자 'E'를 나타내는 비트 패턴 0100 0101을 R1에 집어 넣은 후, R1과 R0를 AND 장치에 입력하여 출력을 다시 R0에 복사하고자 함. 그 결과는 두 번째 입력인 대문자 'E' 코드에서 세 번째 비트가 0이므로 첫 번째 입력인 소문자 'e'에서 세 번째 비트가 0이든 1이든 상관없이 AND를 취하면 세 번째 비트는 무조건 0이 됨.0110 0101 -> e

0100 0101 -> E

=======

0100 0101 -> E아스키코드의 모든 알파벳 대문자와 소문자는 세 번째 비드의 부호만 다르게 구성됨. 따라서 AND 장치를 이용하면 모든 알파벳 문자를 쉽게 대문자로 변환할 수 있다.

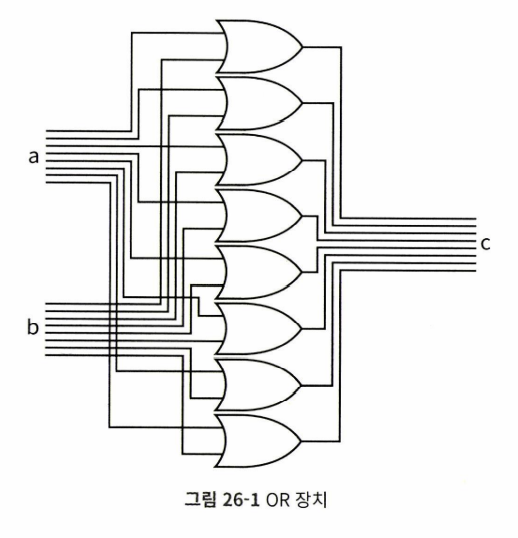

OR 장치

OR 장치는 바이트 단위로 된 입력 2개를 개별적으로 OR 연산 8개를 수행한 후에 그 결과를 바이트 단위로 묶어 출력. 결론적으로 바이트 2개를 OR 연산하여 세 번째 바이트를 만들어 내는 장치

사용

-

알파벳 대문자를 소문자로 변환할 때 사용.

R0 안에 알파벳 대문자 E를 나타내는 코드 0100 0101이 들어있고, 이 글자를 소문자로 만들고 싶다면 0010 0000이라는 비트 패턴을 R1 레지스터에 넣고 R0와 R1을 OR 연산한 뒤에 출력 결과를 다시 R0에 넣어주면 된다.0100 0101 -> E

0010 0000

=======

0110 0101 -> e아스키 코드의 알파벳 대문자와 소문자가 세 번째 비트의 부호만 다르게 설계되어 있기 때문에 OR 장치를 이용하면 쉽게 알파벳 대문자를 소문자로 변환할 수 있다.

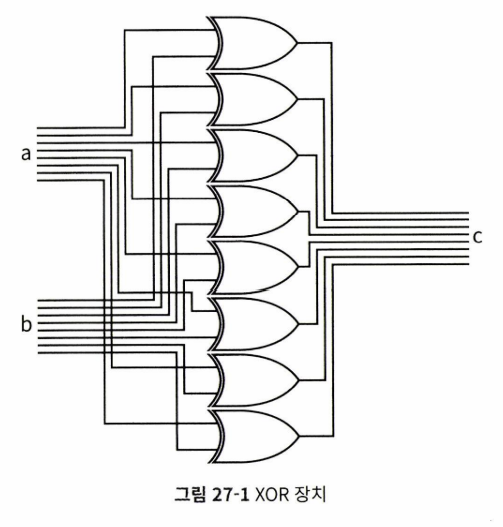

XOR 장치

XOR 장치는 바이트 단위로 된 입력 2개를 받아 개별적으로 XOR 연산 8개를 수행한 후에 그 결과를 바이트 단위로 묶어 출력. 결론적으로 바이트 2개를 XOR 연산하여 세 번째 바이트를 만들어 내는 장치

사용

- R1과 R2가 같은지 비교할 때 사용.

R1과 R2를 XOR 장치에 넣고 출력 결과를 R1에 다시 넣어 확인하면 된다. R1과 R2에 같은 비트 패턴이 들어 있다면 R1에 들어 있는 비트 패턴이 무엇이든 XOR한 결과는 항상 0.