01. 플립플롭(flip-flop)

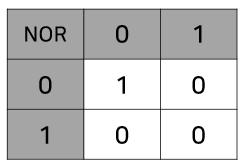

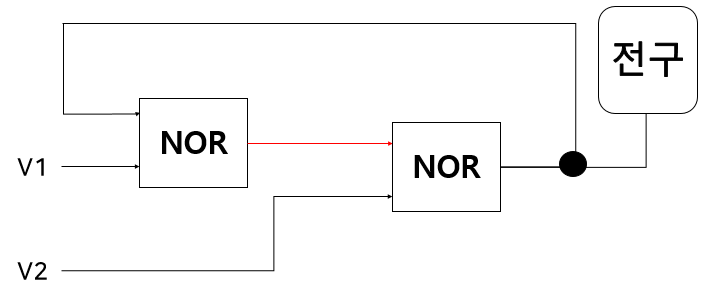

- 데이터를 저장하는 조합논리회로

- NOR Gate 2개를 조합하여 만들 수 있음

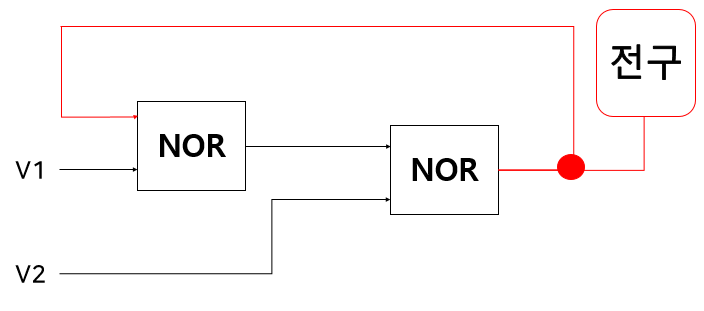

- 처음 상태에서 V1 스위치를 키면 전구가 커진다.

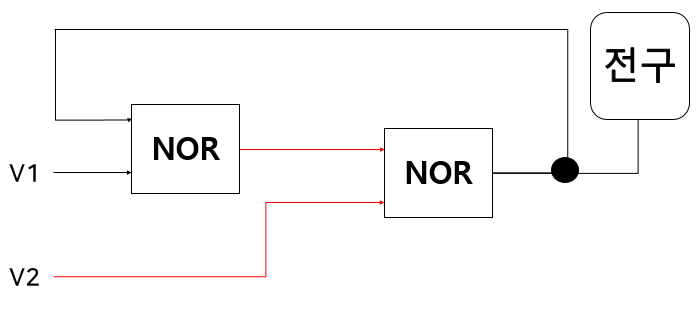

- 이 상태에서 다시 V1 스위치를 꺼도 전구는 꺼지지 않고 켜져 있다.

- 첫 번째 스위치를 한 번이라도 눌렀을 지 판단하는 것은 출력을 통해 알 수 있다.

(= 최근에 V1 스위치가 켜졌었다.) - 이것은 바로 저장한다는 의미로 데이터를 저장할 수 있는 기능임을 의미한다.

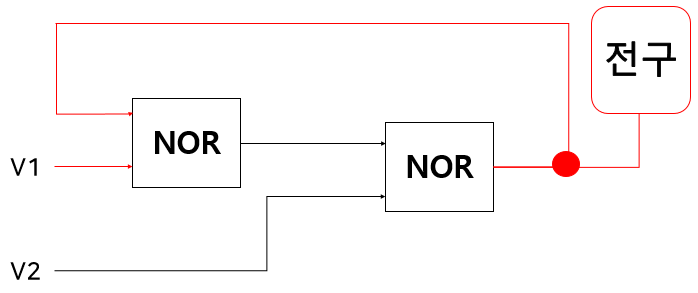

처음 상태

V1 스위치를 켰을 경우

V1 스위치를 껐을 경우

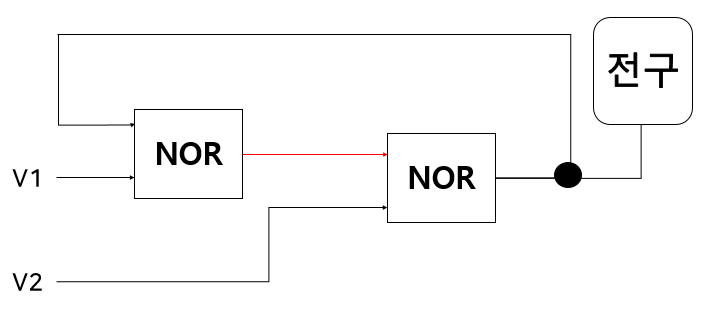

- V1 스위치를 켰다가 끈 상태에서 V2 스위치를 키면 전구가 꺼진다.

- 이 상태에서 다시 V2 스위치를 꺼도 전구는 그대로 꺼져있다.

- 최근에 V2 스위치가 꺼졌었다.

- 이것은 바로 삭제한다는 의미로 데이터를 삭제할 수 있는 기능임을 의미한다.

V2 스위치를 켰을 경우

V2 스위치를 껐을 경우

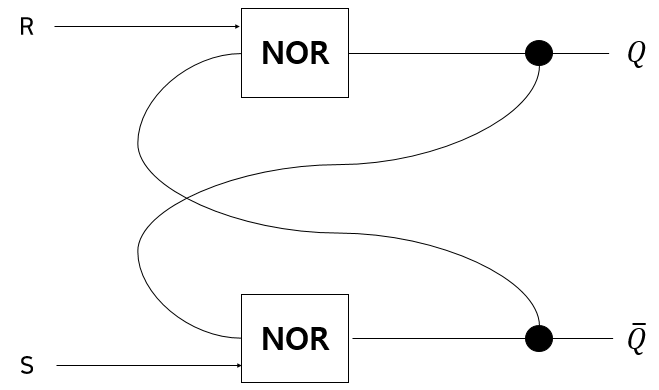

02. RS 플립플롭(Reset-Set filp-flop)

- R와 S 둘 다 1인 상태가 되지 못하도록 하는 것이 일반적이다.

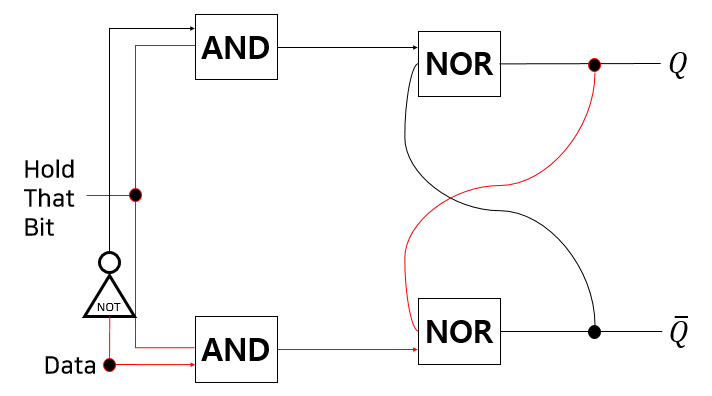

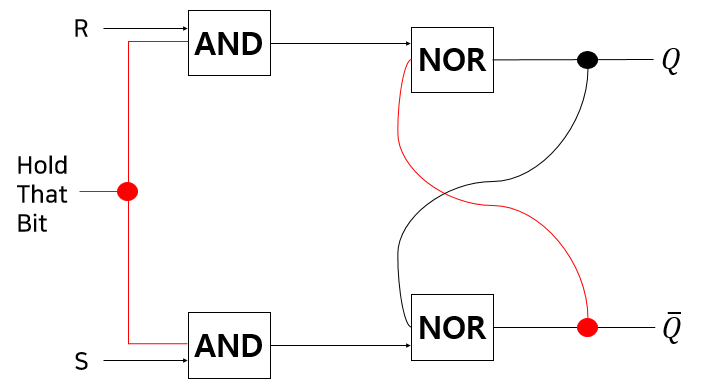

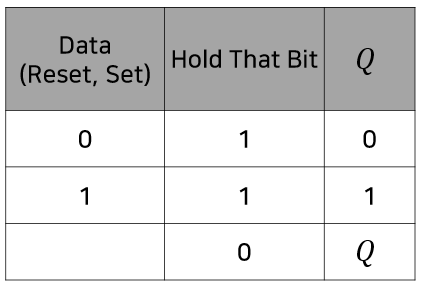

03. Level-triggered flip-flop

-

= RS flip-flop + Hold That Bit

-

Hold That Bit의 역할

- Hold That Bit가 1이 아니면 set이 1이든, reset이 1이든 또는 set이 0이든, reset이 0이든 상관없이 1로 넘어갈 수가 없다.

(= Hold That Bit가 1일 경우만 Data가 1일 때 출력값에 적용이 된다.)

- Hold That Bit가 1이 아니면 set이 1이든, reset이 1이든 또는 set이 0이든, reset이 0이든 상관없이 1로 넘어갈 수가 없다.

-

Hold That Bit를 기본적으로 클럭이라고 생각

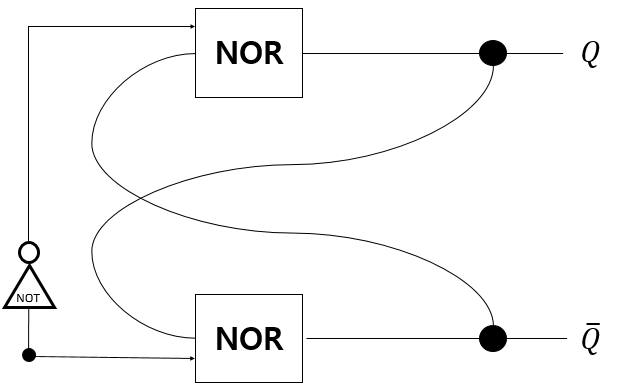

04. D-type flip-flop

- Level-triggered flip-flop에서 input이 Reset, Set으로 2개인 것을 알 수 있다.

- D-type flip-flop을 input(Set)을 하나로 바꾸고 NOT Gate를 붙여 Reset으로 연결해주어 Reset, Set 둘 다 1이 되는 경우를 방지

- Reset, Set 둘 다 0이 되는 경우도 없으므로 생각하지 않아도 된다.

05. Level-triggered D-type flip-flop

- D-type flip-flop에서 Hold That Bit까지 표현한 경우이다.

- Level-triggered는 Hold That Bit가 1일 때만 Data 값을 저장한다는 의미

- Reset, Set 둘 다 1과 0일 경우를 피하도록 설계한 조합논리회로

- 이와 같은 논리회로를 기반으로 메모리가 구성