소재,소자

반도체 정의를 설명하고, 개인적 견해를 이야기 해보시오.

- 반도체는 원래 부도체이나, 외부에서 불순물 주입 등을 통해 도체로 되는 성질을 가진 물질입니다.

- 반도체의 종류로는 순수한 진성반도체가 있고, 여기에 3족 원소를 주입해서 정공의 Carrier를 가진 p형 돈체와 5족 원소를 주입해서 자유전자의 carrier를 가진 N형 반도체가 있습니다.

- 1947년 벨연구소에서 처음으로 진공관 트랜지스터를 대신할 수 있는 반도체 트랜지스터가 만들어 졌는데, 이는 새로운 전자 문명의 신세계를 여는 계기가 되었습니다.

- 트랜지스터 기술의 발전은 전자 기기의 소형화, 고성능화, 저전력화를 가능하게 했습니다.

에너지 밴드를 설명하시오.

- 에너지 밴드는 원자 내 전자들이 가질 수 있는 고유한 에너지 분포를 의미합니다. 이는 전자들이 전기 전도에 참여할 수 있는 능력을 결정합니다.

- 크게 valence band, forbidden band, conduction band, 페르미 준위가 있습니다.

- valence band는 최외각 전자에 의해 채워진 에너지 밴드로, 절대 0도에서 전자가 정상적으로 존재하는 가장 높은 전자 에너지 밴드입니다.

- forbidden band는 valence band와 conduction band 사이의 영역이며 전자가 존재할 수 없는 영역이며 흔히 bandgap이라고 부릅니다.

- 전자가 외부 에너지를 받아서 valence band에서 bandgap을 뛰어 넘어 conduction band에 오르면 자유롭게 움직일 수 있어 전도성을 갖게 됩니다.

- 페르미 준위는 전자의 존재 확률이 50%인 에너지 준위

도체/반도체/부도체의 차이을 에너지 밴드를 이용하여 설명할 수 있다

- 부도체는 valence band와 conduction band 사이의 에너지 밴드갭이 매우 커 전자의 이동이 어렵습니다. 따라서 전기 전도성이 매우 낮습니다.

- 진성 반도체는 conduction band와 valence band의 bandgap이 크지 않아 외부 에너지에 의해 전자가 이동할 수 있습니다.

- 도체는 전도대와 가전자대가 겹쳐 있어 전자가 자유롭게 움직일 수 있으므로 전기전도성이 높습니다.

silicon을 진성반도체로 가장 많이 사용하는 이유를 설명하시오.

silicon은 bandgap이 1.1eV 수준으로 낮아 불순물의 주입으로 쉽게 N형, P형 반도체가 될 수 있으며, 주위에서 쉽게 구할 수 있는 소재라 원가 비용 측명에서도 유리하기 때문에 많이 사용되고 있습니다.

단결정과 다결정 silicon 차이를 설명하시오.

- 단결정은 결정방향이 하나의 동일한 구조이고, 다결정은 여러 단결정들이 뭉쳐진 것입니다.

- 단결정 실리콘은 전자 이동이 자유롭고 균일한 특성을 가지고 있어 반도체 소자의 기판 재료로 주로 사용됩니다. 예를 들어 MOSFET의 소스, 드레인 영역에 사용됩니다.

- 다결정 실리콘은 MOSFET GATE 전극으로 사용되고 있습니다.

Wafer 제조 과정을 설명하시오.

1) 석영을 funace에 녹여 액체의 비정질 상태로 만들고

2) 단결정 seed crystal을 넣어 회전을 하면서 서서히 끌어 올리면, seed crystal과 동일한 결정구조의 단결정 silicon 원통괴가 생성됨(잉곳)

3) 잉곳을 얇게 자르고, 연마하고, 세정함

Wafer가 둥근 이유를 설명하시오.

1) 잉곳 자체가 둥굼

2) 반도체 공정은 회전 원심력을 이용하는 공정들이 많아 물리적인 stree 측면에서 둥근 구조가 제일 이상적

3) 비록 Die가 사각형이라 wafer의 edge 부위에서 버려지는 die가 많지만,

4) 공정 후 균일도 측면에서 유리함

점점 더 큰 size wafer를 사용하는 장단점을 설명하시오.

- 공정기술이 발전하면서

- layer 수 증가

- FAB Step 수 증가

- TAT가 길어짐

- FAB 생산성 감소

- 따라서 큰 Size의 wafer를 이용하면 생산성을 향상할 수 있어 원가 측면에서 유리

- 다만 Size가 커지면 기존 공정 대비 공정의 균일도가 나빠지거나 공정 stress 측면 불리할 수 있음

유전율의 정의를 설명하시오.

- 유전율은 전기장 내 물질이 전하를 저장할 수 있는 능력

- 절연체는 외부에 전계를 인가하더라도 전류가 통하지 않으나 내부 쌍극자의 분극현상을 유발합니다.

- 외부 전계에 의한 쌍극자의 극성이 반응하는 현상을 분극현상이라 하며, 그 크기를 유전율이라고 함

- 유전율이 클수록 절연체 내부에서 쌍극자의 분극현상이 잘 일어난다는 의미이며, 반대편으로 전계를 잘 전달할 수 있다는 의미

P형 반도체와 N형 반도체를 설명하시오.

- N형 반도체: 진성 반도체에 5족 원소를 주입하면, 주입된 5족 원소가 silicon 원소의 자리를 차지하여 최외각 전자와 공유 결합 후 1개의 전자(자유전자)가 남게 됩니다. 이런 불순물의 주입은 conduction band 가까이 5족 원소에 의해 도너 레벨이 만들어지고 쉽게 전자를 conduction band로 이동할 수 있게 되어 전류가 흐릅니다.

- p형 반도체: 진성 반도체에 3족 원소를 주입하면, 3족 원소가 silicon 원소의 자리를 차지하여 최외곽 전자를 공유결합 하더라도 1개의 자리가 비게 되는데, 이를 hole이라고 합니다. valence band 가까이 어셉터 레벨이 만들어지고, 쉽게 valence band에서 전자를 acceptor 레벨로 이동할 수 있게 되어 전류가 흐릅니다.

pn 접합

- p형 반도체와 n형 반도체를 접합시켜 만든 구조

- 서로 접합시키면 양공과 전자가 서로 결합하여 소멸되는 확산 현상이 일어남=>

difussion current - 이 과정에서 p형과 n형 경계면 근처에 carrier가

없는 depletion region이 형성됨 - depletion region에는 donor와 acceptor들의원자핵이 만드는 fixed charge만 남고, 결과적으로 "built-in E-field가 형성됨

- 이에 의해 전자나 hole이 끌려가게 되어 흐르는 전류를

drift current라고 함 - 이는 전자의 확산을 방지하고 전류의 흐름을 제어

- 이에 의해 전자나 hole이 끌려가게 되어 흐르는 전류를

- Forward Bias: p-type에 (+)전계가 인가되면 에너지밴드가 아래쪽으로 내려갑니다. 가해준 bias 만큼 페르미 레벨이 이동하여 n-type 쪽 전자들이 쉽게 p-type쪽으로 건너갈 수 있게 되며, p-type쪽 hole도 마찬가지이므로 전류가 흐릅니다.

- Reverse Bias: p-type에 (-)전계가 인가되면 커진 에너지 장벽때문에 전류가 잘 흐르지 못하게 되고, depletion region이 점점 팽창합니다.

pn 접합의 junction breakdown

Zener Breakdown

큰 도핑 농도를 가지는 pn juction에서 큰 reverse bias를 인가했을 때, 터널링 현상에 의해 급격한 전류의 흐름이 발생하는 것

- pn junction이 매우 높은 농도로 도핑되었을 때 발생하는 메커니즘

- 농도가 클수록 매우 큰 built-in potential 형성됨

- reverse bias를 인가하면 depletion region에 매우 심하게 휘어진 에너지 밴드가 형성됨

- 심하게 휘어지면서 에너지 장벽의 두께가 매우 얇아지고, p type의 전자가 터널링을 통해 쉽게 건너가게 됨

avalanche effect

- 전자가 확산에 의해 depetion rejion으로 끌려들어오면 내부의 강한 E-field에 의해 전자가 매우 빠른 속도를 가지게 되고, 결과적으로 큰 운동에너지를 가진 전자가 됨

- 가속된 전자가 다른 원자핵과 전자 사이의 결합을 끊어 버림

- 많은 전자-홀 쌍이 생기고 전류가 흐름

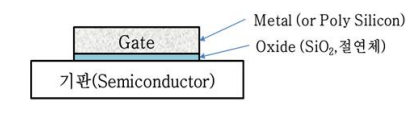

MOS의 개념을 설명하시오.

- Metal Oxide Semiconductor

- 두개의 전극을 가지는 구조

- silicon 기판 위에 절연체인 산화막과 gate 전극을 쌓은 구조

- gate 전극에 전압을 걸면 silicon 내부 상태를 변화시켜 절연 산화막 내부의 분극현상으로 산화박 하부에 캐리어를 모을 수 있음

- 이런 전기적 특성을 이용해 수동소자인 capacitor로 만들거나 능동소자인 transistor를 동작시키는 채널을 만들 수 있음

MOS CAP의 동작원리를 설명하시오.

- Accumulation: Gate 전극에 P기판 전압보다 낮은 전계를 인가하면, 전극 하단에 hole들이 모이게 됨

- Depletion : Gate 전극에 P기판보다 약간 높은 전계를 인가하게 되면 전극 하단의 hole들이 밀려나게 됨

- Inversion: Gate 전극에 P기판보다 훨씬 높은 전계를 인가하게 되면 전극 하단에는 소수 캐리어인 electron이 모이게 되는데, 이때 p 기판과 반대되는 -극성의 층이 생성되며, 이를 Inversion layer이라고 함

MOSFET의 동작 원리를 설명하시오.

- Gate 전압을 통해 source와 drain 사이 흐르는 drain current를 조절하는 장치

- High ON current, Low OFF current

- DRAIN 전압에 의한 채널 포텐셜의 분포

- cut-off 영역 : Drain 전압과 무관하게 gate 전압이 threshold 전압 이하일 경우 채널 inversion이 형성되지 않아 전류가 흐르지 않는 상태

- linear 영역 : Gate 전압을 threshold 전압 이상으로 증가시키면 채널 inversion 영역이 형성되어 Drain 전압에 비례하여 drain 전류가 증가하는 상태

- Pinch-off : linear 영역에서 Drain 전압을 더 증가시키게 되면 Drain영역에서 Depletion 영역이 늘어나 점점 channel inversion 영역을 밀어냅니다. 채널 inversion 영역이 Drain과 분리되는 시점 (VG-VD=VT)

- Saturation : inversion영역이 Drain과 끊어진 이후 drain 전압이 증가해도 drain 전류는 일정하게 유지되는 상태

- depletion 영역의 전기장에 의해 전류가 흐를 수 있음

- 전자의 양은 gate 전극에 의해 결정되기 때문에 drain current가 늘어나지는 않음

NMOS PMOS

NMOS

- N형 반도체 채널을 이용

- 게이트 전압이 일정 수준 이상이면, N형 채널이 형성됩고 전자들이 소스에서 드레인으로 이동

- NMOS는 전기를 더 잘 전달하기 때문에 PMOS보다 빠르게 동작

PMOS

- P형 반도체 채널을 이용

- 게이트 전압이 일정 수준 이하로 떨어지면, P형 채널이 형성되고 정공들이 소스에서 드레인으로 이동

- NMOS에 비해 오프 상태에서의 누설 전류가 낮아 전력 소비가 적은 장점

MOSFET의 Vth를 설명하시오.

- MOSCAP에서 반전층이 생기는 시점에 GATE에 인가한 전압의 크기

- 소스와 드레인간 연결되어 동작하기 위하 최소한의 Turn On 전압

- MOS Capacitor의 Capacitance과 반비례하고, 기판의 농도에 비례

- 반전층 채널을 만들기 방해하는 기판의 원래 캐리어 농도가 낮을수록 문턱전압이 낮아짐

- capacitance가 크면 더 작은 Gate 전압으로도 채널을 형성할 수 있는 충분한 전하를 끝어들일 수 있기 때문에 문턱전압은 낮아짐

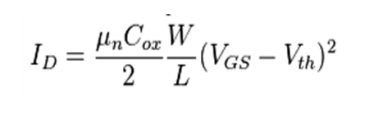

MOSFET의 Saturation 전류에 대해 설명하시오.

- saturation 상태에 있다고 할 때, source와 drain 사이에 흐르는 전류

MOSFET의 누설전류 loff를 설명하시오.

- Cut-off 상태의 leakage를 의미

- gate 전압인 문턱전압보다 낮아 channel inversion이 없음에도 불구하고 발생하는 leakage를 의미

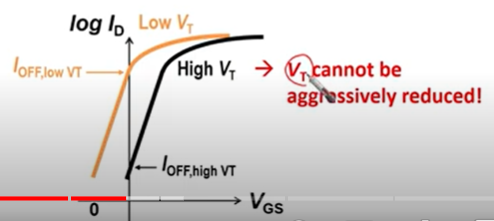

문턱전압 Trade-off

- 문턱전압을 낮추면 on current를 높일 수 있음

- 문턱전압을 낮추면 off current 또한 높아짐

- weak inversion에서 전류의 기울기를 급격하게 만들자!

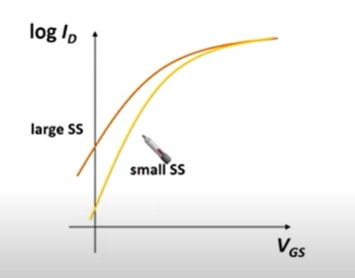

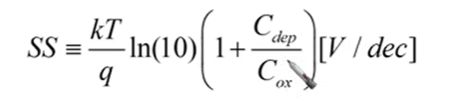

Sub-threshold slope와 swing에 대해 설명하시오.

문턱전압 이하에서도 채널이 완전히 꺼지지 않고, 약간의 전하 캐리어(전자 혹은 정공)가 존재할 수 있습니다. 이 캐리어들이 이동하면서 미량의 전류가 흐르는 것을 subthreshold leakage라고 합니다.

- subthreshold slope: subthreshold 영역에서 leakage 발생 정도를 표시

- Subthreshold swing: drain current를 10배 변화시키는데 필요한 gate voltage의 양

- ss값이 작을수록 mosfet의 성능이 좋음

- mV/decade 단위

minimize SS

- oxide 두께가 커지면 Cox 작아지면서 ss커짐 -> 따라서 두께가 작을수록 유전율이 높을수록 좋음

- 기판의 도핑농도가 증가하면 Cdep이 증가하여 ss커짐-> 따라서 도핑농도가 적을수록 좋음

트랜지스터의 동작 speed 성능을 높이는 방법을 설명하시오.

- TR의 speed가 빠르다는 것은 TR on/off가 빠르다는 의미

- carrier의 이동하는 거리가 짧을수록 on 동작이 빨라지기 때문에 채널 length가 짧으면 발라짐

- carrier의 이동속도를 빠르게 하면 speed가 빨라짐

- 소스 드레인 간의 전위차가 크면 동작속도를 높일 수 있기 때문에 CMOS 구조에서 동작전압을 증가하면 SPEED 좋아짐

- 그러나 이는 전력소모 측면에서 부적합

트랜지스터의 Vth를 제어하는 공정 방법을 설명하시오.

- 문턱전압은 capacitance와 반비례하고 기판의 농도에 비례

- capacitor의 capacitance와 관련되 oxide의 유전율과 그 두께를 변경하면 됩니다.

- 기판 농도를 조절하기에 불순물 이온을 주입하는 공정이 적용되고 있음

트랜지스터의 Vth를 낮추기 위해 capacitance를 높이는 방법을 설명하시오.

- 유전체의 면적을 넓힘

- 집적도가 낮아지기 때문에 바람직하지 않음

- 유전체의 두께를 줄임

- 유전상수가 높은 물질의 유전체를 사용

문턱전압을 낮추면 낮은 gate 전극의 전압에서도 채널의 반전층이 쉽게 발생할 수 있어 낮은 동작 전압을 구현할 수 있습니다.

트랜지스터 파라미터들의 온도특성을 설명하시오.

온도가 올라가면

- 진성 캐리어 농도의 증가에 의해 문턱전압이 낮아집니다

- 누설 전류는 증가합니다. 누설전류의 주요 원인인 subthreshold leakage는 문턱전압에 반비례하는 물성이기 때문입니다.

- 포화 전류는 최종 감소합니다.

- 초기에는 문턱전압 감소로 전류는 증가하나 온도가 증가하면서 실리콘 격자의 진동과 산란에 의해서 캐리어의 mobility가 떨어지고 on 저항이 커지기 때문에 전류가 감소

Short Channel Effect

channel length를 줄이면 캐리어가 이동해야 할 거리인 source와 drain 간의 채널거리가 짧아지므로, on/off동작을 빠르게 수행할 수 있음

그러나 여러 부작용이 수반됨

부작용은 tox를 줄여 cox를 키우는 것이 효과적임

채널을 줄이는 이유

- device의 speed를 높이기 위해서

- device의 dense를 높여서 칩의 단가를 높이기 위해서

Channel Length Modulation

- saturation Mode에서 drain 전압이 증가해도 saturation 전류는 일정하다라고 하지만 사실 조금씩 증가함

- drain 전압이 증가함에 따라 점점 inversion의 길이가 짧아지기 때문에 lengh에 반비례하는 drain 전류는 조금씩 증가함

- 채널 길이가 짧을수록 channel length modulation이 더 크게 나타남

Drain Induced Barrier Lowering(DIBL)

- Drain 전압에 의해 채널의 원치 않는 에너지 장벽의 낮아짐이 발생하면서 누설 전류처럼 전류가 발생하는 현상

- dibl 값이 작을수록 MOSFET 성능이 좋음

- GATE 전압으로 전류를 조절할 수 없음

GIDL (Gate-Induced Drain Leakage)

- OFF상태에서 Drain current가 발생하는 현상

- gate와 drain이 사이 중복되는 지역 발생

- drain 전압이 크고 gate 전압이 낮다면 depletion region에서 에너지 밴드의 휘어짐이 심해져 band to band tunneling이 발생하여 전류가 흐름

- lightly doped drain(LDD)를 통해 완화 가능

- long &short channel에서 둘 다 발생

vth roll off

- gate length가 짧아질수록 Vth가 감소하는 현상

- drain 전압이 커져서 채널의 일부분을 켜기 때문

- vth roll off가 커질수록 SCE 심해짐

hot carrier effect

hot carrier:channel을 따라서 흐르던 전자가 drain 근처의 강한 전기장에 의해 큰 에너지를 얻게 되고, 일부는 silicon과 충동하면서 전자-홀쌍을 만듬- electric field 값을 줄이기 위해 lightly doped drain(LDD), spacer(gate옆 날개처럼 달린 산화막) 사용

punchthrough

- 채널 길이가 짧아지면 Source 쪽의 depletion region이 drain쪽의 region과 만나게 되는 현상이 발생

- 이를 통해 누설 전류가 발생하는 현상

- 도핑농도를 증가시키면 depletion region을 줄일 수 있음

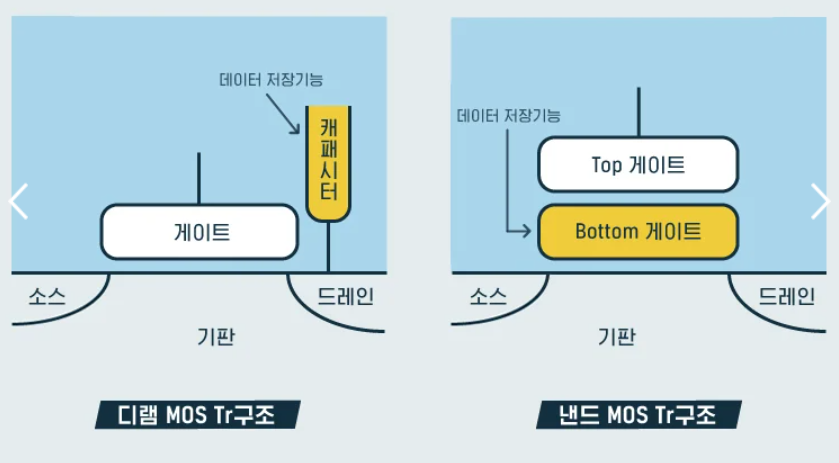

DRAM vs NAND

DRAM(Dynamic Random Access Memory)

- 구조 : 스위칭 역할을 하는 Tr 1개와 Tr 밖에 별도로 데이터를 저장하는 캐패시터 1개

- 저장 방식:각 비트를 하나의 트랜지스터와 하나의 캐패시터를 사용하여 저장합니다. 캐패시터가 충전되어 있으면 1, 방전되어 있으면 0을 나타냄

- 속도: DRAM은 빠른 읽기/쓰기 속도

- 휘발성: DRAM은 전력 공급이 끊기면 저장된 데이터가 사라지는 휘발성 메모리

NAND Flash 메모리

- 구조: 스위칭 역할을 하는 트랜지스터 속에 데이터 저장 기능을 갖는 플로팅 게이트를 같이 내포

- 저장 방식: NAND Flash는 플로팅 게이트(Floating Gate)를 사용하여 데이터를 저장합니다. 여러 개의 셀이 연속적으로 연결되어 있으며, 각 셀은 1 비트 이상을 저장할 수 있음

- 속도: DRAM보다 느림

- 비휘발성: 전력이 공급되지 않아도 데이터를 유지할 수 있어 휴대전화, SSD, USB 메모리 등의 저장 장치에 주로 사용됨

MOSFET의 개요

Planar MOSFET

DIBL, punchthrough와 같은 off current가 발생