지난 학기 디지털 시스템 설계 과목에서 Vivado 를 통해 Verilog 코드를 작성하고 RISC-V 를 통해 RTL systhesis 와 FPGA 로 boarding 하는 것 까지 배울 수 있었다.

이제 한 학기가 끝나서 라이센스와 보드 모두 반납. 여름방학 동안 내가 할 수 있는게 뭐가 있을까 생각하다가 우선 Verilog 코딩 복습부터 해보기로 결심하였다. 우선 나는 이전에 homebrew 로 설치한 gtkwave 와 VSCode 에서 설치한 iverilog 패키지를 활용해 기본적인 로직게이트의 파형을 분석해보겠다.

https://velog.io/@vantaa89/맥에서-Verilog-돌리기

참고로 VSCode 에서 작성하는 코드는 Vivado 코드에서 'dump' 를 위한 코드가 추가되어야하는데, 나는 맥북을 사용하고 있기 때문에 해당 링크의 도움을 받아서 코드를 작성하였다.

- inverter 동작 확인

1. module file 생성

첫 번째로 'inv.v' 라는 이름의 verilog file 을 생성하여 inverter 의 동작을 수행하는 모듈을 생성한다. 작성하는 코드는 다음과 같다.

module inv(a, b);

input a;

output b;

assign b = ~a;

endmodule2. testbench file 생성

해당 코드를 작성하였으면 'inv_tb.v' 라는 이름의 testbench 파일을 생성하여 입력에 시간 정보를 할당시켜준다.

`include "inv.v"

`timescale 1ns/1ps

module inv_tb;

reg t_a;

wire t_b;

inv my_inv(.a(t_a), .b(t_b));

initial

begin

t_a = 1'b0;

#5 t_a = 1'b1;

#5 t_a = 1'b0;

#5 t_a = 1'b1;

#5 t_a = 1'b0;

end

initial begin

$dumpfile("inv_tb.vcd");

$dumpvars(0, inv_tb);

end

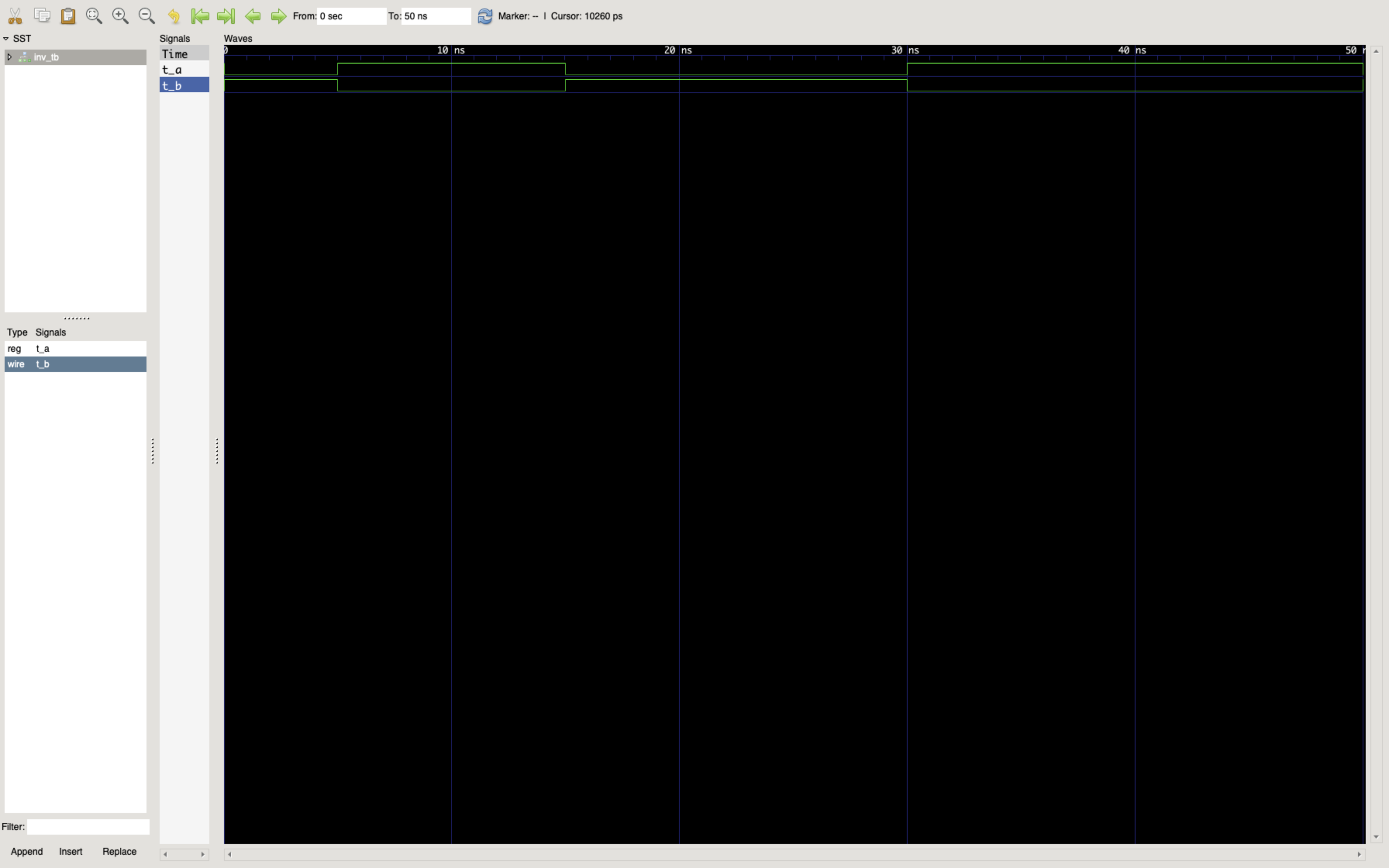

endmodule3. compile 및 파형 확인

두 파일을 저장하고 터미널에서 해당 파일에 대한 컴파일링을 수행한다. 소스파일이 있는 디렉토리에서 다음과 같은 순서대로 커맨드를 입력해준다.

iverilog -o testbench testbench.v

iverilog -y ./module -o testbench testbench.v

vvp testbench -vcd

open -a gtkwave testbench.vcd위의 코드에서 컴파일하고자 하는 testbench source file 에서 사용된 모듈 이름을 testbench 자리에 입력하면 된다. 정상적으로 컴파일이 됐으면 해당 디렉토리에 vcd file 이 생성되고 gtkwave 를 통해 파형이 출력된다.

- 나머지 logic gates 동작 확인

1. module file 생성

logic circuit 에서 사용되는 6가지의 logic gate 를 한번에 담은 모듈을 생성한다. 'all_in_one.v' 라는 이름의 verilog file 을 생성하여 코드를 작성해보았다.

module all_in_one(a, b, yAND,yOR, yNAND, yNOR, yXOR, yXNOR);

input a,b;

output yAND, yNAND, yOR, yNOR, yXOR, yXNOR;

assign yAND = a & b;

assign yNAND = ~(a & b);

assign yOR = a | b;

assign yNOR = (a | b);

assign yXOR = a ^ b;

assign yXNOR = ~(a ^ b);

endmodule2. testbench file 생성

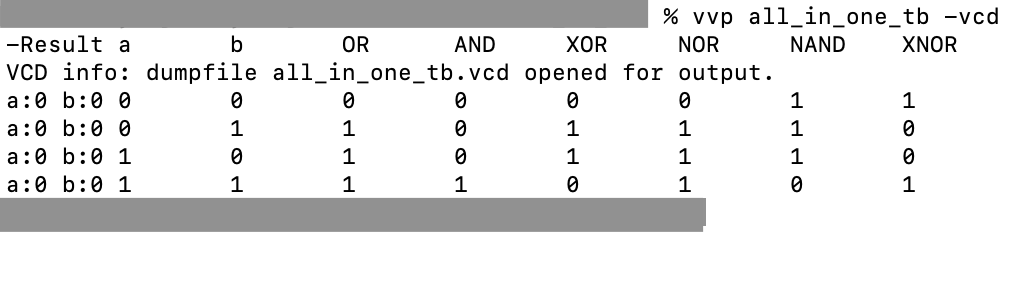

앞서 수행한 과정을 반복해주면 된다. 이때 $display(); 는 생성된 파일을 실행시켰을 때 terminal 에 출력되도록 하는 명령어이다.

`include "all_in_one.v"

`timescale 1ns/1ps

module all_in_one_tb;

reg a, b;

wire yAND, yOR, yNAND, yNOR, yXOR, yXNOR;

all_in_one my_all(a, b, yAND, yOR, yNAND, yNOR, yXOR, yXNOR);

initial begin

$display("-Result\ta\tb\tOR\tAND\tXOR\tNOR\tNAND\tXNOR");

a = 0; b = 0; #50;

$display("a:0 b:0\t%d\t%d\t%d\t%d\t%d\t%d\t%d\t%d",a, b, yOR, yAND, yXOR, yNOR, yNAND, yXNOR);

a = 0; b = 1; #50;

$display("a:0 b:1\t%d\t%d\t%d\t%d\t%d\t%d\t%d\t%d",a, b, yOR, yAND, yXOR, yNOR, yNAND, yXNOR);

a = 1; b = 0; #50;

$display("a:1 b:0\t%d\t%d\t%d\t%d\t%d\t%d\t%d\t%d",a, b, yOR, yAND, yXOR, yNOR, yNAND, yXNOR);

a = 1; b = 1; #50;

$display("a:1 b:1\t%d\t%d\t%d\t%d\t%d\t%d\t%d\t%d",a, b, yOR, yAND, yXOR, yNOR, yNAND, yXNOR);

end

initial begin

$dumpfile("all_in_one_tb.vcd");

$dumpvars(0, all_in_one_tb);

end

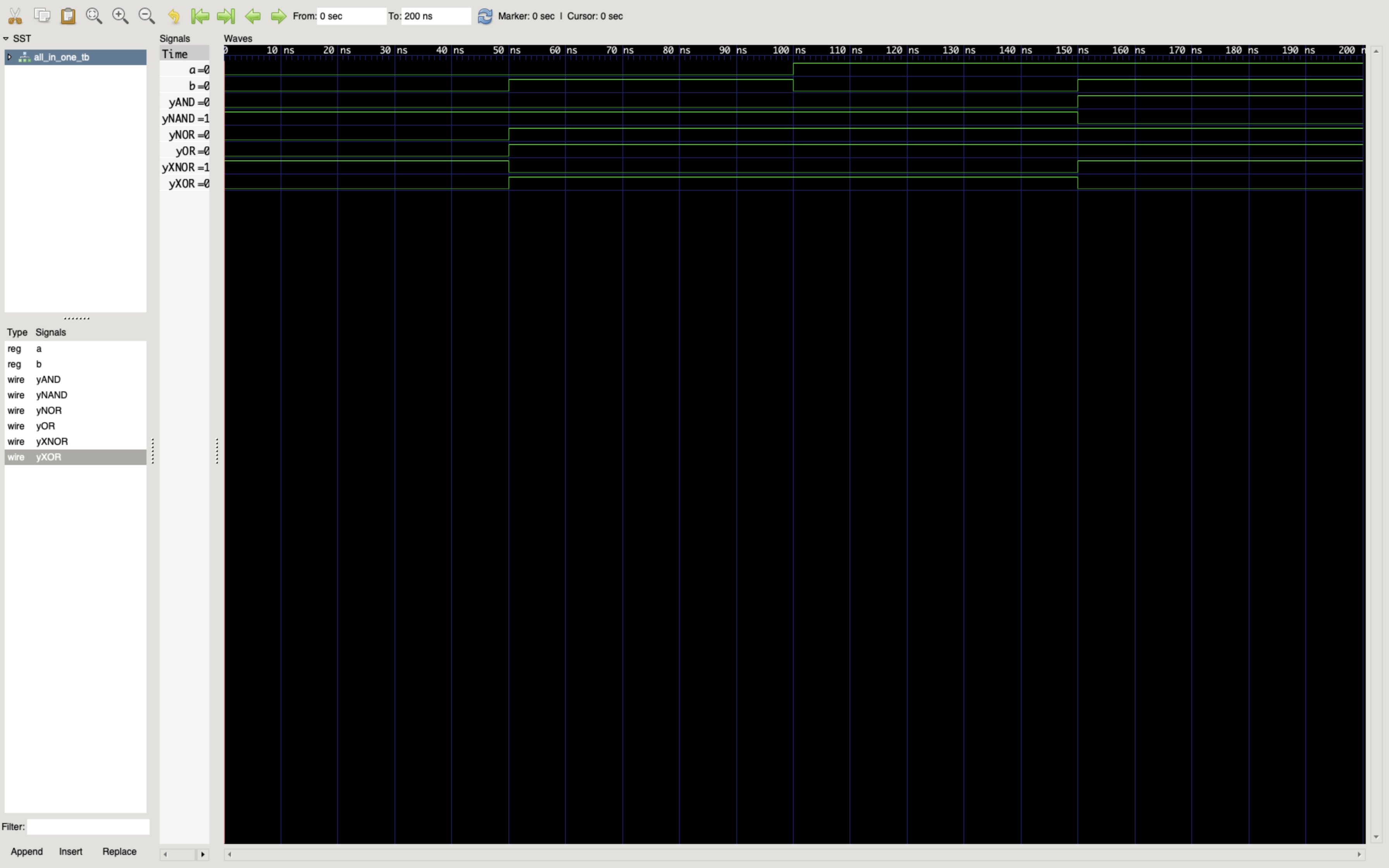

endmodule3. compile 및 파형 확인

앞서 과정과 동일하게 컴파일을 실행하고 파형을 확인해보면 다음과 같이 정상적으로 로직이 구현되는 것을 확인할 수 있다. testbench file 에서 작성된 $display(); 명령어로 인해 terminal 창에서는 아래와 같은 창이 출력된다.

(참고로 a : 0 b : 0 부분 코드는 수정전에 캡쳐해서 문제가 있음. 코드는 수정해서 문제 없음.)

마치며

구글링을 하다가 verilog code 예시들을 모아놓은 링크를 발견했다. 이 부분을 참고해서 이번 여름 방학동안 꾸준히 학습해보려고 한다. To be continued...🫠

안녕하세요! 저도 맥북을 사용하고있는데, gtkwave를 설치하고나서 실행하려니까 update required fof "gtkwave-bin"이라는 문구가 뜨고, 오케이를 누르니까 'gtkwave-bin 응용프로그램이 예기치 않게 종료되었습니다'라는 문구가 뜨면서 열리지가 않네요.. 혹시 뭐때문에 그러는건지 아신다면 알려주실수 있으실까요??ㅠㅠ