MOSFET

동작 특성

-Depletion mode MOSFET

- 전류의 흐름을 제어하는 채널을 미리 만들어 놓고 전류가 흐르는 경로를 줄여 가도록 한 제어 구조

- 즉, VGS = 0일 때 , IDS흐음(D-S간 On) -> default on

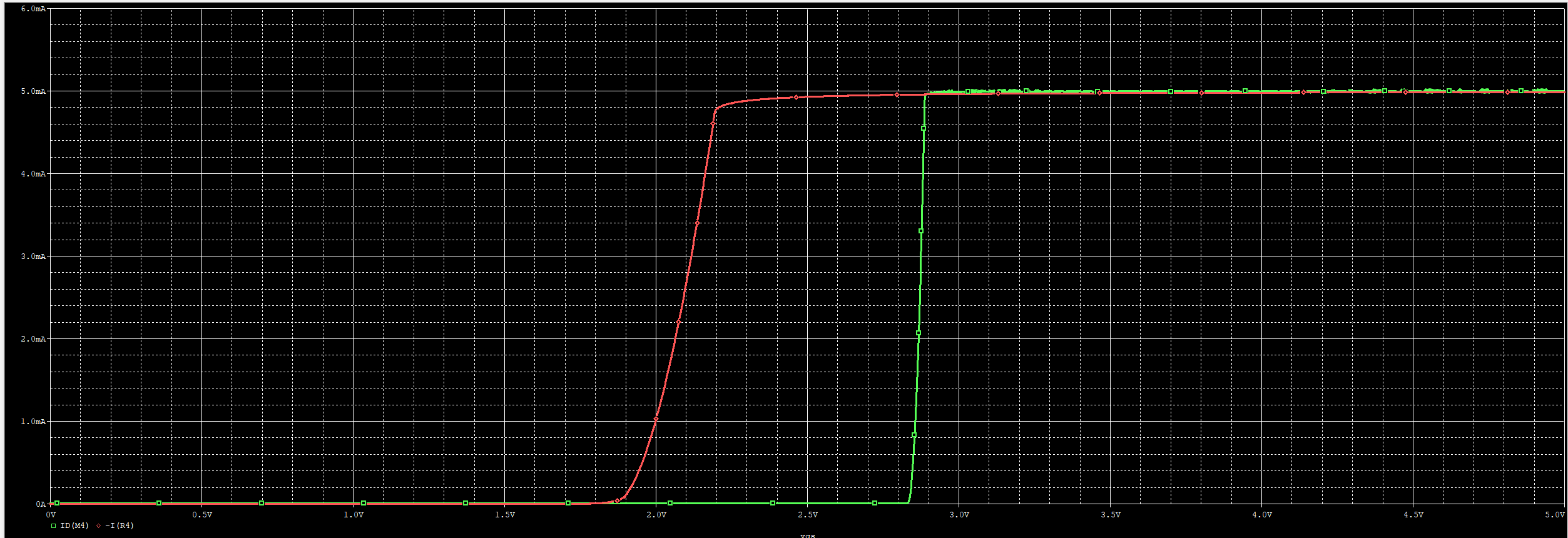

-Enhancement Mode MOSFET :대부분 회로에 적용

- 전류의 흐름을 제어하는 채널을 제어전압(VGC)에 의해 형성해 가는 구조

- 즉, VGS = 0 일 때, IDS = 0(D-S간 off) -> default off

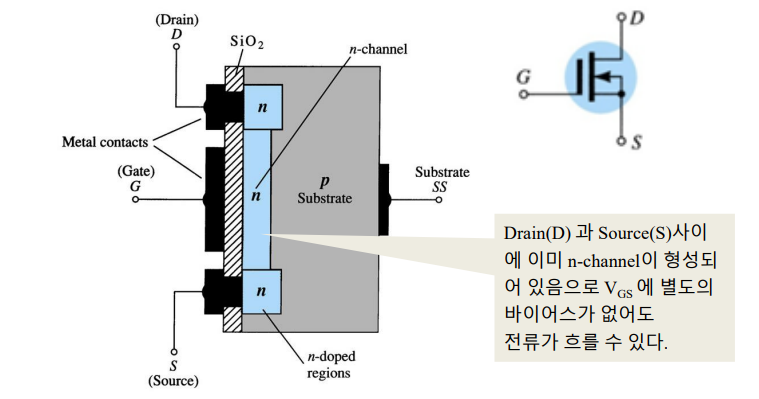

Depletion Mode MOSFET(n-channel)구조

- Drain(D) 과 Source(S) 핀은 n-doped 영역에 연결되어 있으며, 이러한 두 개의 n-doped 영역은 n-channel을 통해 연결 구성됌.

- n-channel 은 SiO2의 얆은 절연물질을 사이에 두고 Gate(G)d와 구성되어있음

- n-channel 물질은 SS(Subraste, Body) 터미널과 연결된

p-doped substrate에 올려져 있는 구조

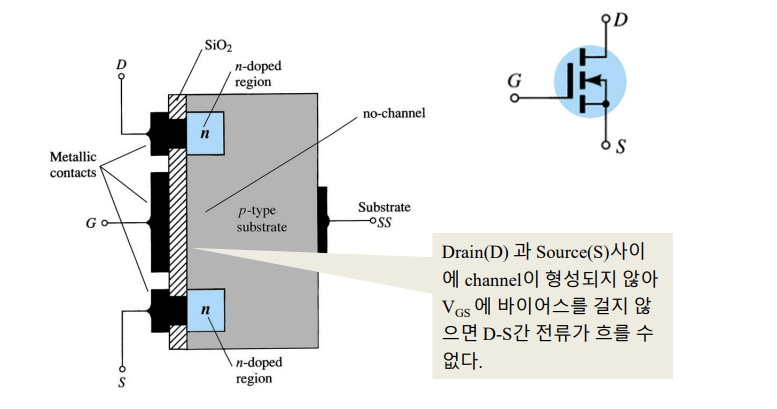

Enhancement Mode MOSFET(n-channel)구조

- D와S핀은 n-doped 영역에 연결되며, 이들 n-doped 영역에 별도의 channel 구성은 없음.

- VGS = 0인 경우 전류가 흐를 수 없다.

- G는 얇은 SiO2 절연층을 거쳐 p-doped substrate에 접해있음

- n-doped 물질은 별도의 SS터미널과 연결된 p-doped substrate에 올려져 있는 구조

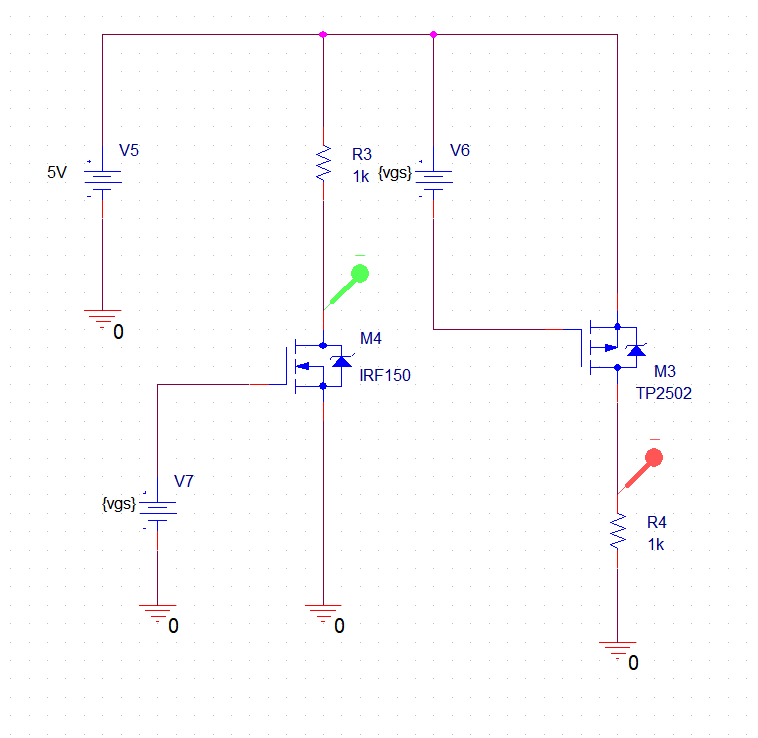

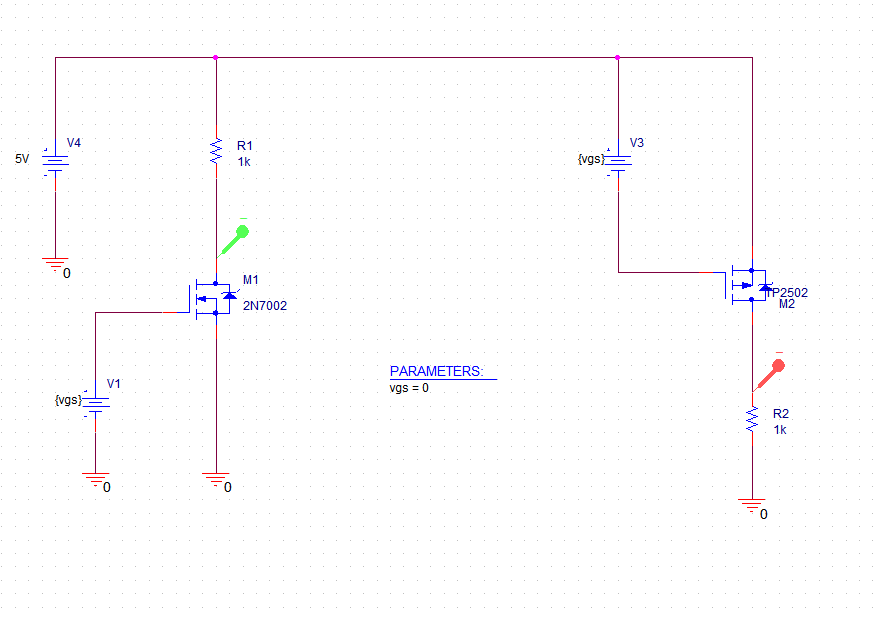

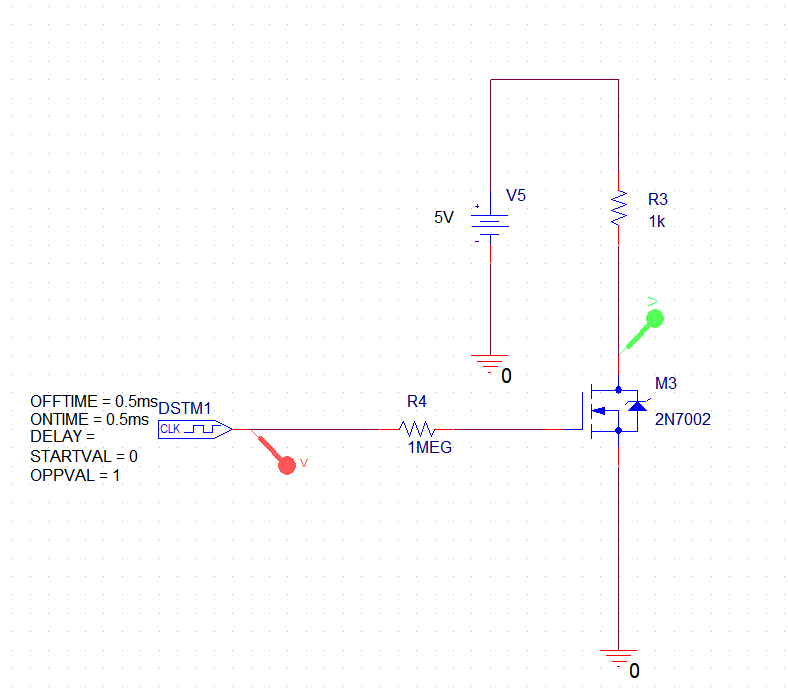

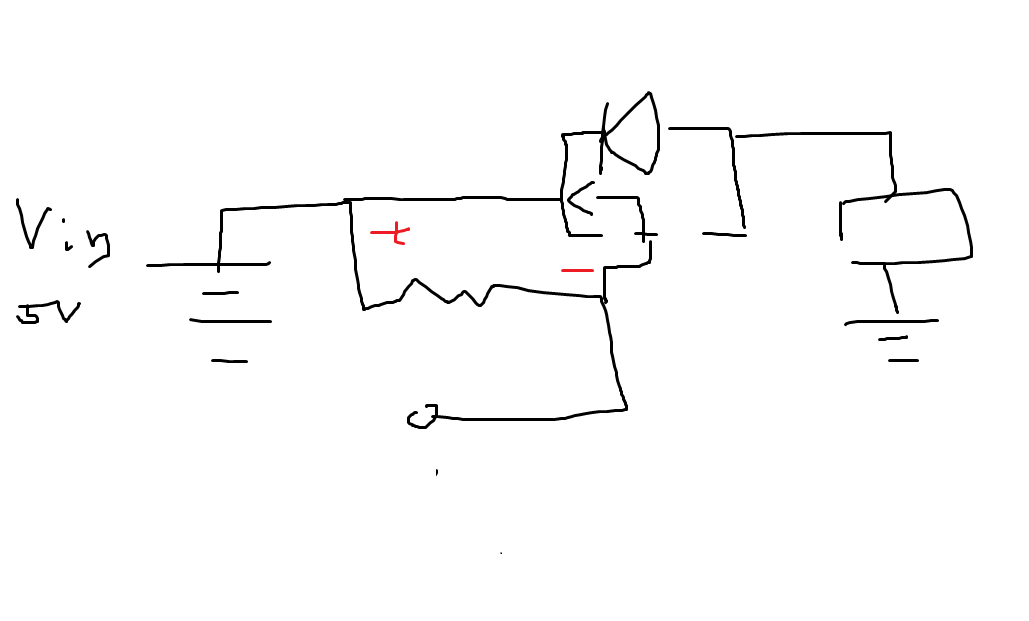

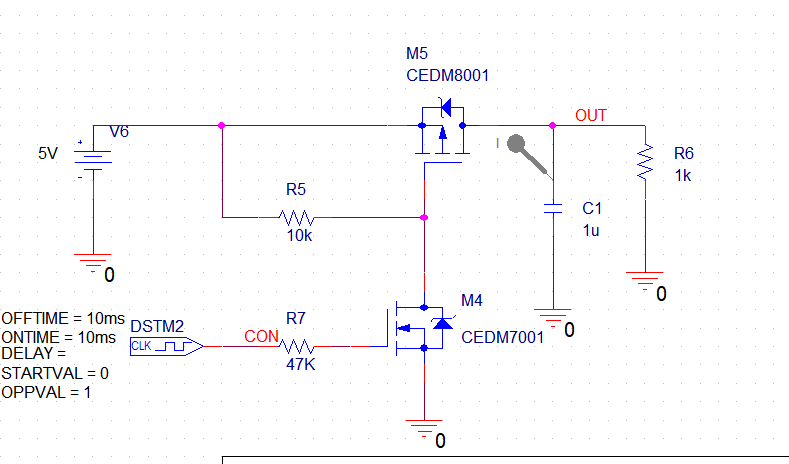

MOSFET 을 바꿧을 때

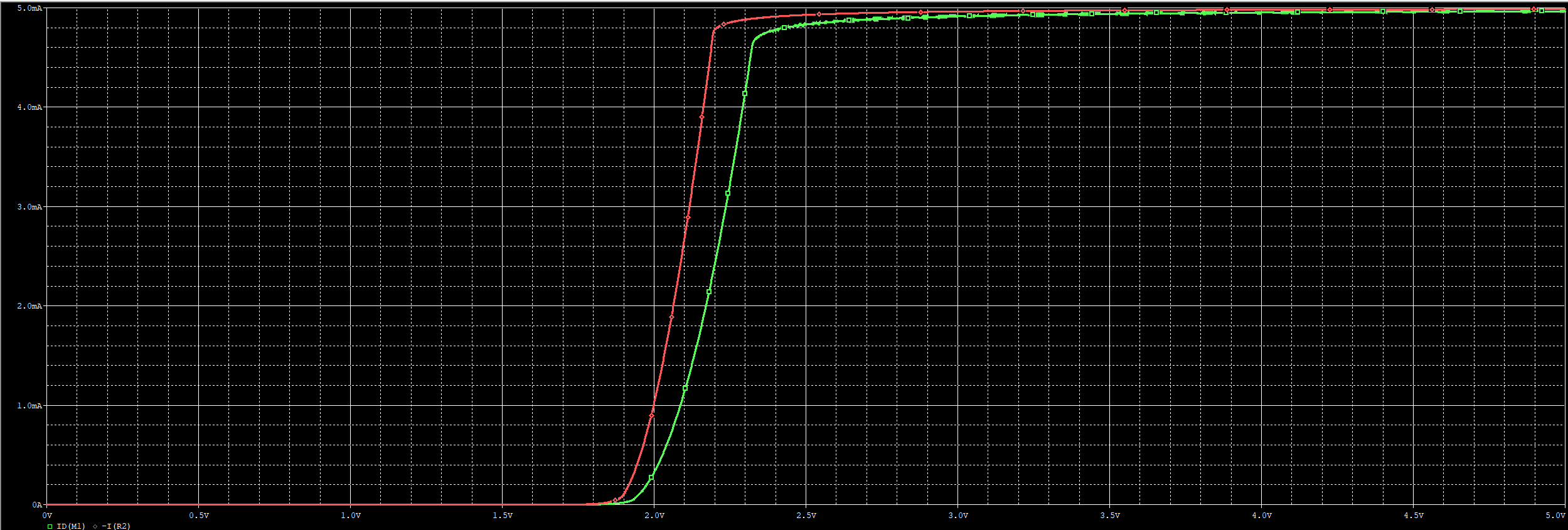

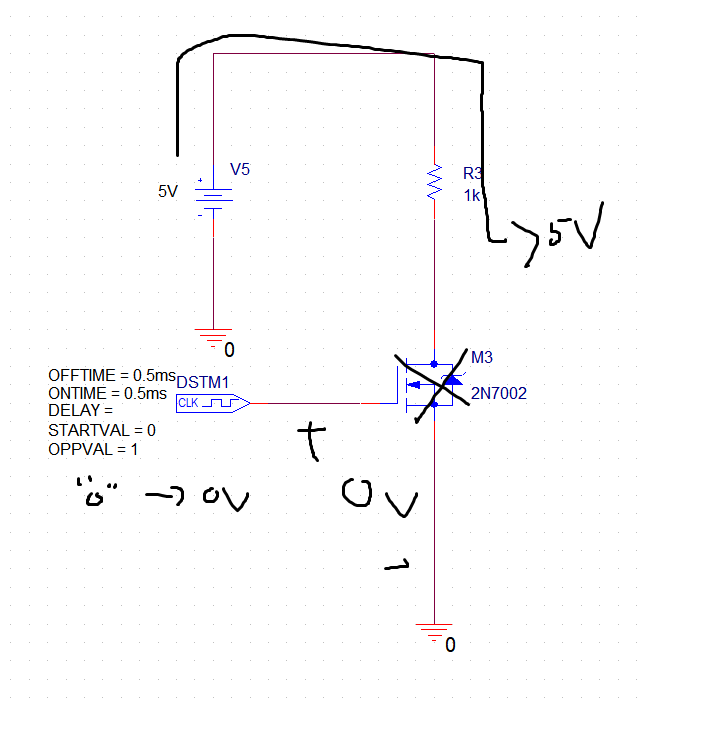

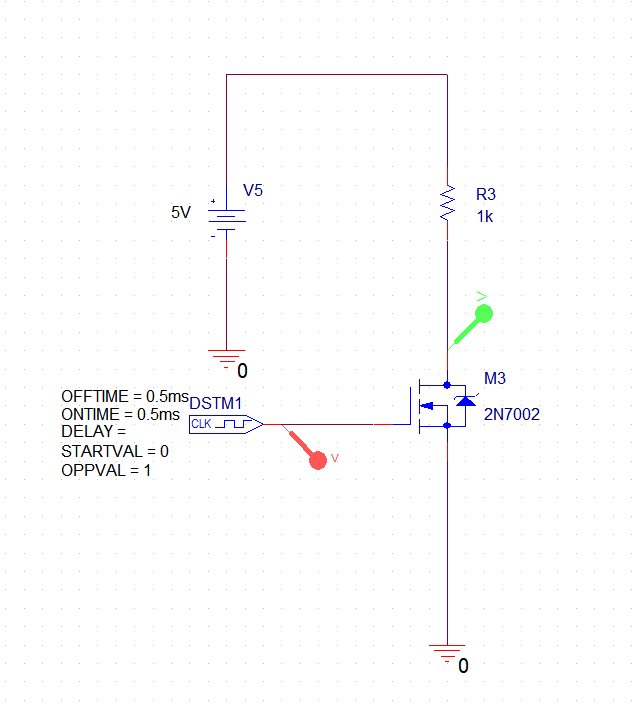

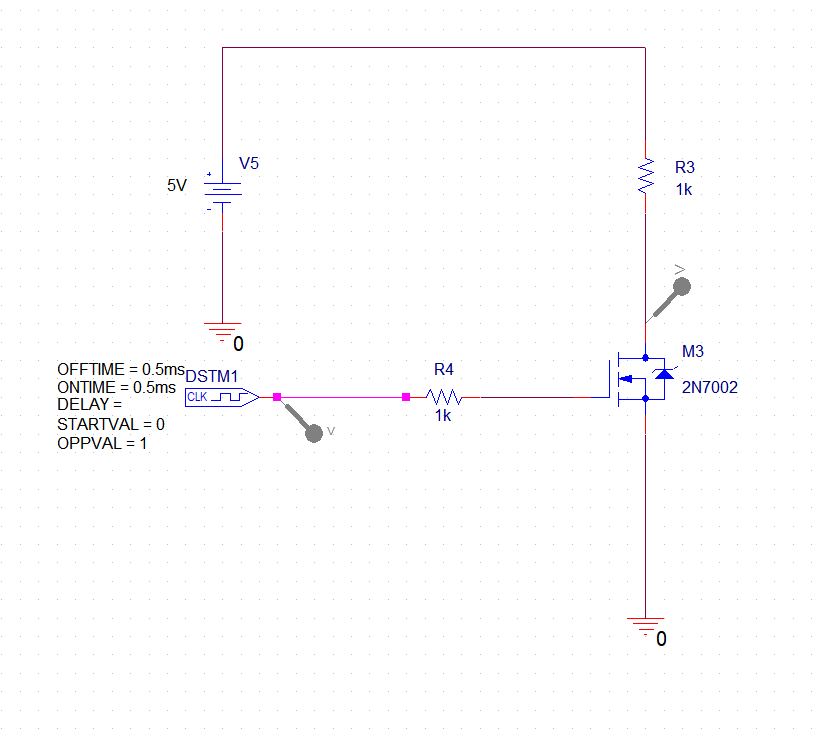

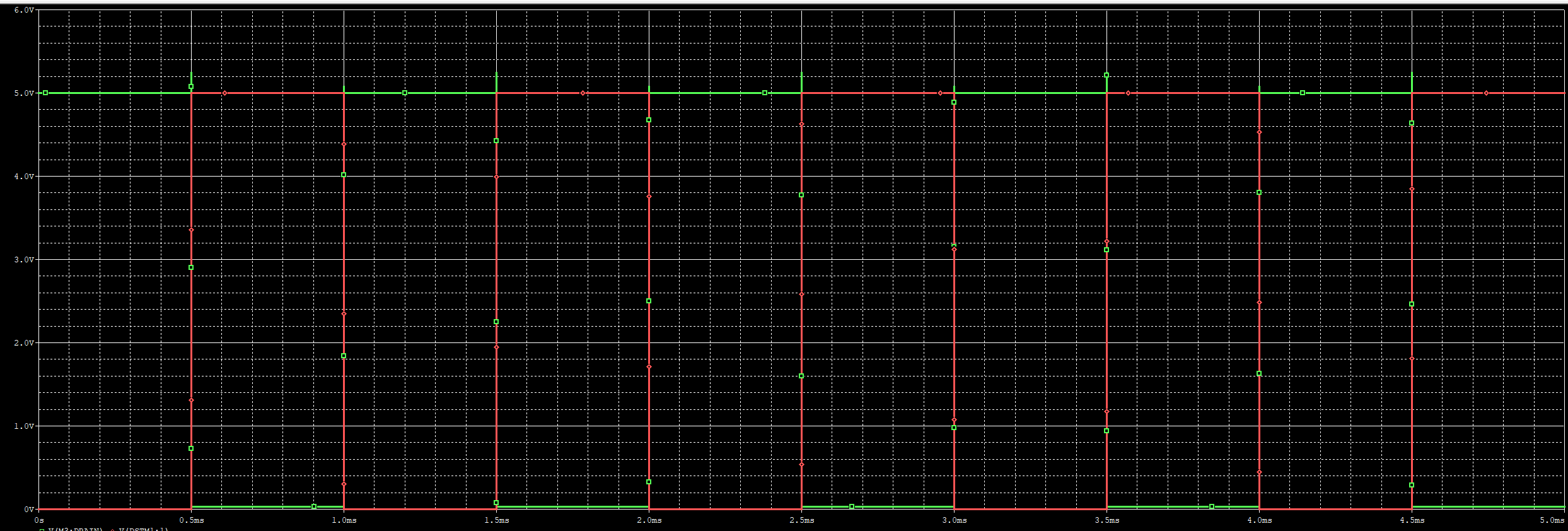

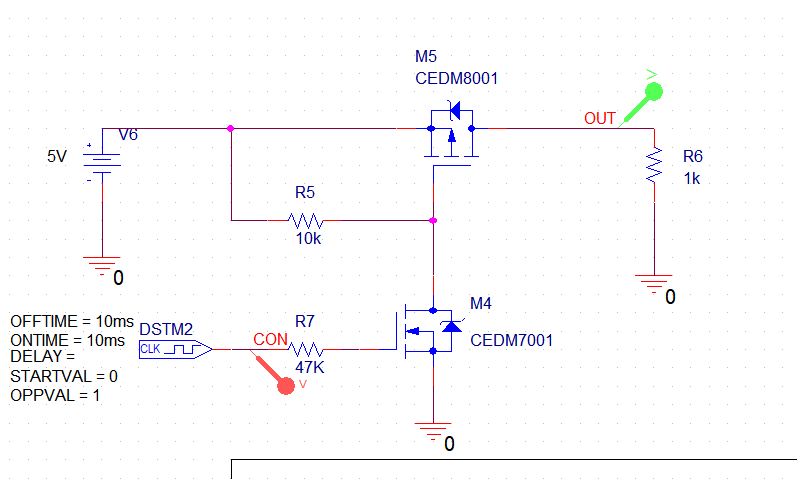

MOSFET을 이용한 Switching 회로 설계

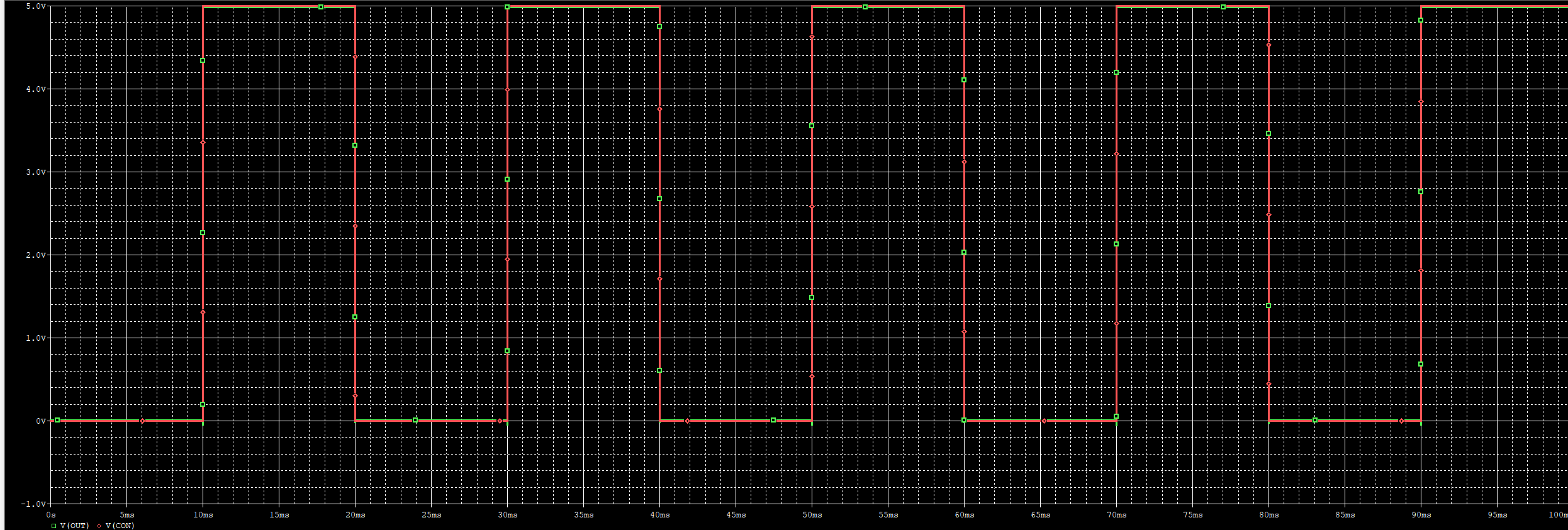

-논리 0일 때

-논리 1일 때

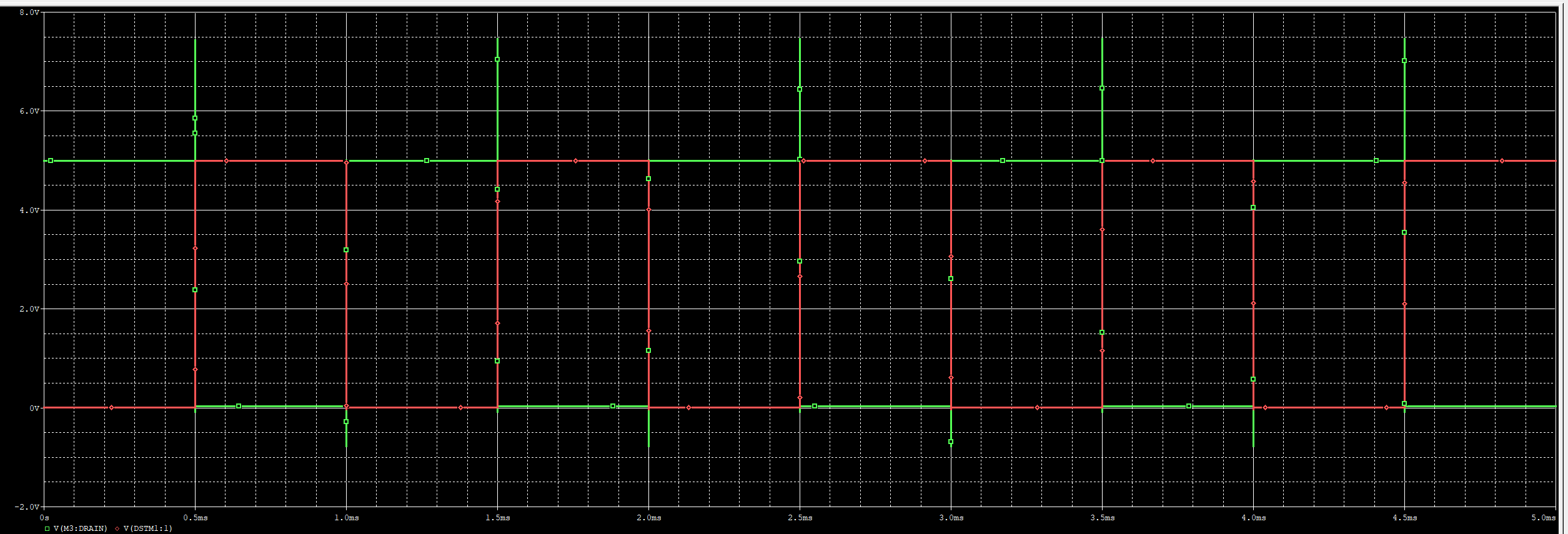

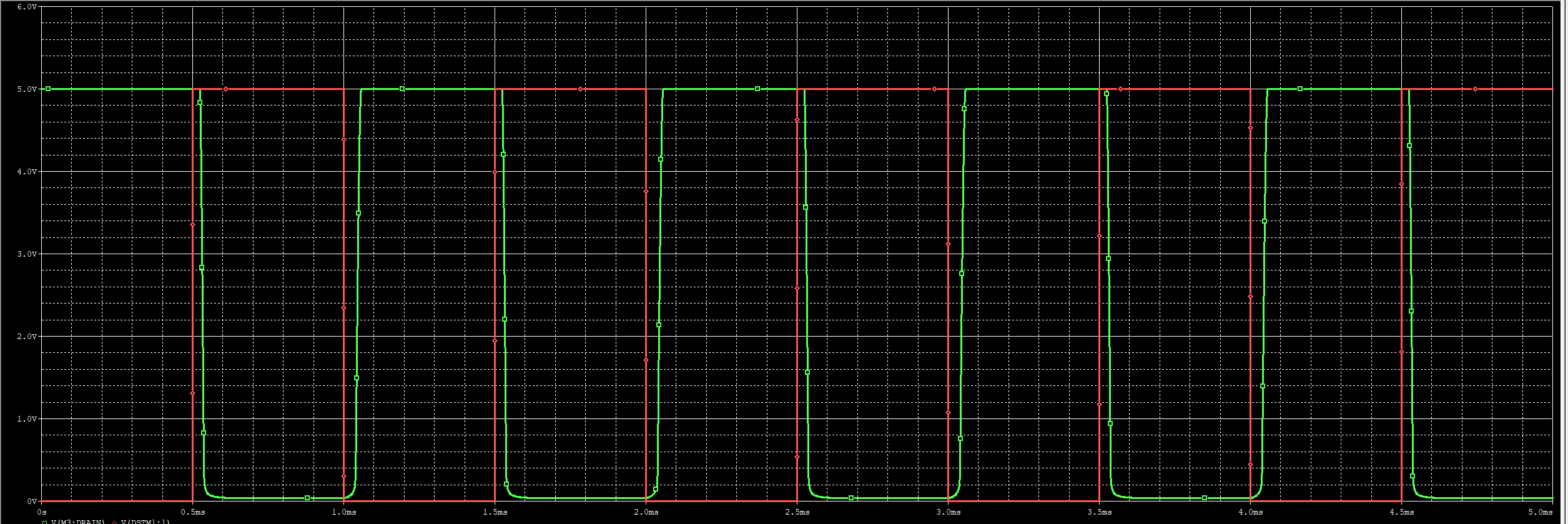

=>입력에 0v 출력에 5v

출력에 5v 입력에 거의 0v가까이 나옴

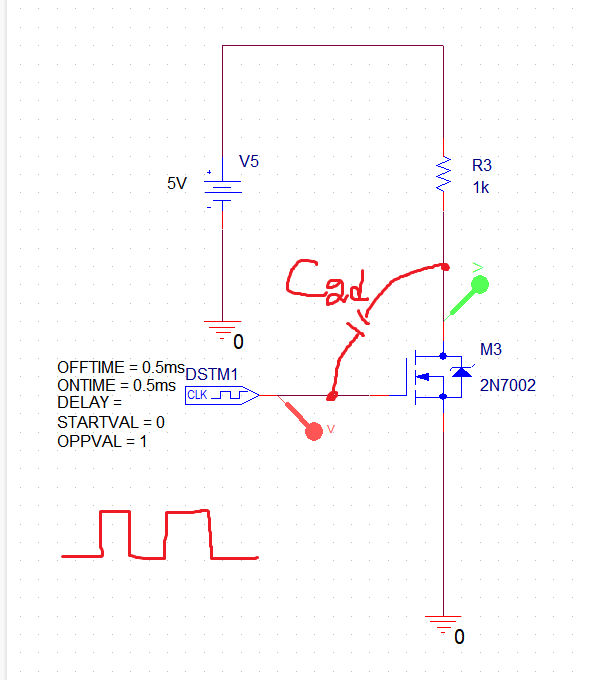

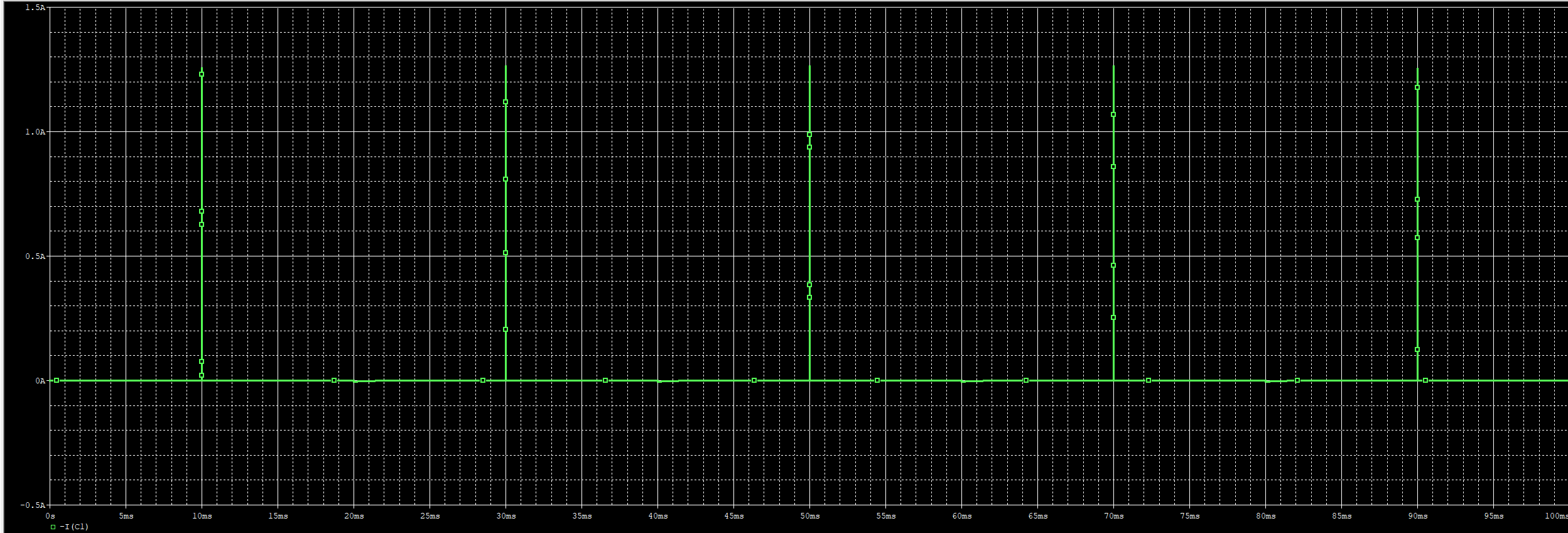

모서리에서 튀는 현상이 발생하는 이유 :

dv/dt가 가장 큰 부위가 edge가있어서 전류가 흐르게 된다.

C x dv/dt 의 전류가 흐르게 된다.

=> 작지만 D와 입력인G사이에 작은양의 커패시터가 있어서 튄다.

해결하는 방법으로는 전류의 크기를 작게 해야함 -> dv/dt의 값을 줄이게 되면 튀는 전류가 작아진다.

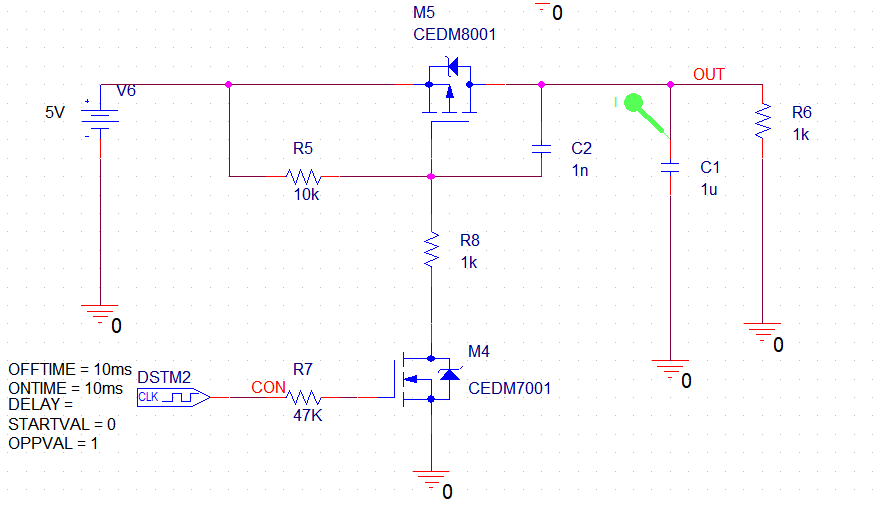

->pspice에서 시정수를 주면 됌

저항값을 달면 된다.

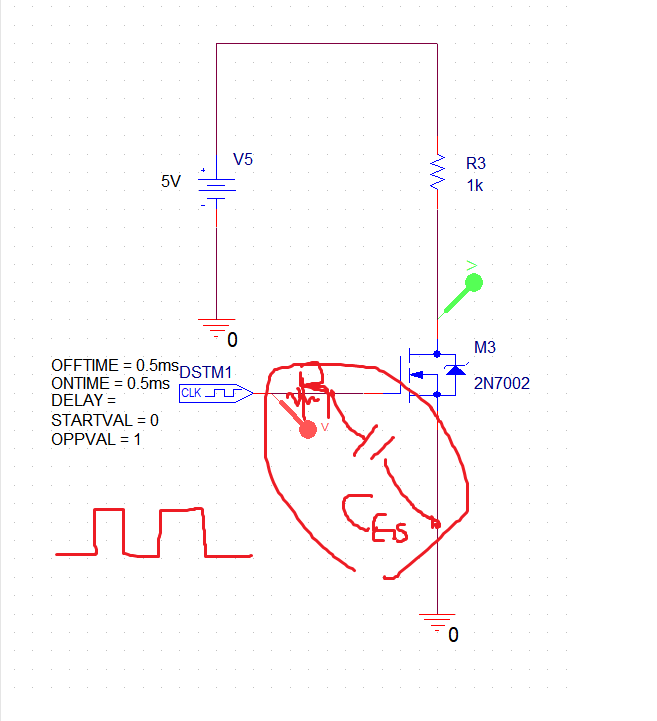

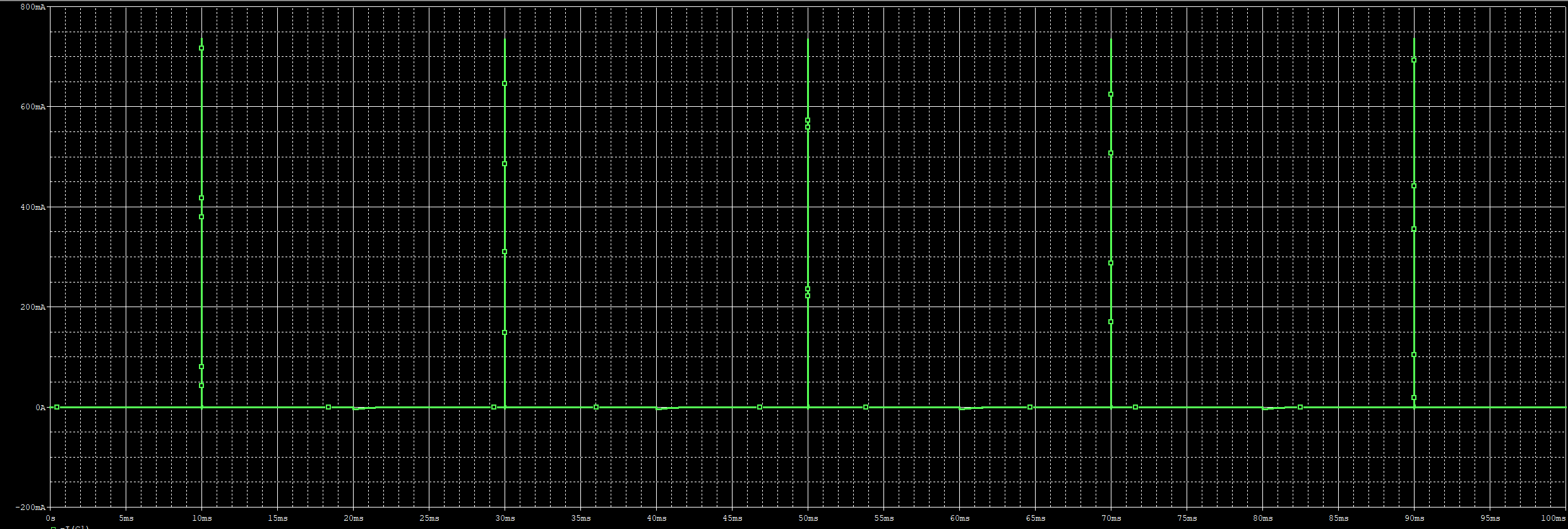

임의의 저항값 1k를 줬을 때

=> 튀는 값이 적어졌다

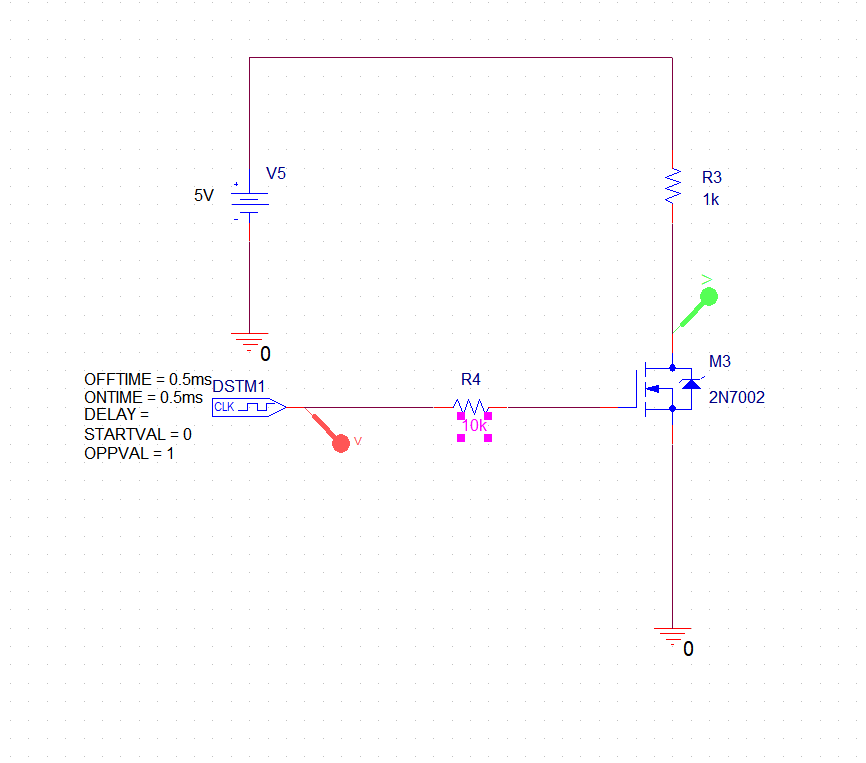

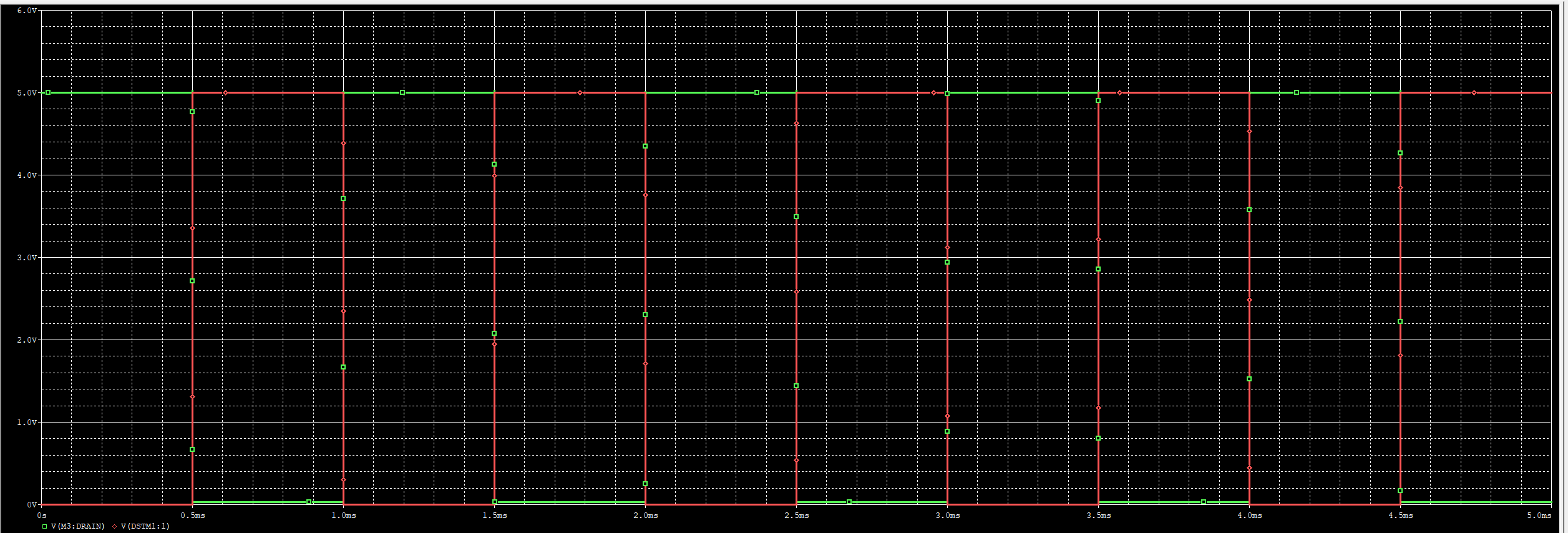

저항값을10k 주었을 때

=>값이 거의 튀지 않는것을 볼 수 있다.

d가 존재하는데 입력 전압이 dt/dv (rising,falling)일때 급격하게 변하니까 Cgd를 타고 전류가 D쪽으로 흐르게 된다. I = Cgd x dv/dt만큼의 전류가 흐른다 그래서 D쪽에 있는 전압이 Cgd를 타고 흐르는 전류와 저항이 곱해져서 값이 튀게 된다. 그래서 시정수를 해줘야한다 그렇게 했을때 rising,falling이 급격하게 변하지 않고 천천히 변하게 된다. 그래서 dv/dt값이 줄어들게 되어서 D에서 전압이 튀는값이 적게 튀게 된다.

저항값을 크게 주게되면

입력과 출력의 타이밍이 맞지 않게된다.

->적절한 저항값을 찾아야 한다.

입력신호 G단자는 C처럼 이루어져있기 때문에 입력단자인 G를 보호하기 위해서 저항이 존재해야한다

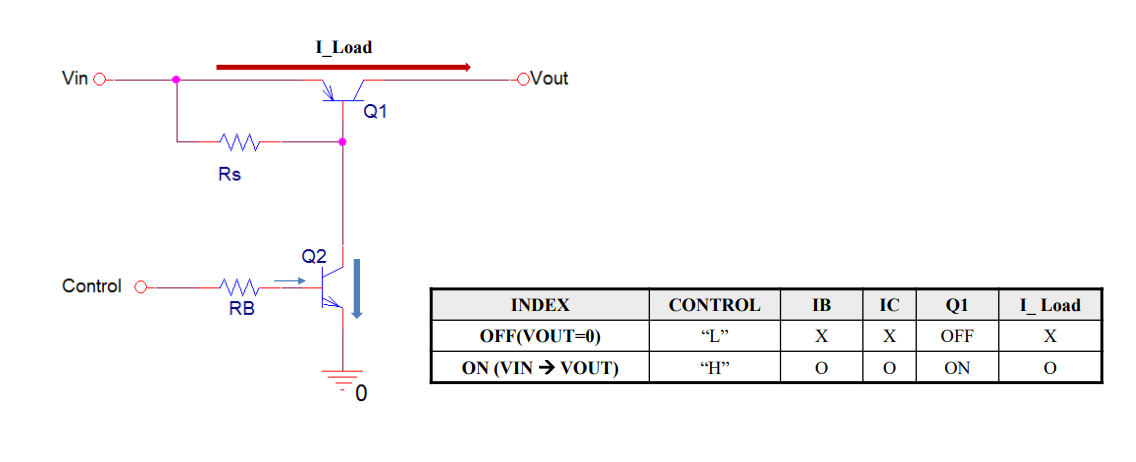

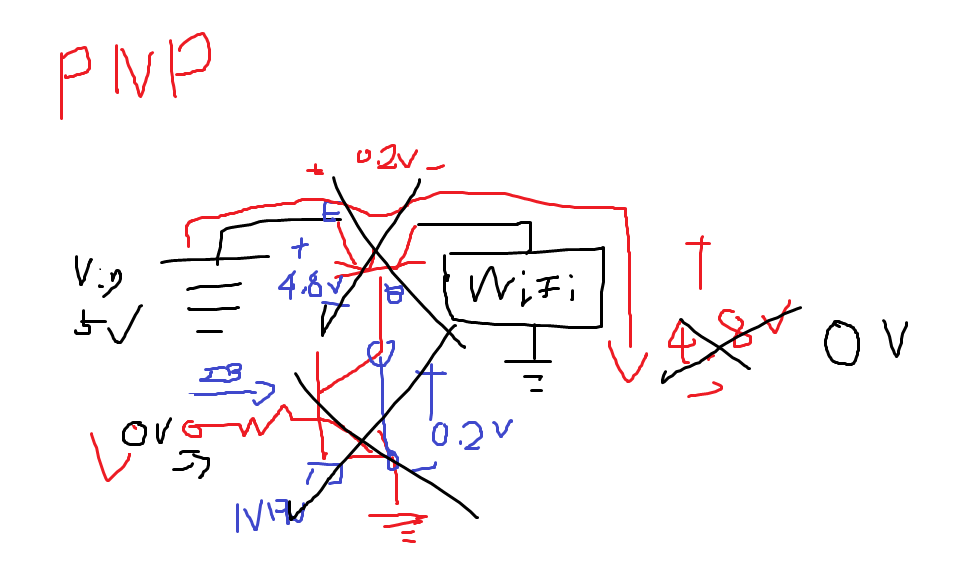

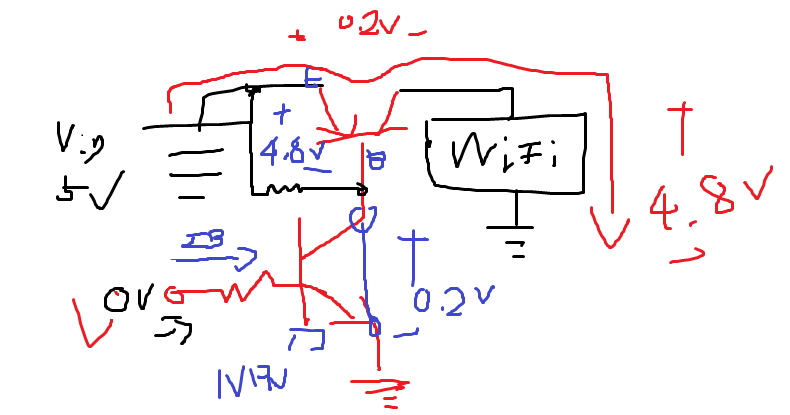

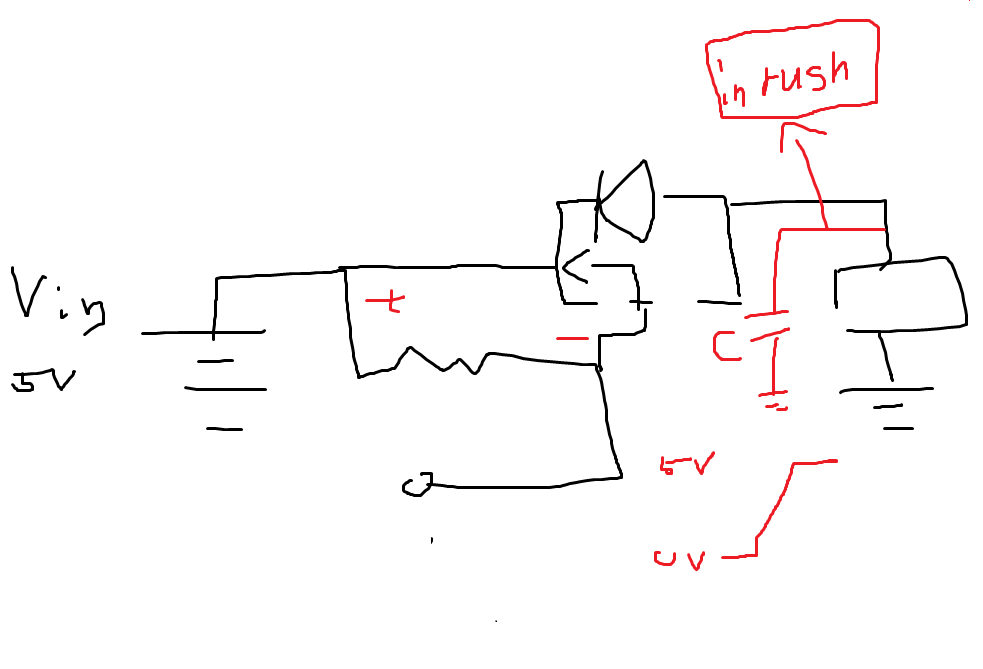

Load Switch 회로

- pnp와 npn을 조합한 직류전원(dc전원) on/off 제어회로로 Load Switch라고 한다

- Rs저항이 없으면 Q2 off시 Q1의 베이스가 floating(high Z)상태가 되어 외부 노이즈에 취약하여 불안전한 상태가 될 수 있다. 이러한 용도의 저항을 pull-up저항이라고 한다

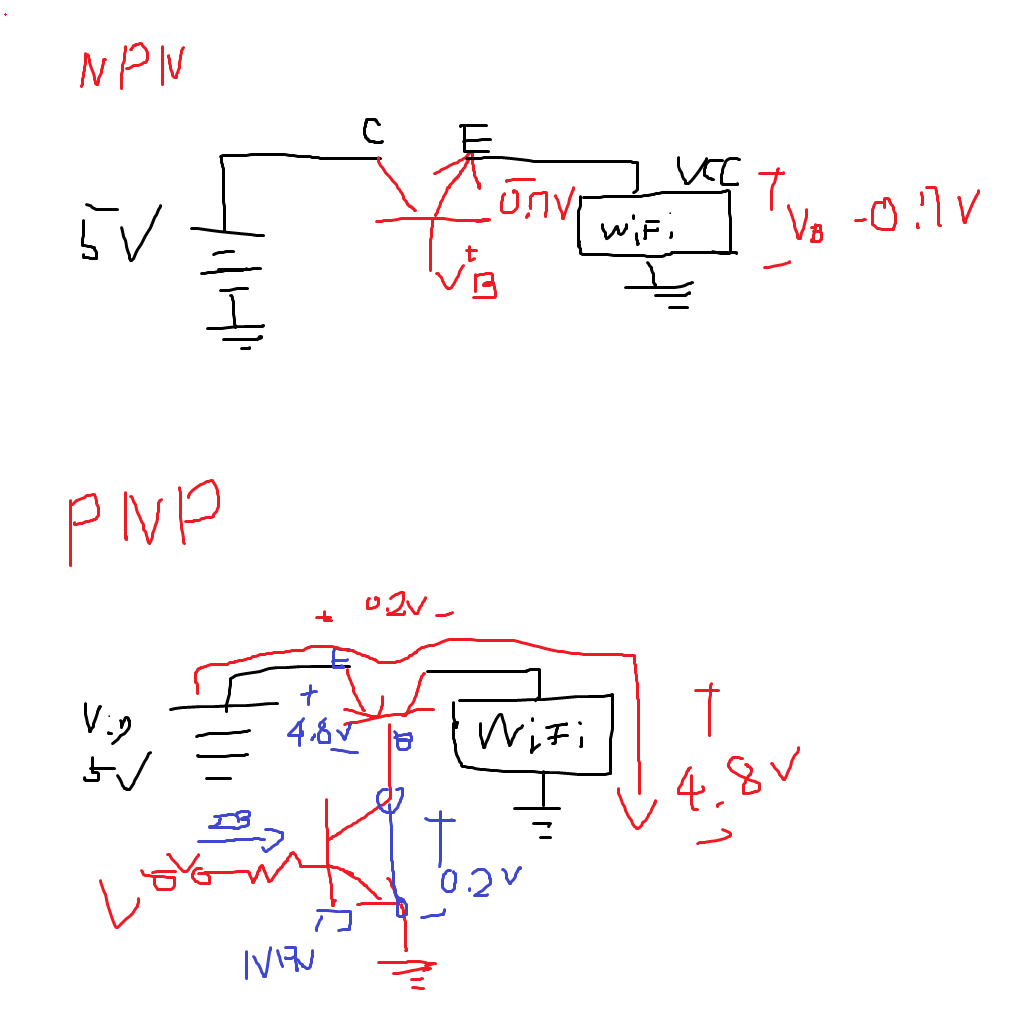

npn,pnp on 동작

pnp off 동작

0v가 흘러서 base전압에 0v가 흘러서 npn이 끊어지게 된다 -> pnp와 npn사이가 floating가 됌 ->회로에서는 좋지않은 현상->외부에서 쉽게 noise가 들어 올 수 있다.

->

저항을 연결해서 외부 noise등에 영향을 받지 못하게 한다.

=> power소모가 크다

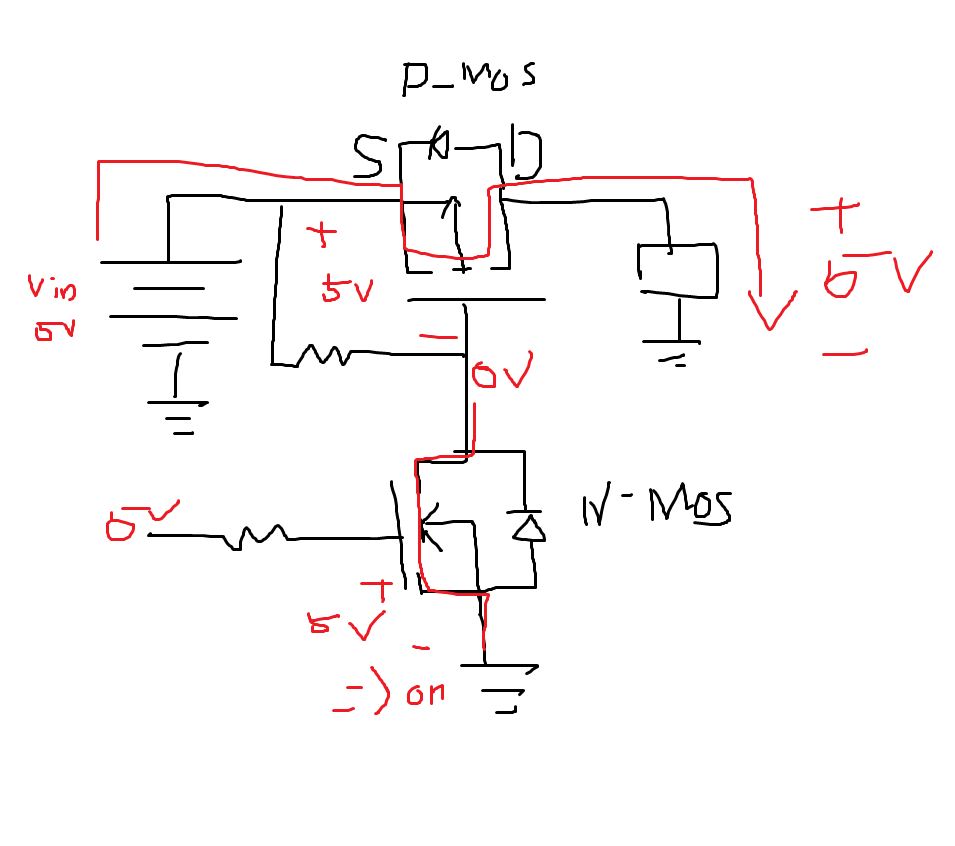

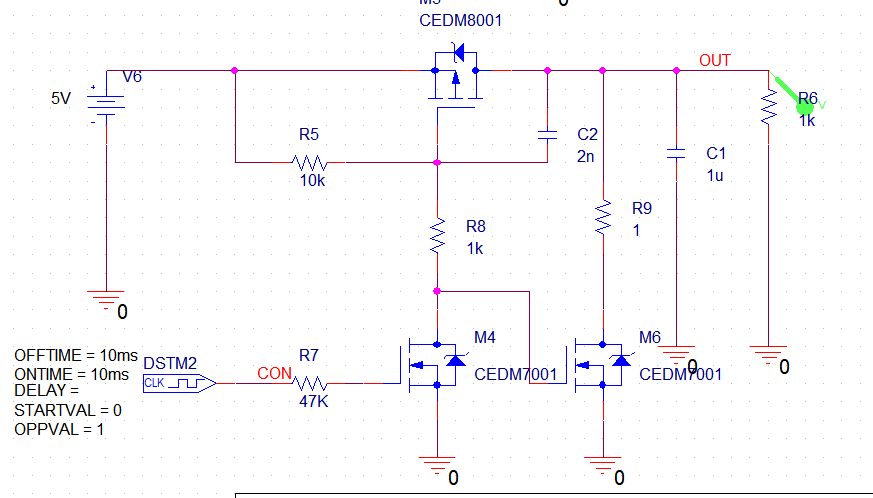

MOSFET을 이용한 Load Switch

p-mos의 문턱 전압보다 더 큰 값인 5v가 흐르기 때문에 p-mos가 on상태가 된다.

=>power 소모가 적다 =>가격이 비싸짐

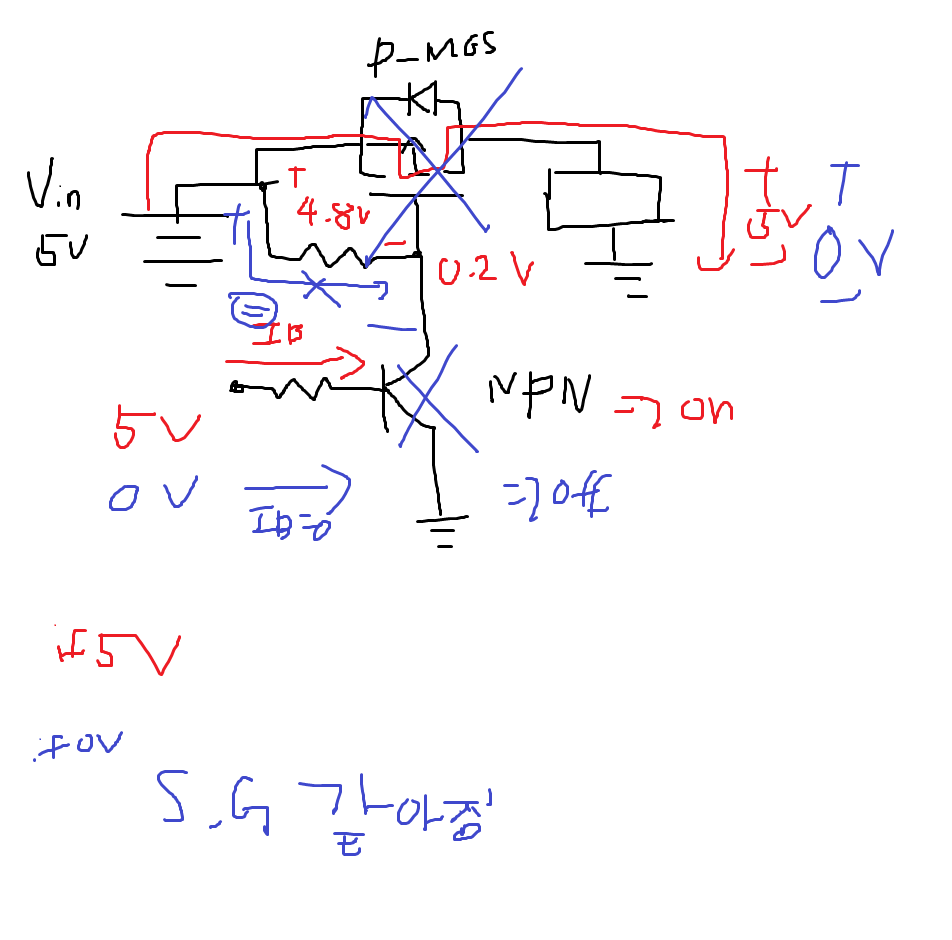

p-mos와 npn사용한 Load Switch

가격을 줄이기 위해서 n-mos를 npn으로 바꿔주면 된다.

p-mos만 사용한 Load Switch

외부전압에 5v를 주게 되면 전압차가 0이기 때문에 off가 되고

외부전압에 0v를 주면 전압차가 5v가 되기 때문에 on이 된다

이러한 구조를 단순형이라고 한다.

=>이러한 구조는 조건이 잘 맞아야 한다->넘겨주는 전압과 외부 전압이 같아야지만 잘 된다. 만약 vin이 12v이고 외부저압이 5v이면 양단전압이 7v가 되고 외부전압을 0v로 주면 양단 전압이 12v가 된다 이 경우 둘다 on상태가 된다.

외부전압으로 0v가 들어가면 출력으로 0v가 되고

외부전압으로 5v가 들어가면 출력으로 5v가 된다.

하지만 실제ic라면 커패시터가 존재한다

inrush가 발생한다 ->커패시터 고장 mosfet고장 ->전원고장

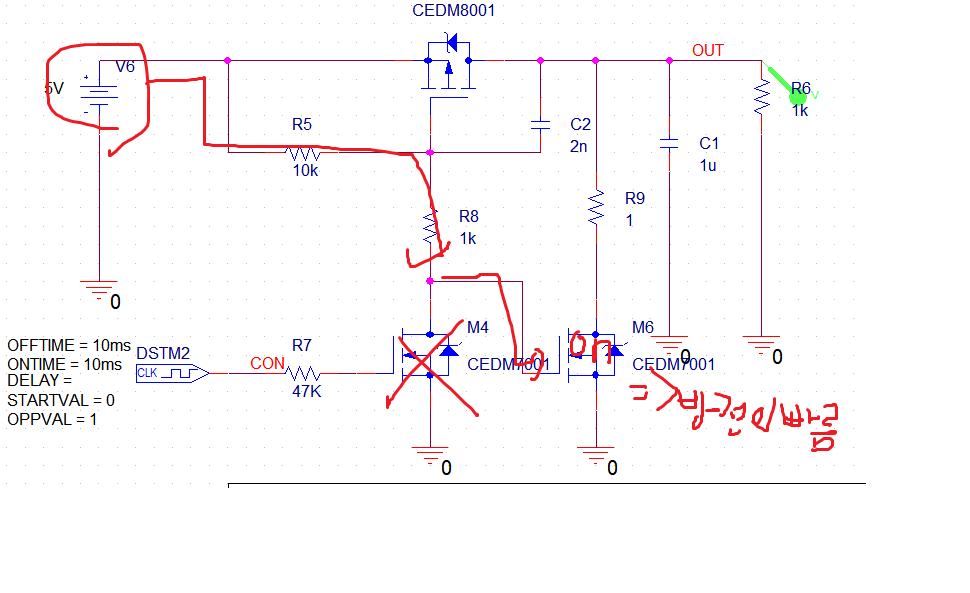

대책으로는 switch on되는 과정에 시정수를 넣어서 dv/dt를 늘어지게 만들어 주면 dv/dt가 줄어들어서 흐르는 전류의 값이 작아진다.

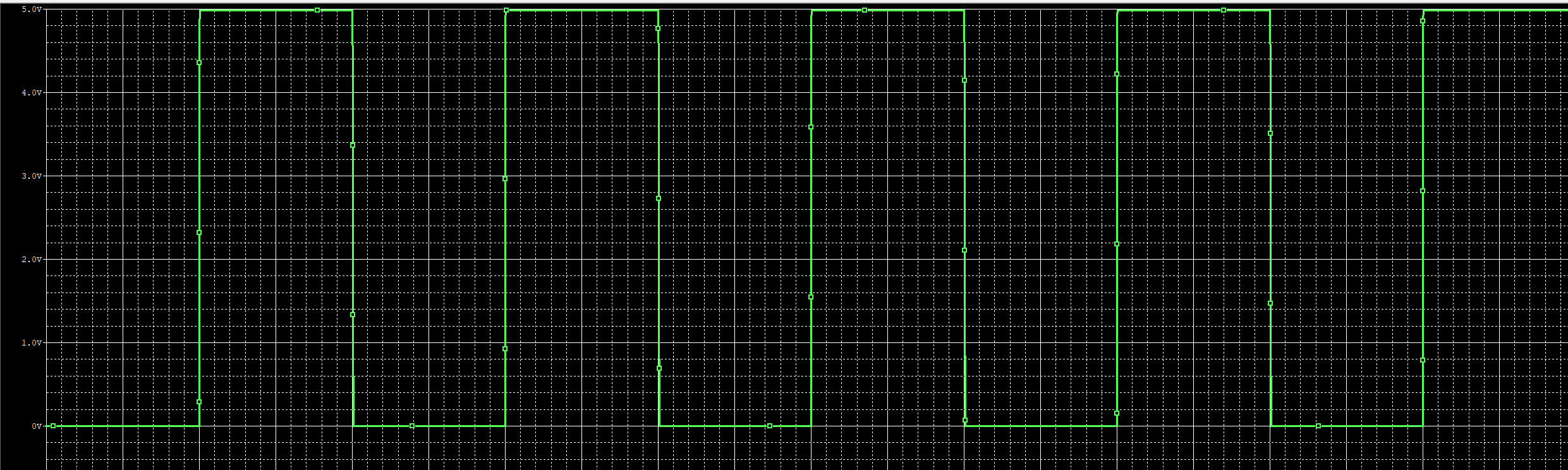

inrush current가 줄었다.

=>시정수를 크게하면 할 수록 inrush current가 줄어들게 된다.

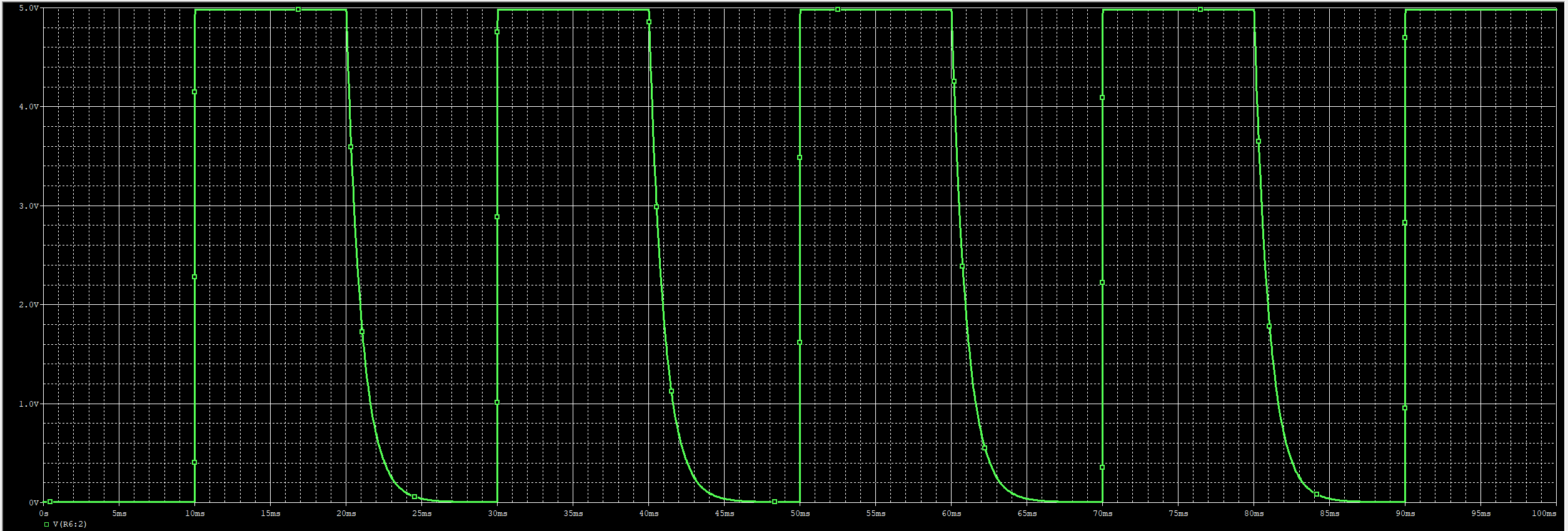

출력 전압이 천천히 방전이 된다

-> 방전이 빨리 되어야 하는데 방전이 느리기 때문에 문제가 발생할 수 있다.

fast discharge회로를 단다

->방전이 빠르게 된다.