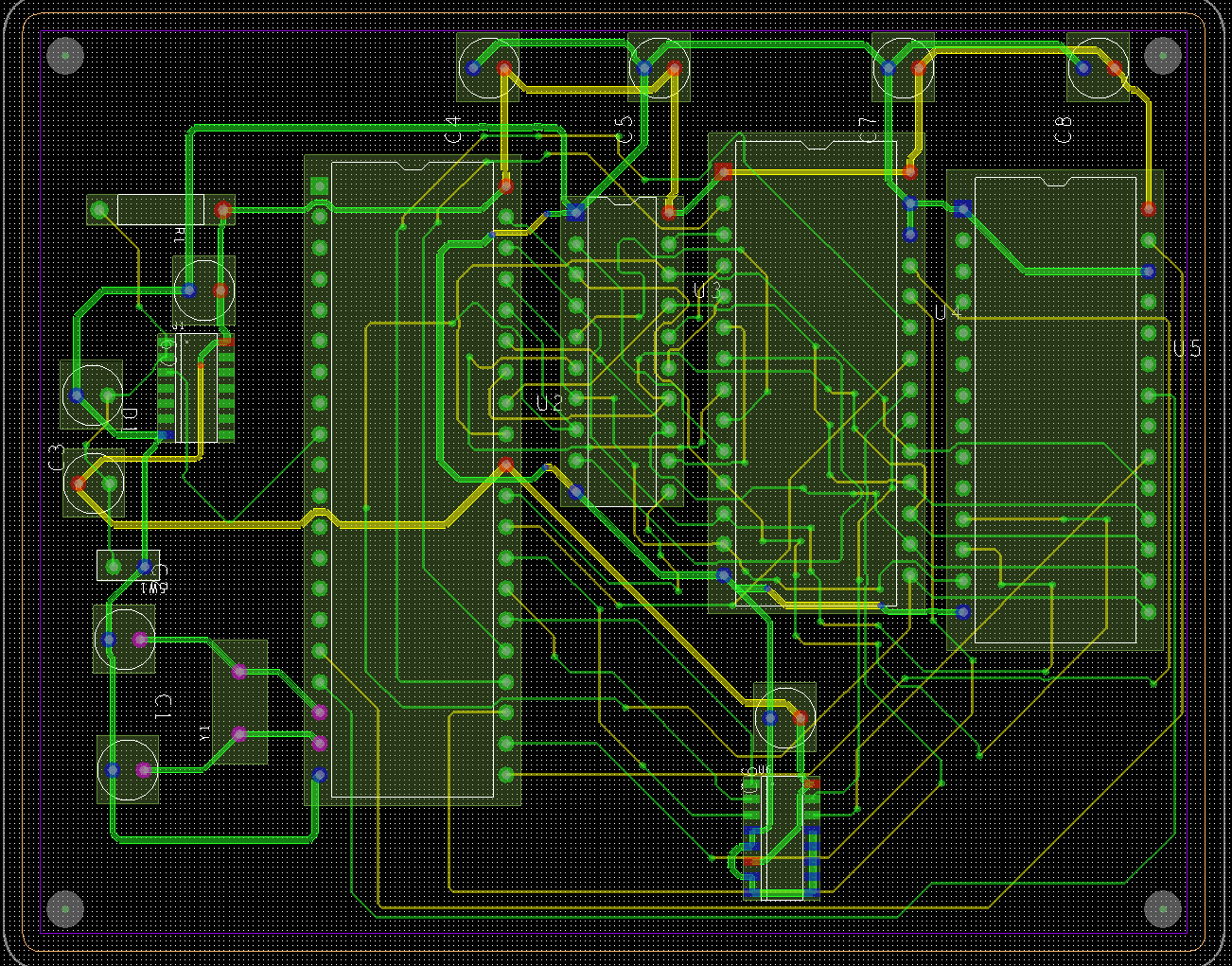

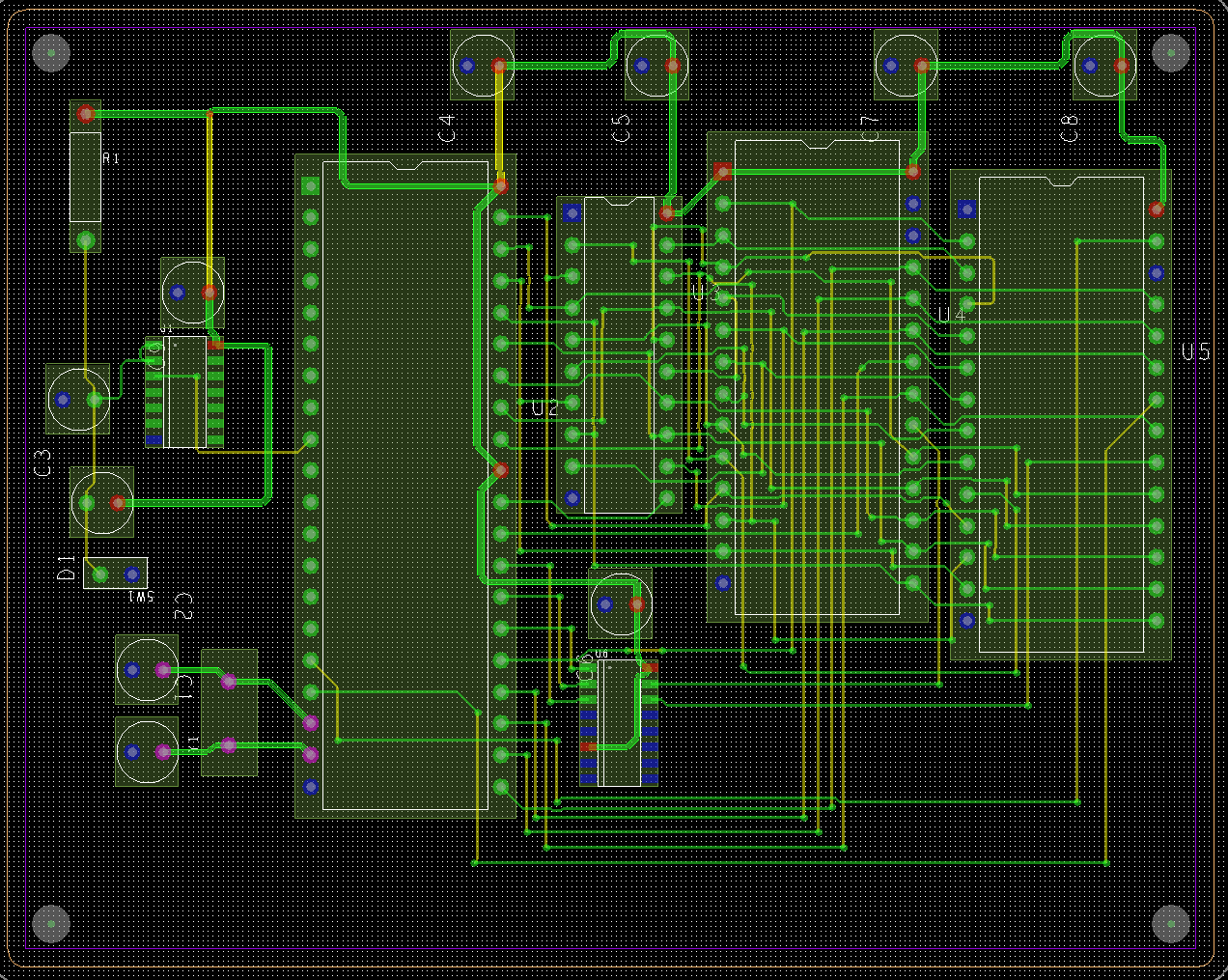

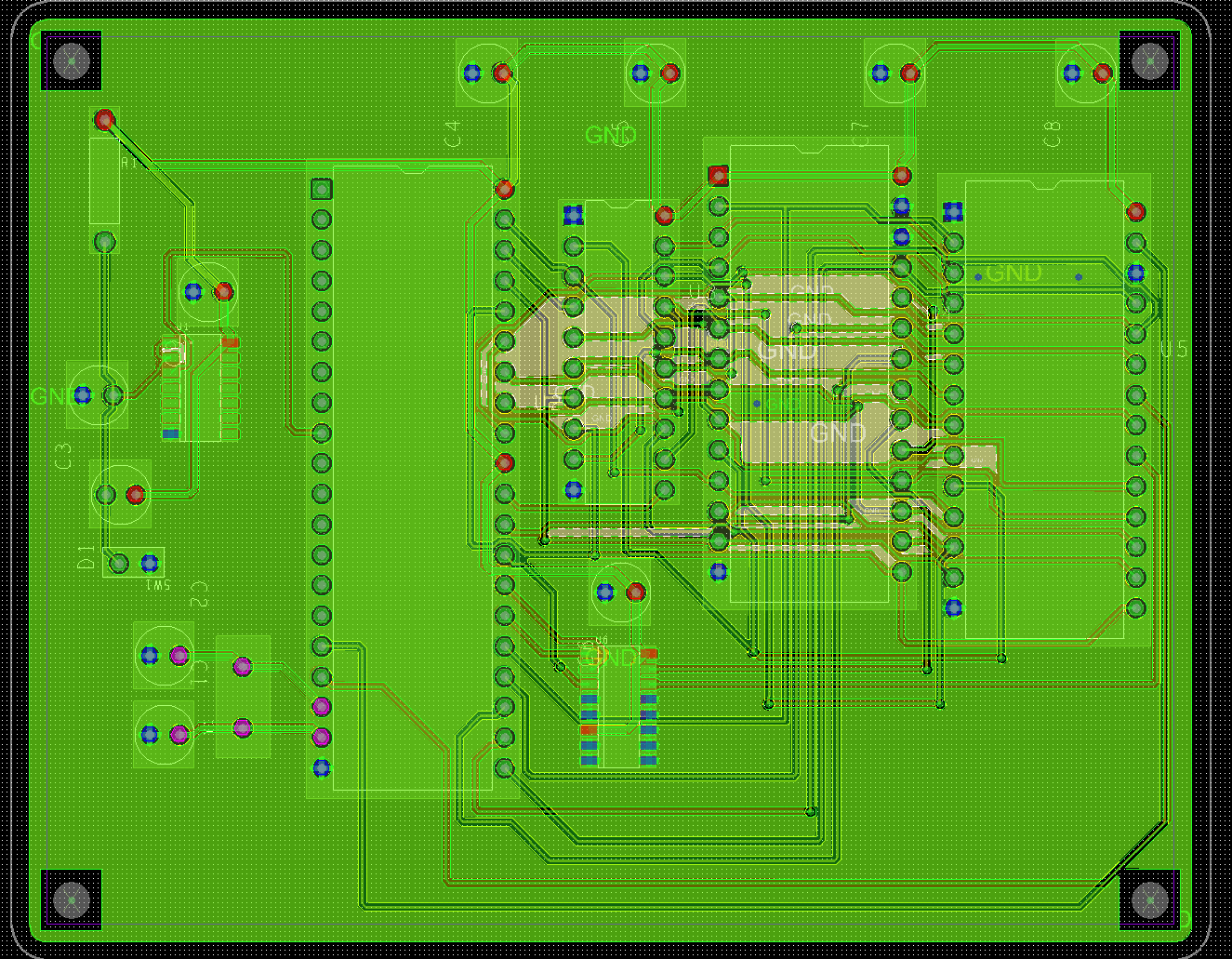

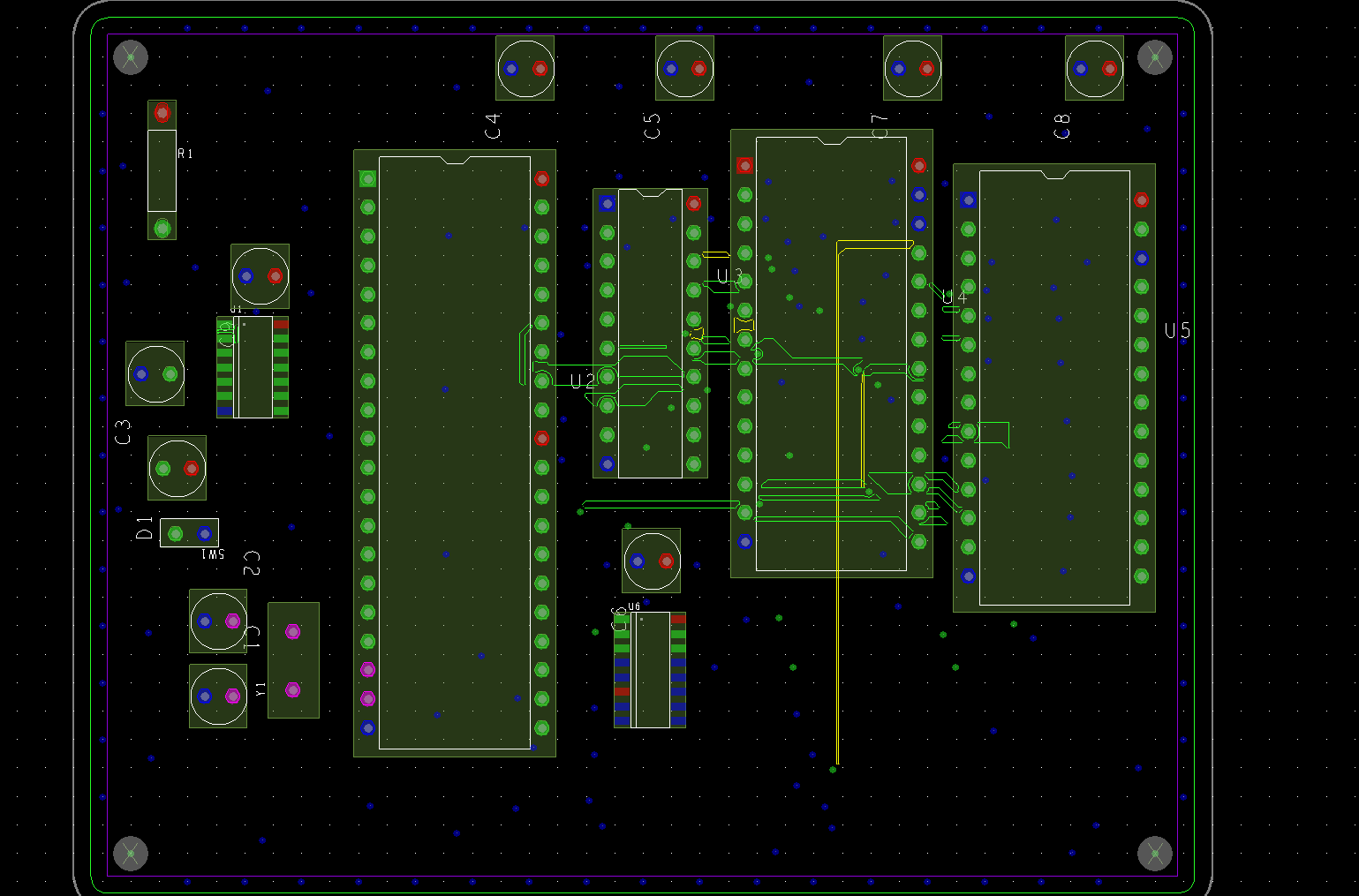

어제 ROUTING 한 PCB을 제대로 배워서 다시 만들 예정이다.

- 가로는 TOP으로 세로는 BOTTOM으로 만들면 VIA의 수를 줄일 수 있음

- 그 후 VIA를 줄여나가는 작업을 해야함

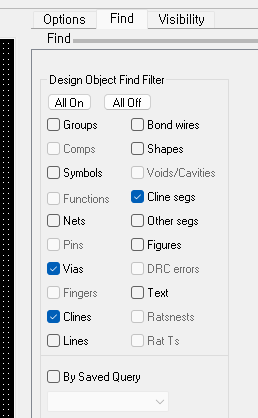

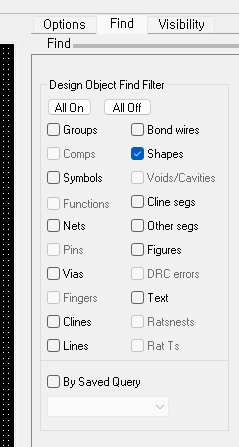

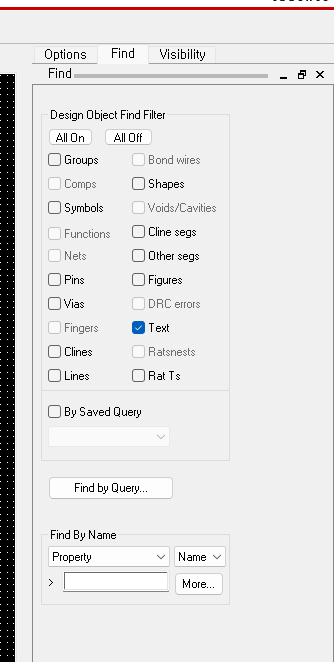

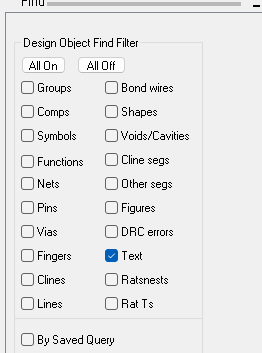

DELETE 명령어를 누르고 선들만 지우기 위해서 Find에서 3개만 체크 한다

cline segs : seg별로 지울 수 있다

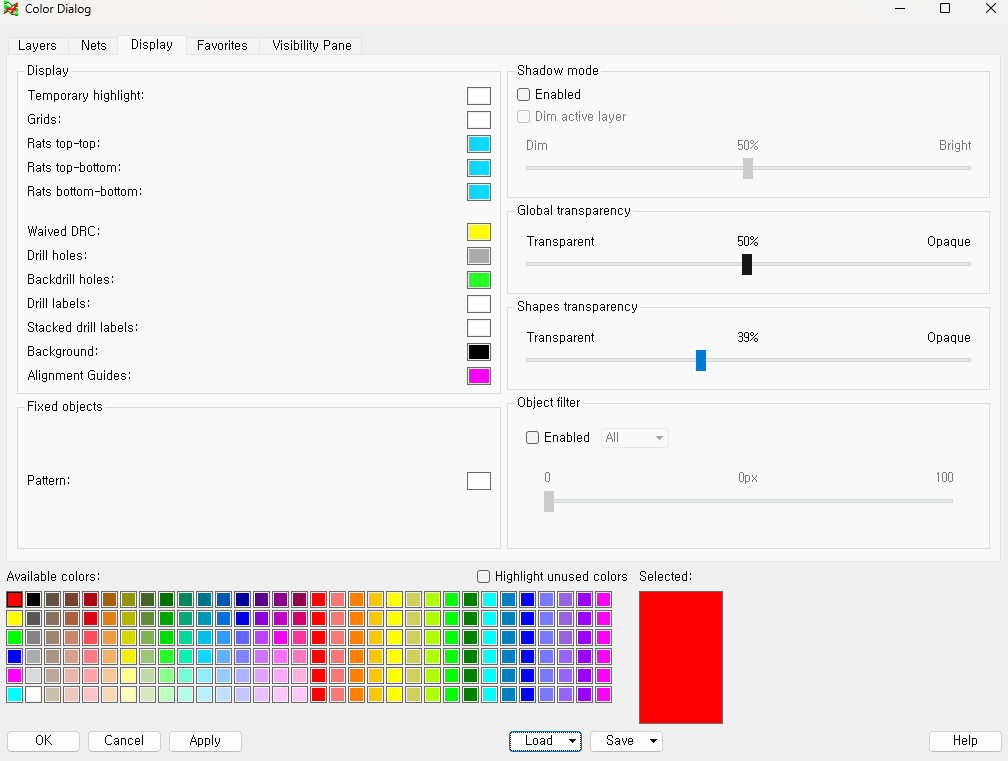

transparent는 투명도

설계할 때는 50%가 가장 좋다

양면 설계할 때 배선 순서

1. 중요한 신호선 부터 배선

->power,grd(배선x),clock,critical net...

gnd는 나중에 배선이 다 끝나고 남는 빈 땅을 그라운드로 다 덮을 예정 -> 보드내에 들어오는 noise를 빼내기 위해서 gnd로 덮는다

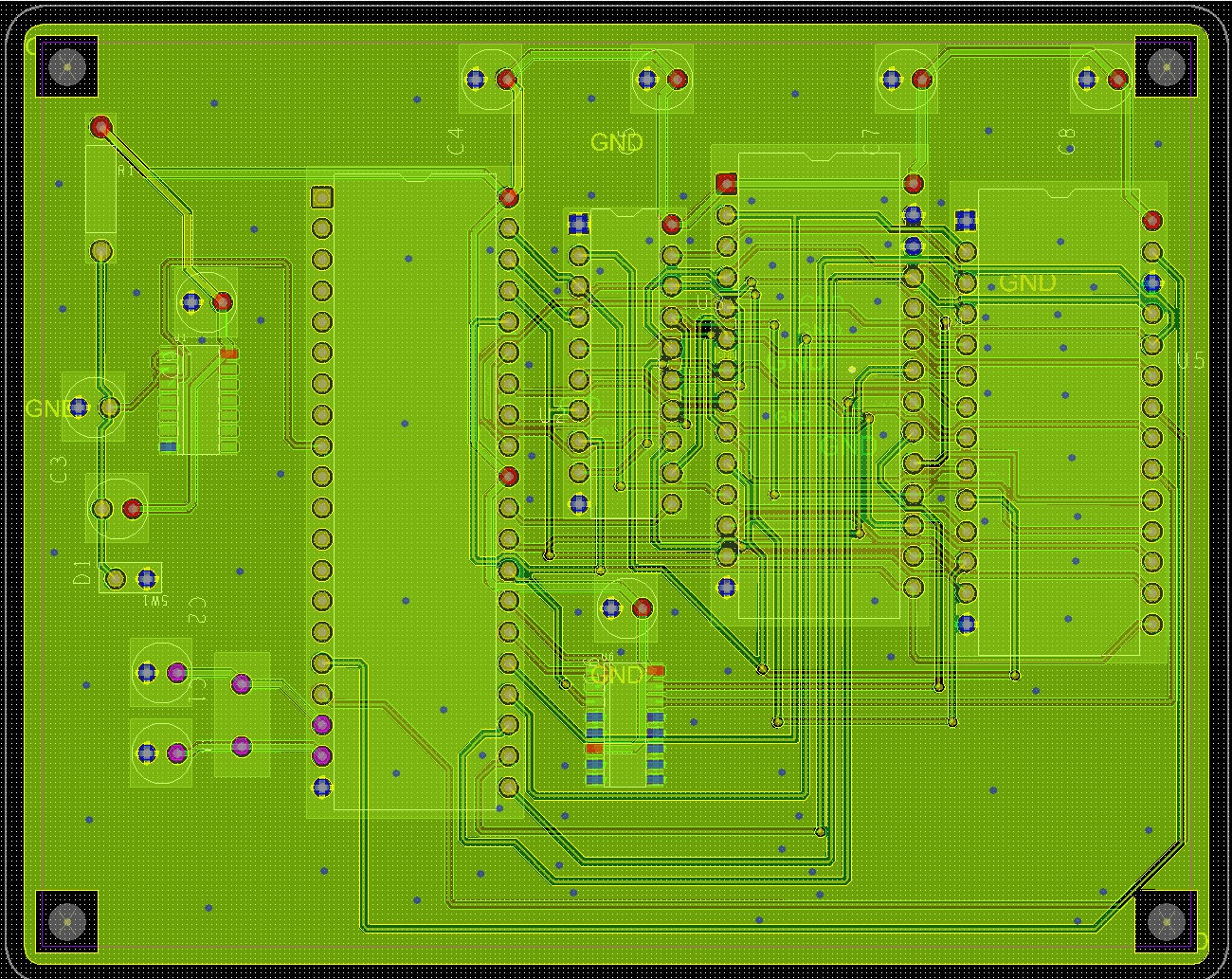

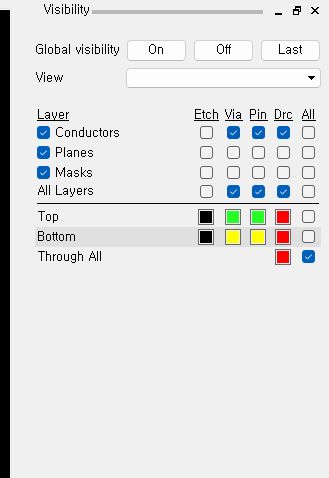

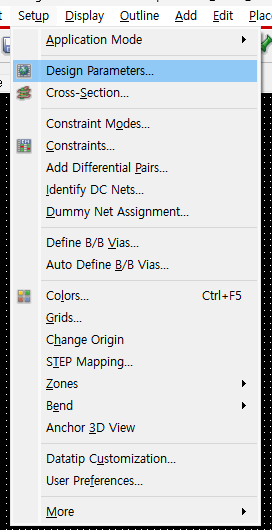

설계할 때 gnd를 안보이게 하기 위해서

이렇게 설정을 해준다.

-

mcu 주변부 부터 배선

-> 주요 신호선이 복잡하고 어려운 부분 -

long net를 배선

-> 신호선의 길이가 길게 연결되는 net -

나머지 net배선

->normal signal

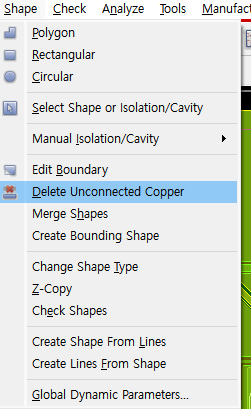

VIA 확인하기

VIA는 30개 아래로 만드는게 좋다.

필요없는 VIA를 지움

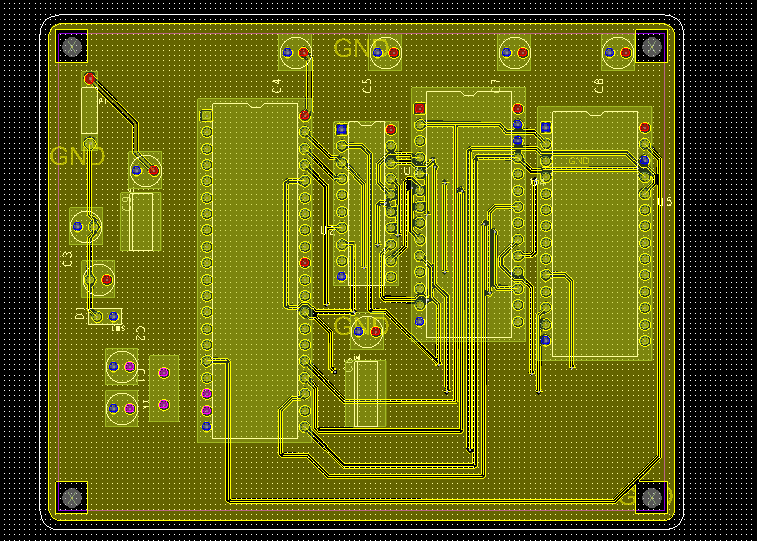

VIA가 25개가 된것을 볼 수 있다.

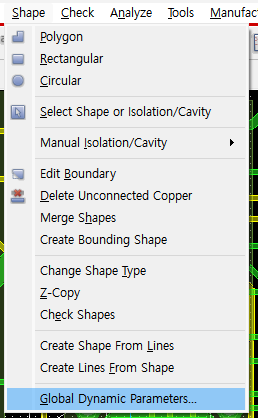

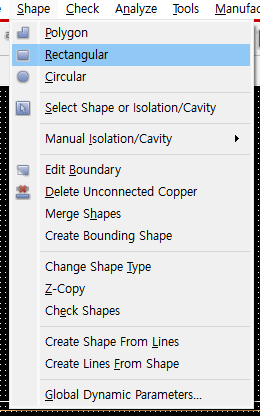

동판 배치

1. 배선완료 후 TOP/BOTTOM 남는 공간에 Ground 동판 채우기

2. Reference Silk 정리하기

3. 새로운 Silk 입력하기

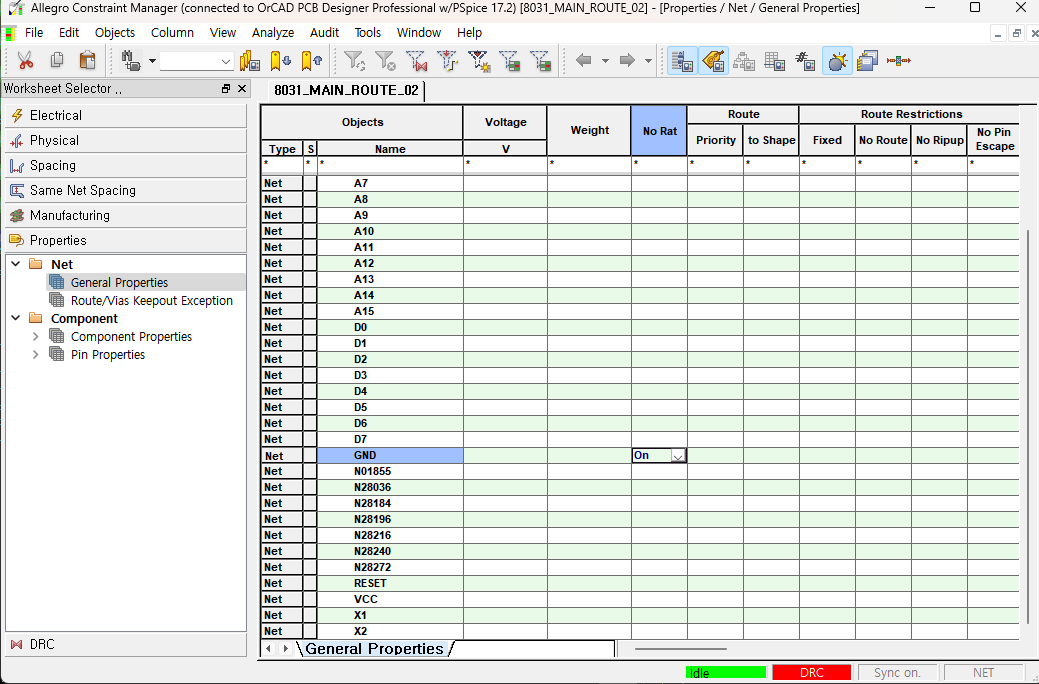

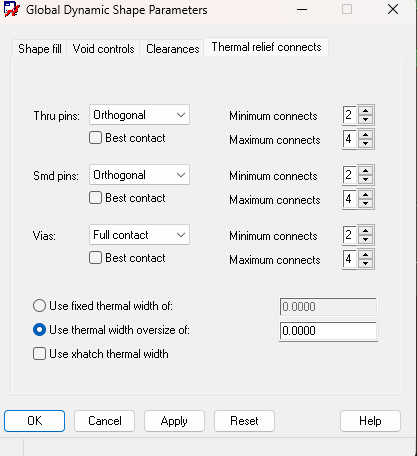

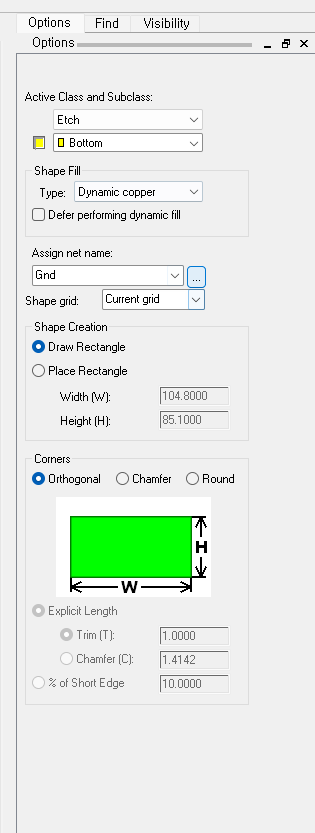

어떻게 설정 되어있는지 확인이 가능하다

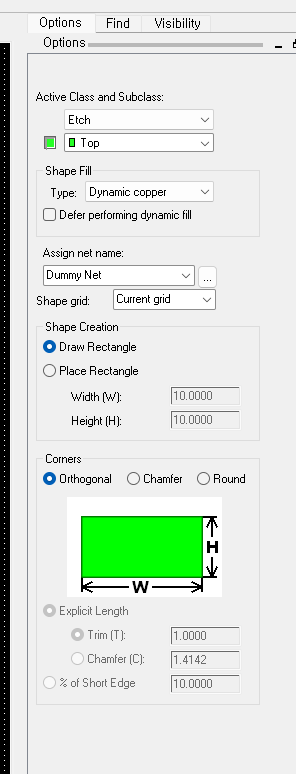

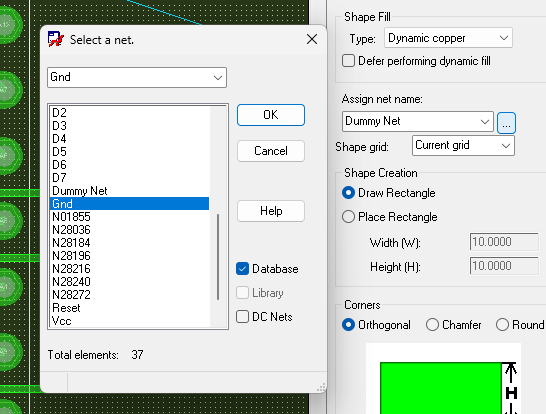

assign net name 을 gnd로

그리고 보드를 네모로 채우면

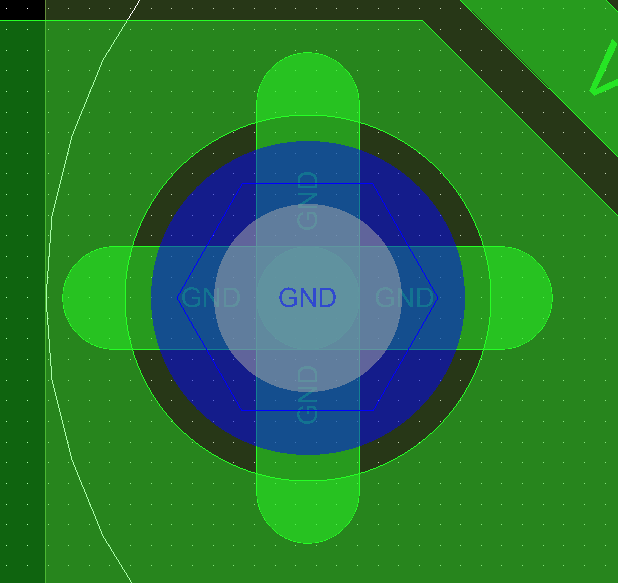

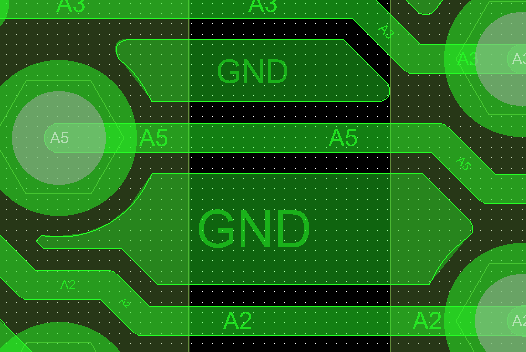

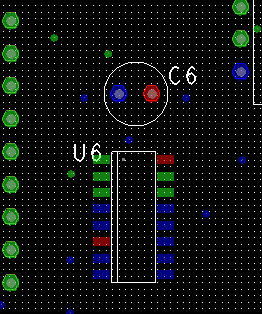

gnd가 이렇게 나온다 이게thermal relief이다.

bottom도 똑같이 설정해준다.

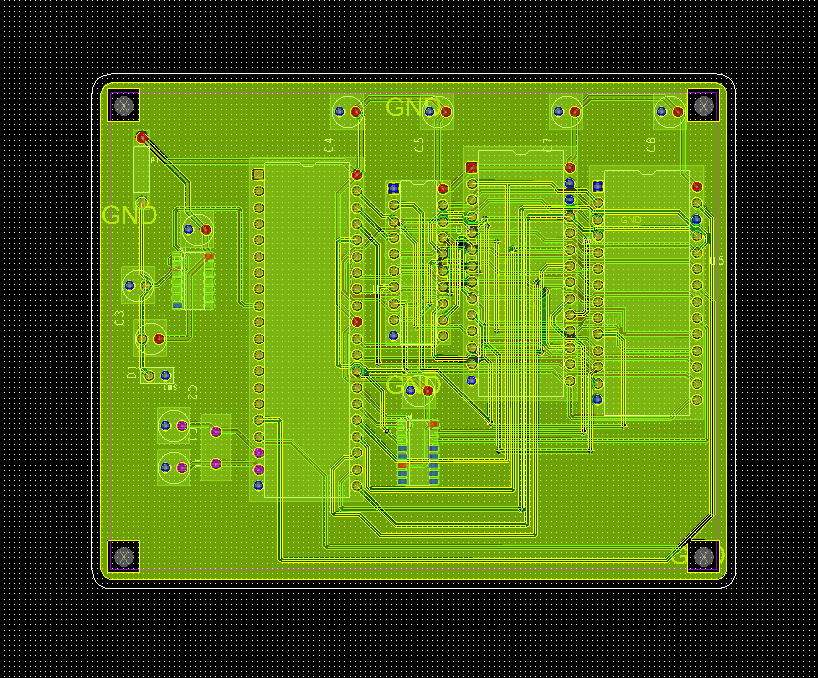

top과 bottom을 둘다 체크를 하면 이렇게 나오게 된다

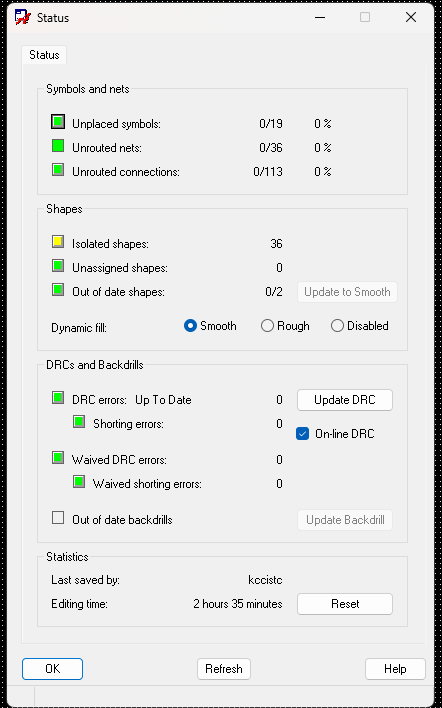

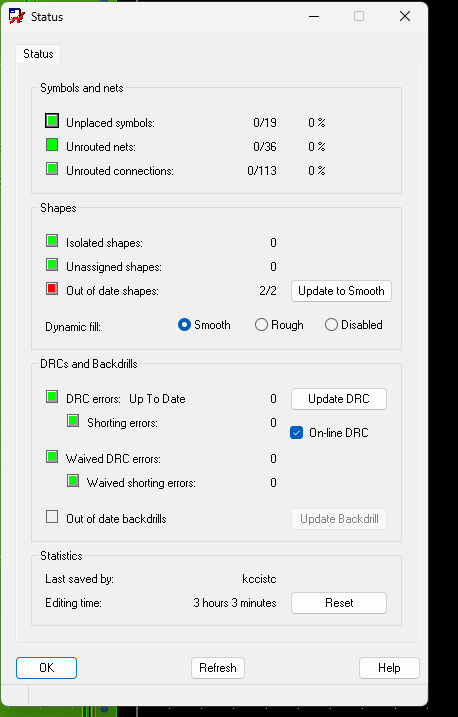

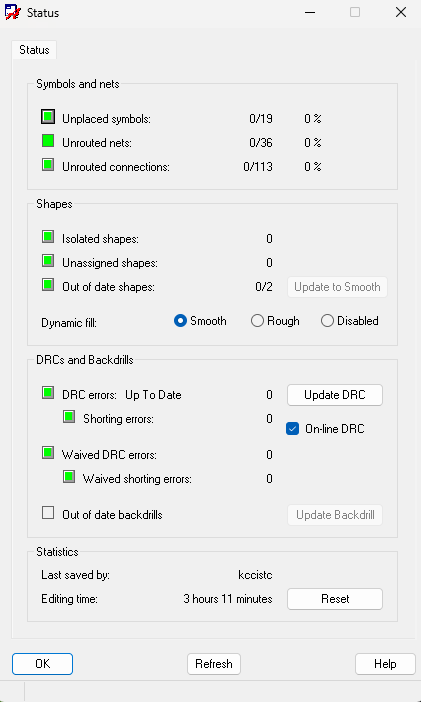

status를 확인해보면 gnd때문에 연결 안되어 있던곳이 다 연결이 되어져서 나온다

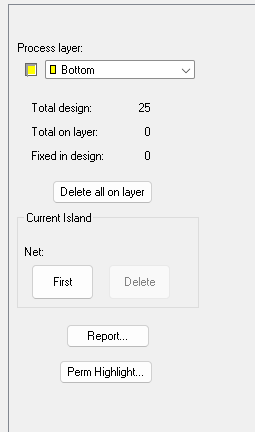

이렇게 독립되어져서 다른곳의 gnd와 연결 되지 않는 gnd가 isolated shape이다

고립된 그라운드를 bottom gnd와 via로 연결해준다

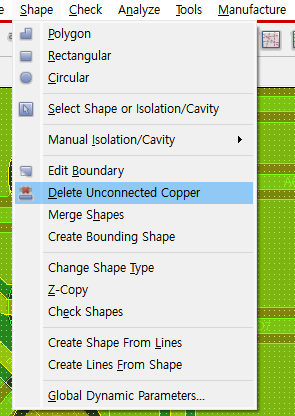

죽어있는 gnd가 나온다

delete 명령을 누르고 shapes 체크하고 gnd를 지우면 된다

gnd를 안정화 하기 위해서 (전위 레벨을 동일하게 하기위해서) 즉 노이즈를 안정화 하기 위해서 via를 뚫는다.

외부에 정전기가 동판으로 들어가기 때문에 외부에 gnd via를 뚫어버리면 정전기가 들어와도 gnd가 흡수한다

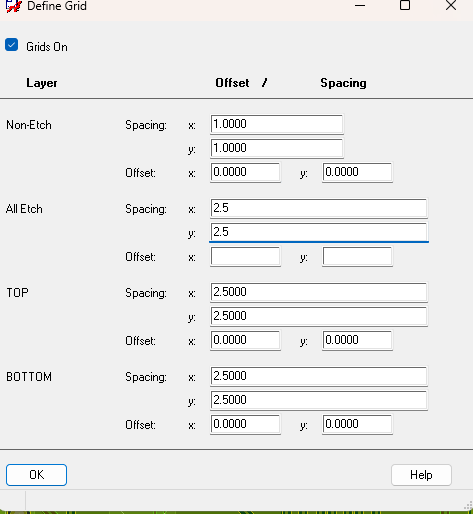

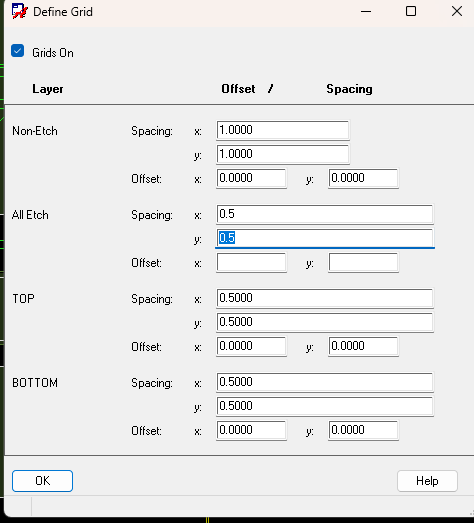

현재 grid가 0.1 이기 때문에 grid를 바꿔주어야한다

5mm간격으로 via를 넣어준다

이렇게 하면 정전기가 타고 들어와도 gnd로 흡수를 해준다

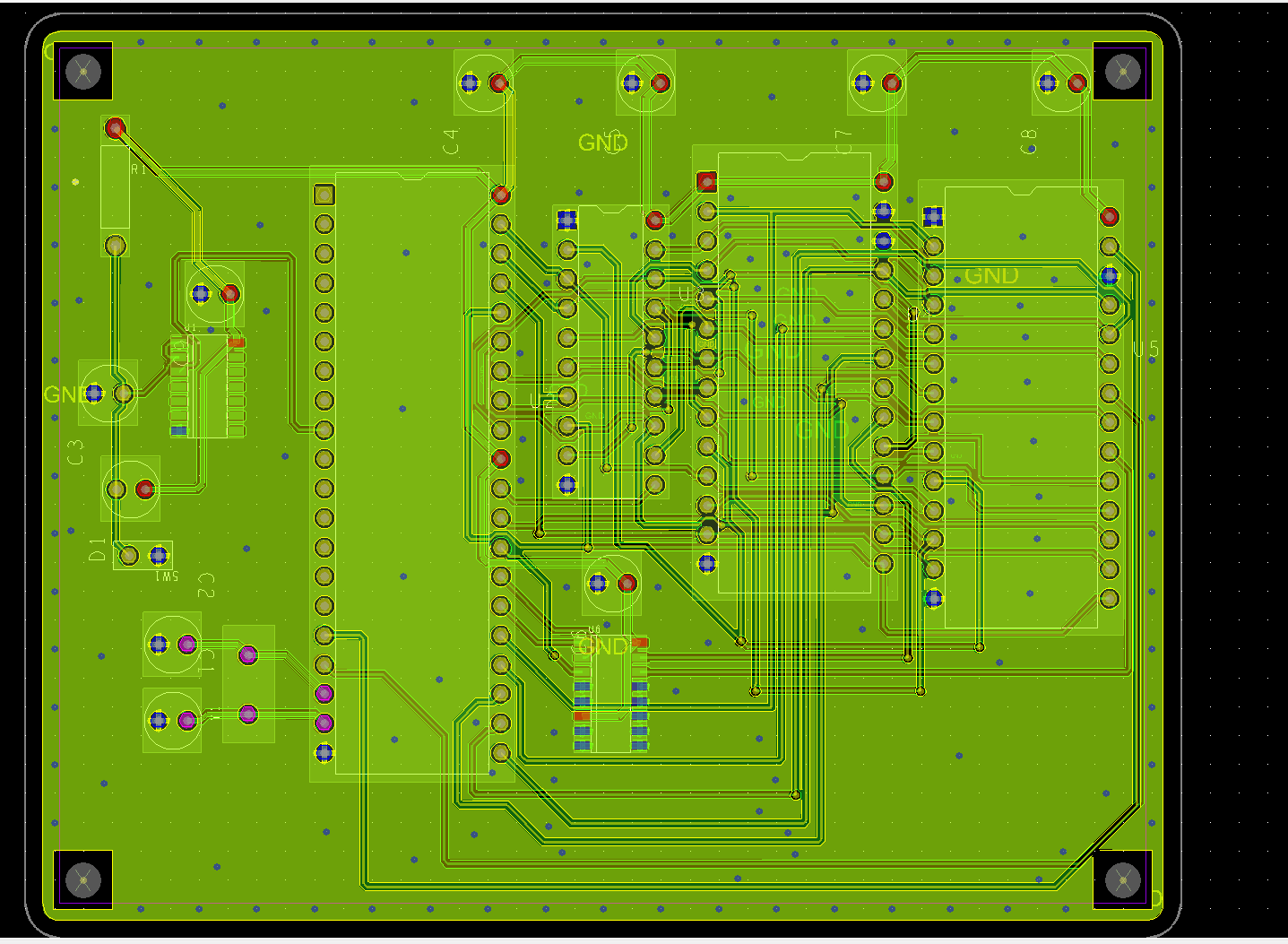

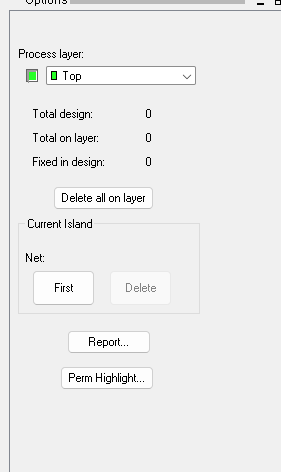

이렇게 하면 isolated gnd가 다 삭제가 되어있는 것을 볼 수 있다

update to Smooth를 클릭하면

이렇게 나오게 된다

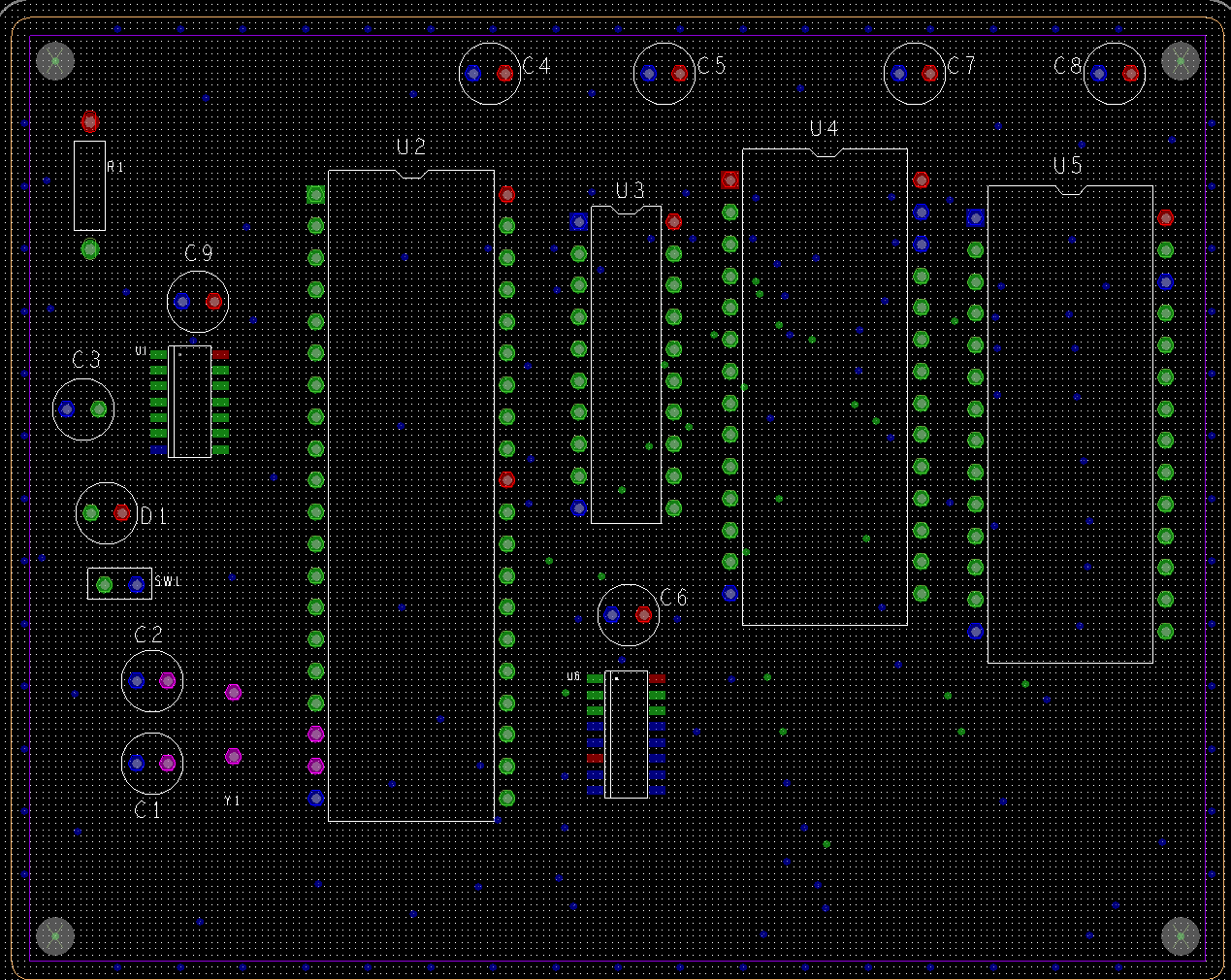

silk 정리를 위한 display 변경

etch를 꺼서 psr을 다 없앤다

그후 grid를 0.5로 바꾼다

move커서를 클릭하고 option ->find에서 texts만 클릭하여 옮겨준다

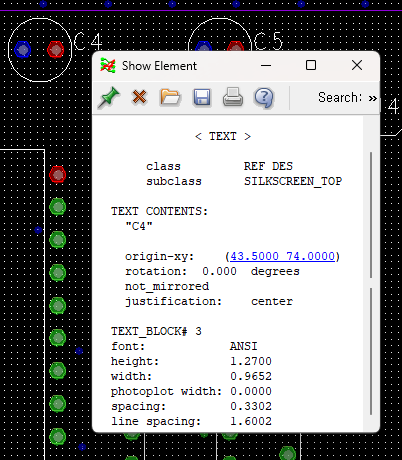

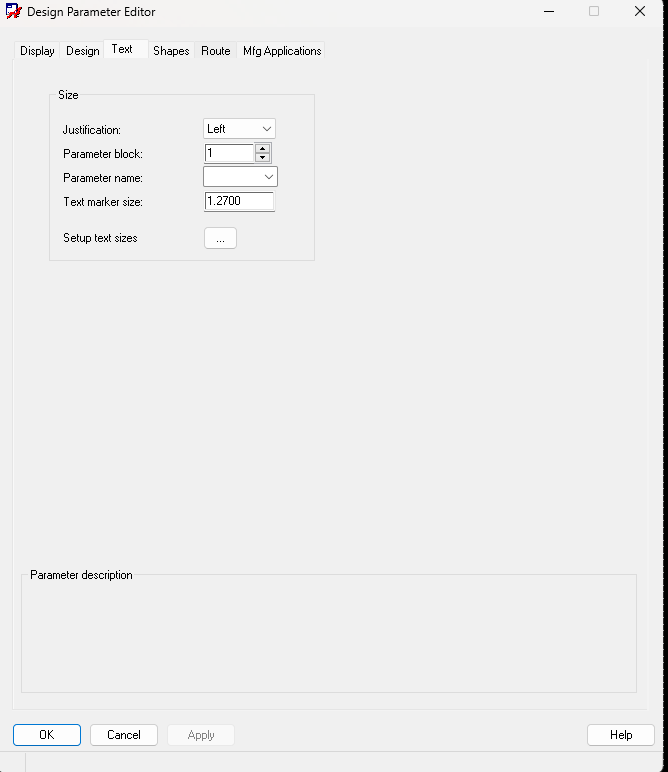

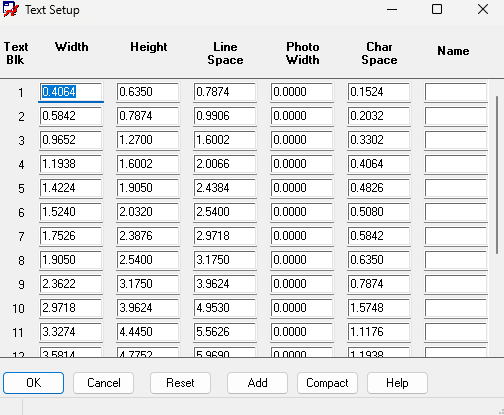

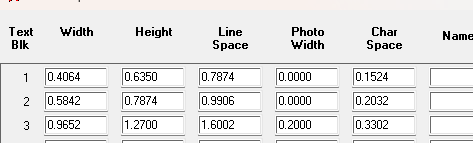

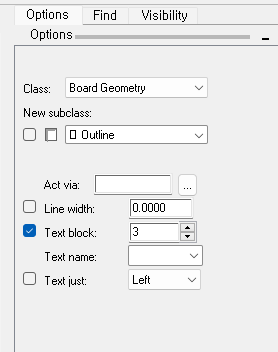

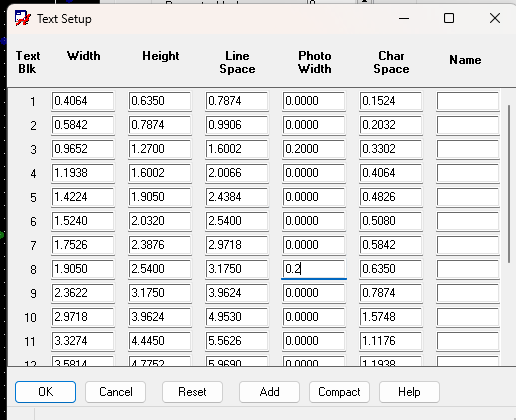

Silk Text 정보 확인 및 크기 및 Photo Width 변경

text의 정보가 나오게 된다

photo width 를 0.2로 바꿔준다

이렇게 설정하고 작은 text를 클릭 해주면

다시 커지게 된다

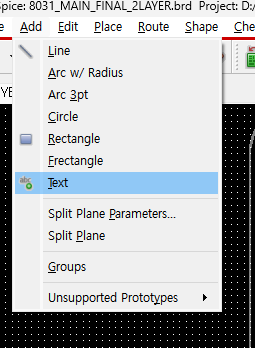

Silk Text추가

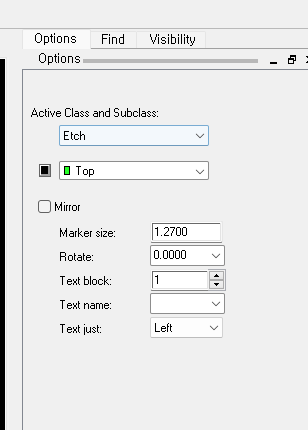

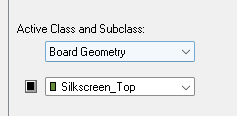

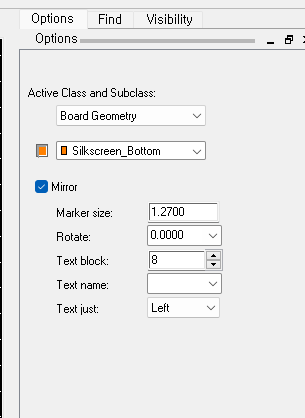

Add->Text를 클릭하고 options을 확인한다

8번으로 사용할 예정이다

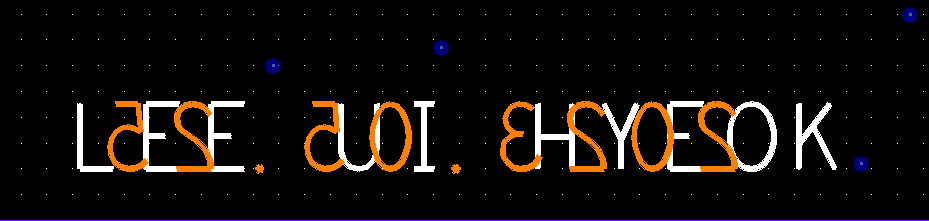

BOTTOM에 적을 때는 Mirror를 check해주어야 한다

TOP면에는 이름 BOTTOM면에는 날짜를 적어준다

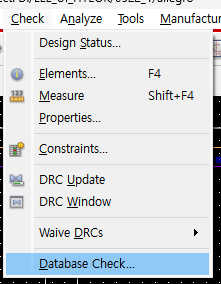

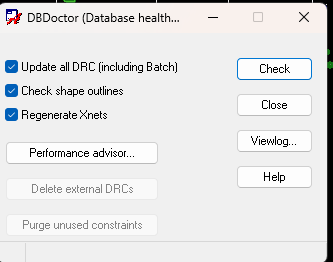

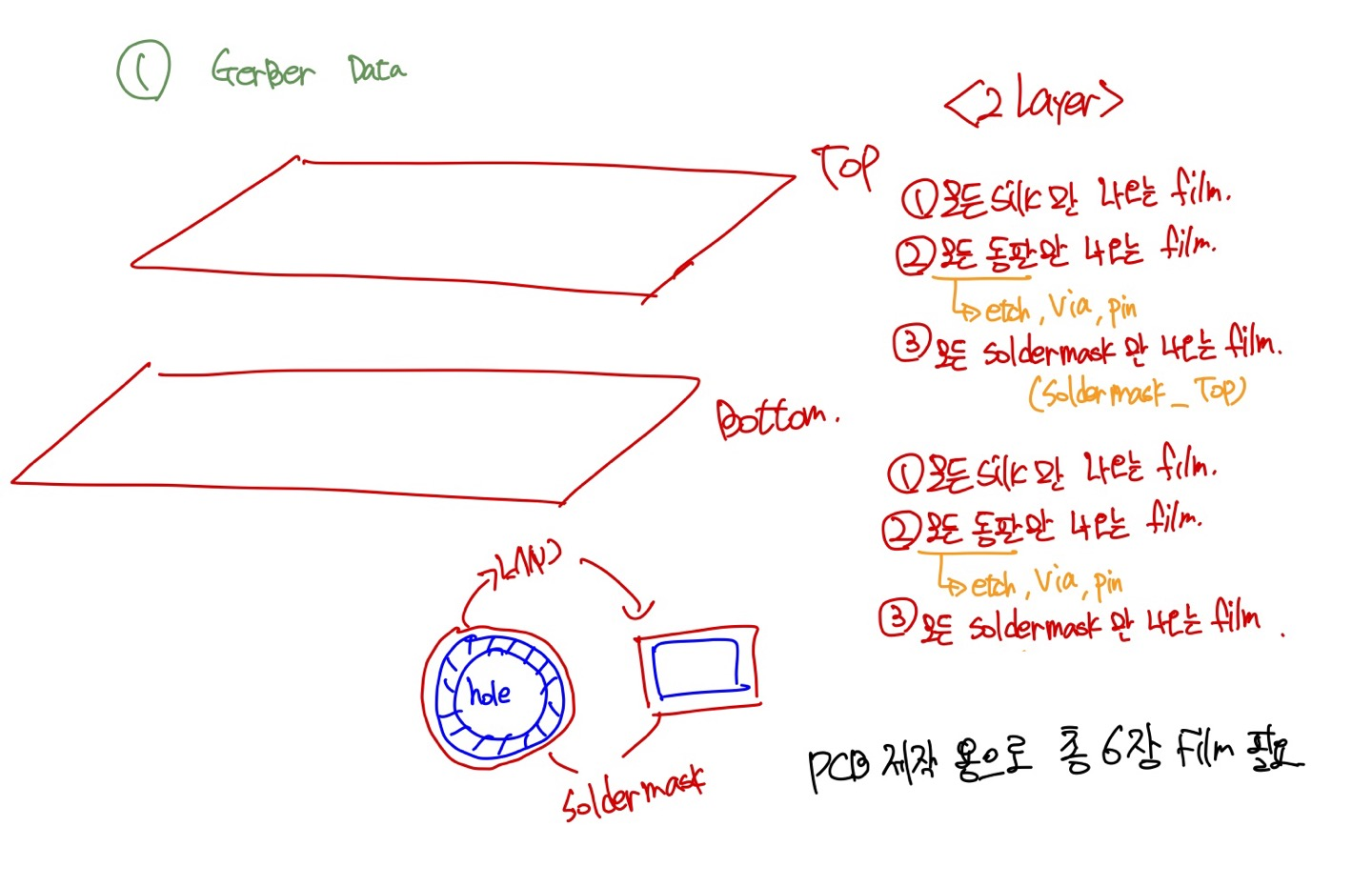

마지막 확인

error가 없는 것을 볼 수 있다

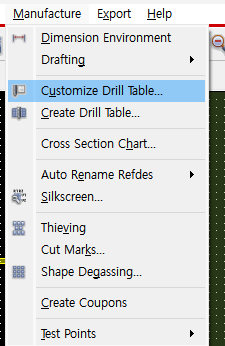

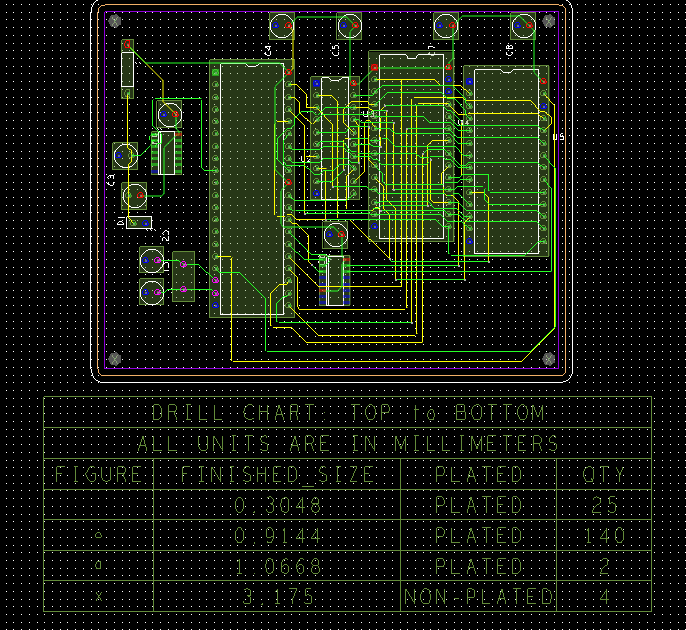

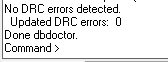

Gerber Data 생성

TOP면 FILIM

-top면에 존재하는 모든 silk film (silk screen_top)

-top면에 존재하는 모든 동판만 나오는 film (etch, via, 부품의 pin0

-top면에 존재하는 모든 soldermask만 나오는 film (land보다 0.1mm큰게 있음 -> 그게 soldermask라는 속성 -> 동판을 보호하기 위해 psr(납땜하는 부품의 핀만 빼고 다 덮음)이 덮어지는데 soldermask가 있으면 psr이 들어가지 못한다 -> psr이 도포 되지않게 하는 영역)

BOTTOM면 FILIM

-bottom면에 존재하는 모든 silk film (silk screen_top)

-bottom면에 존재하는 모든 동판만 나오는 film (etch, via, 부품의 pin0

-bottom면에 존재하는 모든 soldermask만 나오는 film (land보다 0.1mm큰게 있음 -> 그게 soldermask라는 속성 -> 동판을 보호하기 위해 psr(납땜하는 부품의 핀만 빼고 다 덮음)이 덮어지는데 soldermask가 있으면 psr이 들어가지 못한다 -> psr이 도포 되지않게 하는 영역)

=> 양변 pcb를 보내줄 기업에 보내줄 때는 총 6장을 보내줘야한다

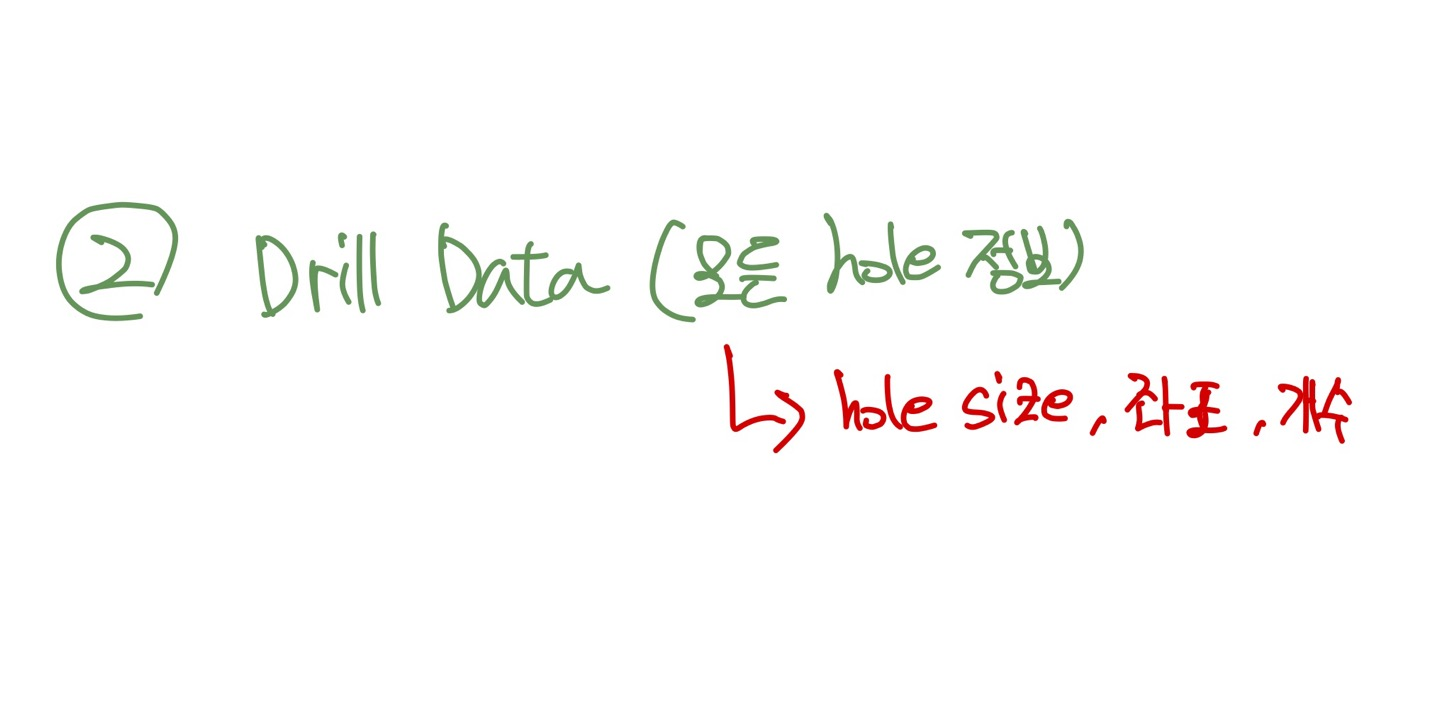

Drill data

모든 홀 정보를 보내줘야한다 (size, 좌표, 갯수)