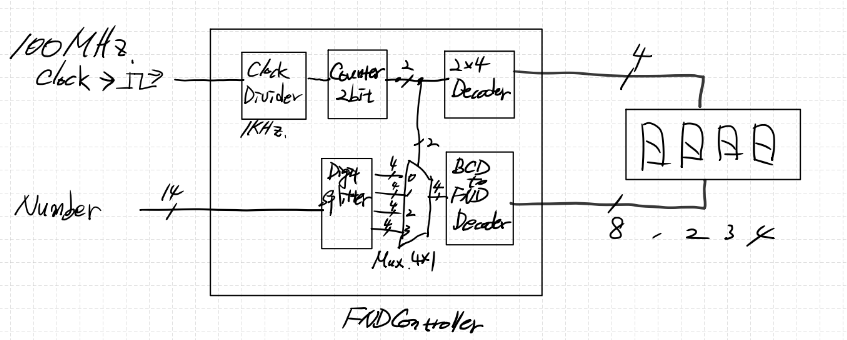

카운터 쓰는 법

reg ~~

always @ (posedge clk, posedge rst) begin

if(rst) counter <= 0;

else begin

if(counter == 100_000_000-1) //1초 셀 때 (클락 주파수 만큼)

o_clk <=~o_clk;

이렇게 하면 반전이 될 때 마다 1초가 흐르기 때문에 한주기가 2초가 된다

그러므로

if(counter == 50_000_000-1)이 되어야 한다

우리는 1ms를 만들었기 때문에

if(counter == 49_999) begin

o_clk <=~o_clk;

counter <= 0;

end

else

counter <= counter + 1;

end

if문안에 판단을 하게 하고 else문에서 액션을 하게 하는게 좋다

module freqDiv(

input i_clk,

output reg o_1kHz

);

reg [15:0] o_cnt;

always @ (posedge i_clk)

begin

if(o_cnt <49_999) begin

o_cnt <= o_cnt + 1;

end

else begin

o_1kHz <= ~o_1kHz;

o_cnt <= 0;

end

end

endmodule좋지 않은 코드이다

module freqDiv(

input i_clk,

output reg o_1kHz

);

reg [15:0] o_cnt;

always @ (posedge i_clk)

begin

if(o_cnt == 49_999) begin

o_cnt <= 0;

o_1kHz <= ~o_1kHz;

end

else begin

o_cnt <= o_cnt + 1;

end

end

endmodule이렇게 완성하는게 좋다

만진집어 넣어야함

조합논리회로(Combinational Logic Circuit)

- 같은 값의 입력이 되면 출력도 항상 같은값

- 동작 time은 비동기식으로 동작한다.

- Memory 기능이 없다.

- ex) 디코더, Mux,Adder,비교기등등

순차논리회소(Sequential Logic Circuit)

- Memory기능이 있다.

- 전 입력값과 현재 입력값의 영향을 받는다.

- 동작 time은 clock을 기준으로 동기식으로 한다.

- ex)Latch,Flip_Flop

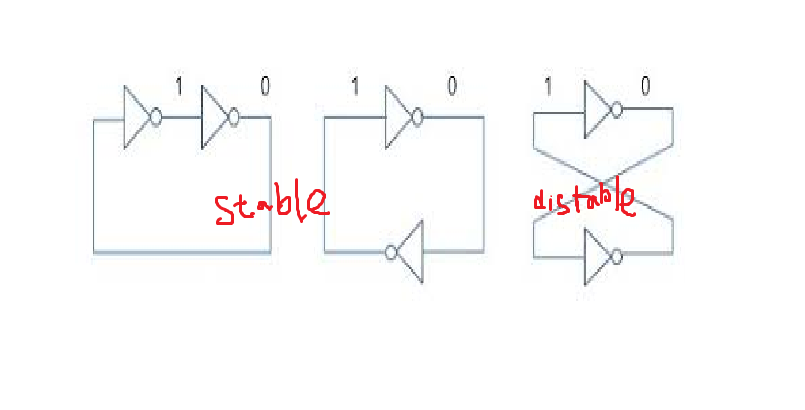

Latch

- 출력 -> 입력

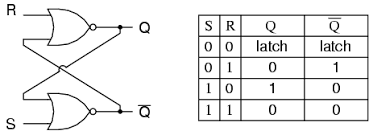

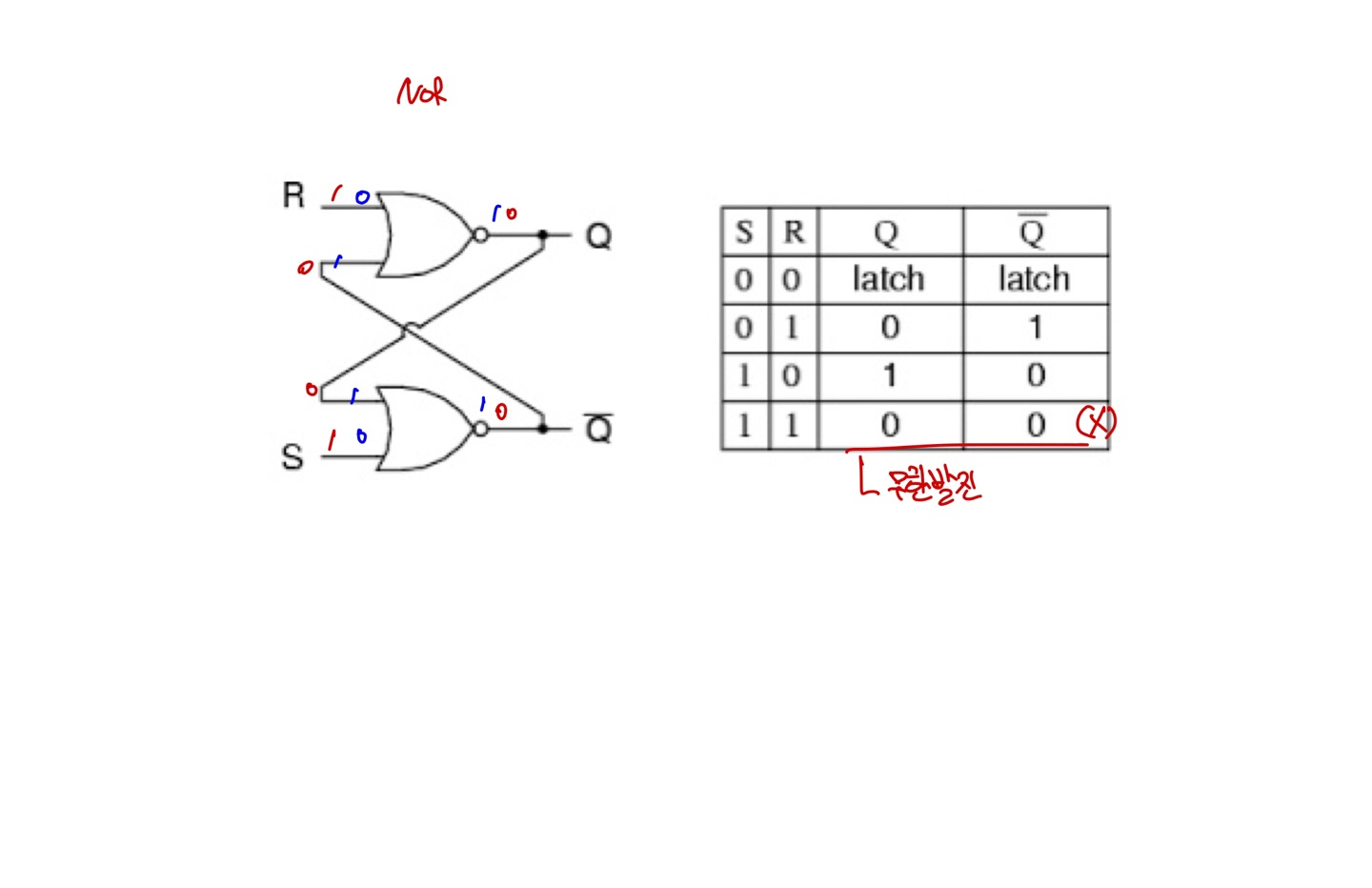

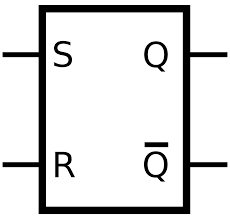

SR Latch

- 00이 들어가면 이전 값 유지

- 11이 들어가면 불능(x) -> 그 다음 입력이 00이 들어가게 되면 무한 loop에 빠지게 됌

- 메모리인 이유는 00일때 이전값을 기억하고 있기 때문에 메모리이다

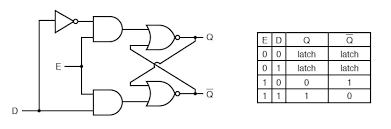

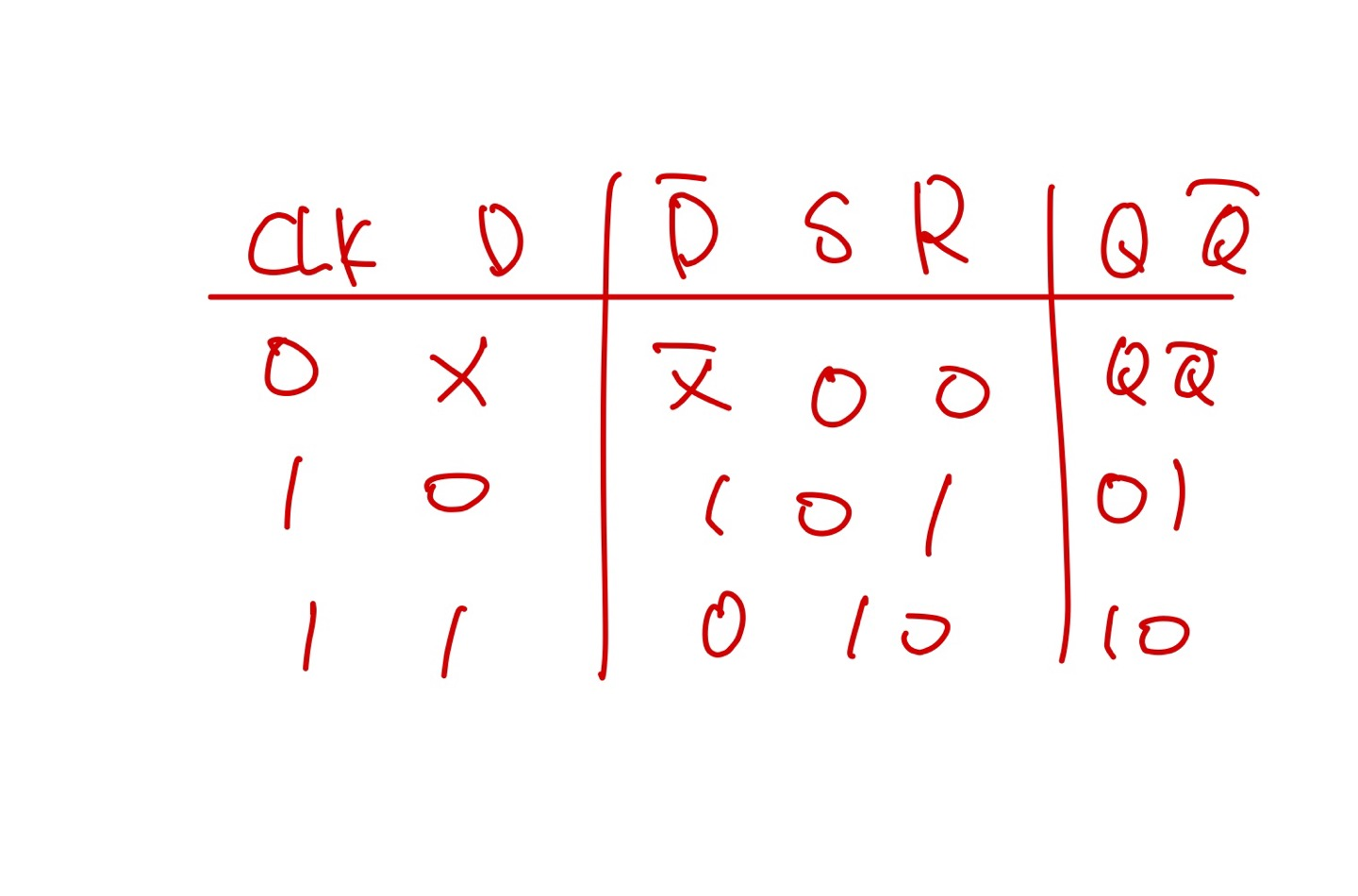

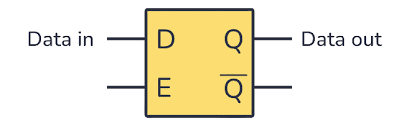

D Latch

- CLK가 0일 때는 D값이 뭐가 들어가든 이전값이 된다.

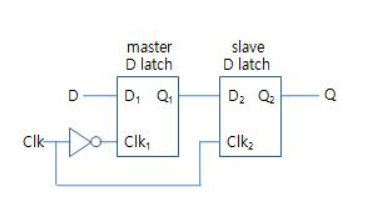

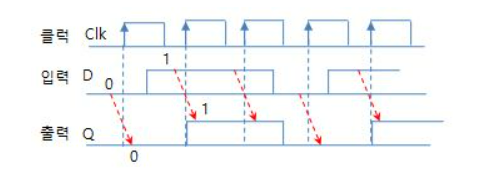

Flip-Flop

- latch는 level trigger

- f-f는 edge

-

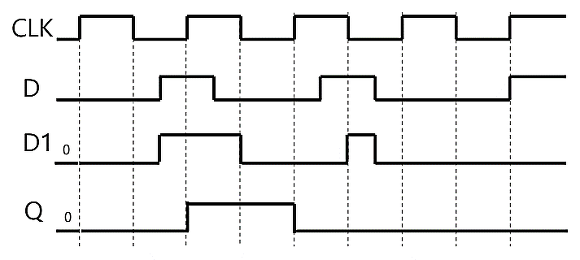

D가 입력 D1이 MASTER의 출력 Q가 SLAVE의 출력

-

Q값이랑D1값은 랫치의 출력이기 때문에 level trigger에 따라서 출력이 된다.

결과적으로 입력D와 출력Q를 비교했을 때 CLK이 rising edge일 때 변하는 것을 알 수 있다.

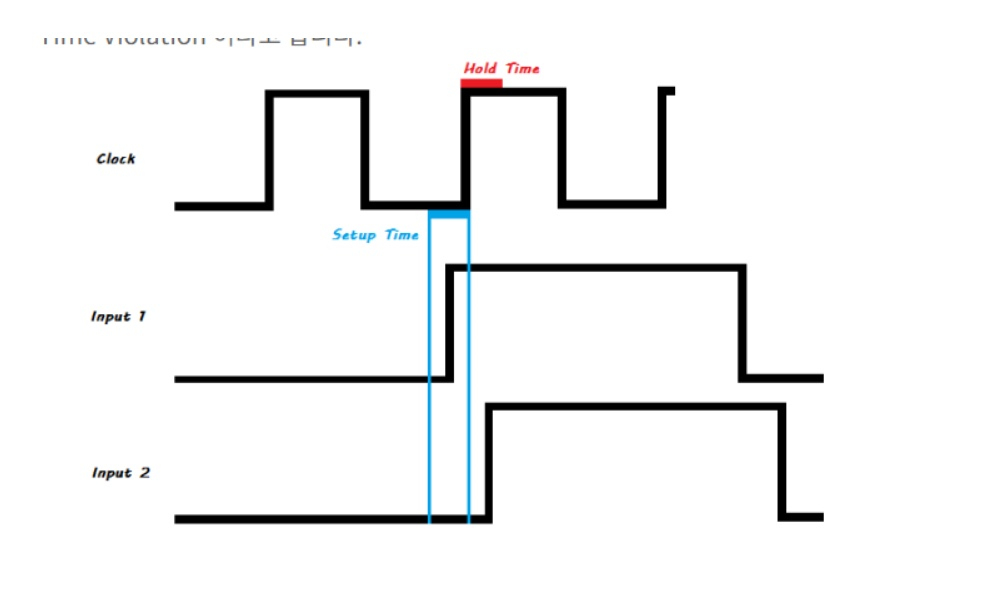

metastable

clk의 edge상태일 때 입력이 high,low 겹칠 때

setup time, hold time을 주어서 metastable상태를 방지

setup time 상승(하강)에지 전, 입력으로 받아들이는데 필요한 최소시간

hold time 상승(하강)에지 후, 출력으로 유지하기위해 필요한 최소시간

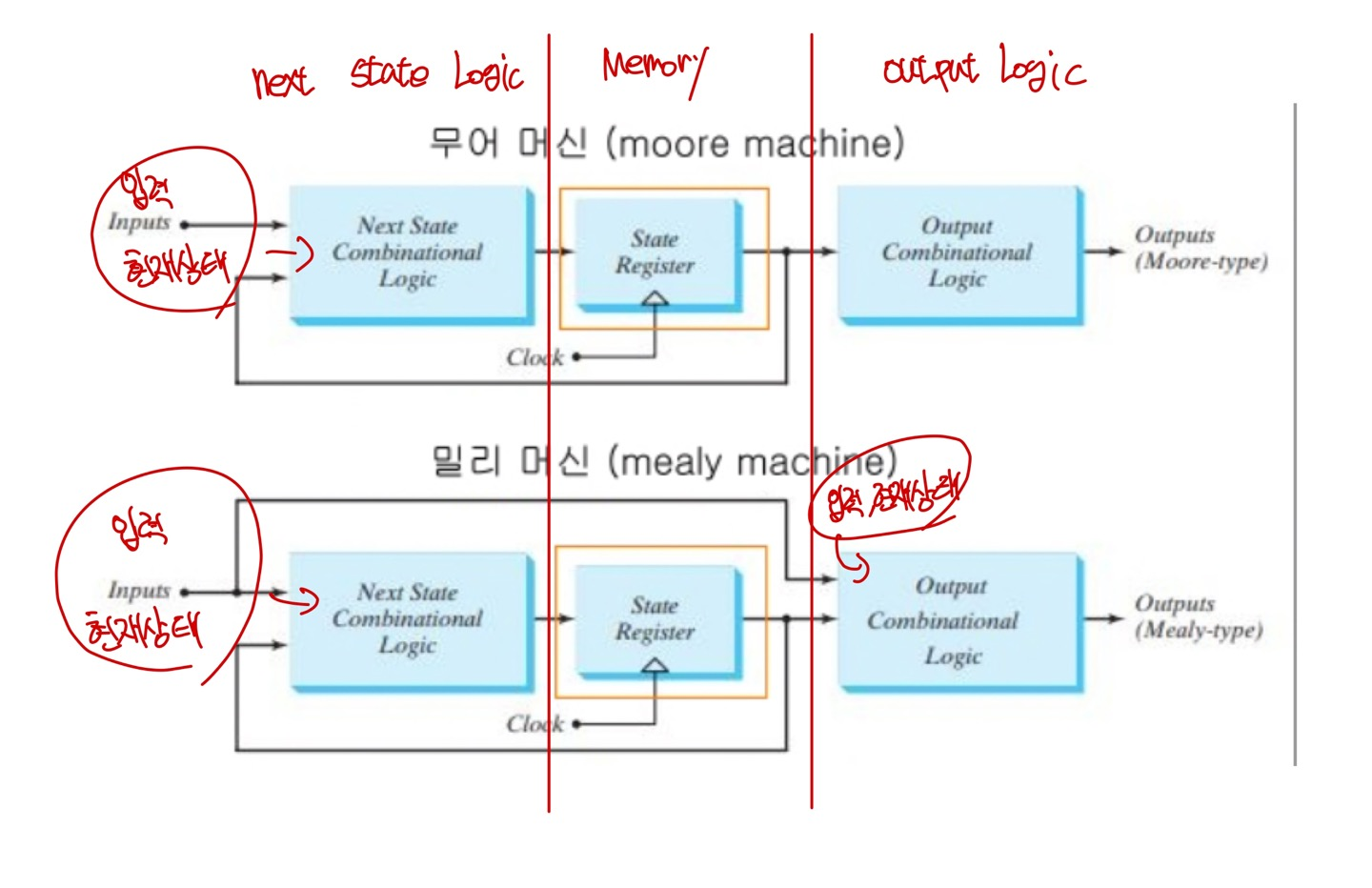

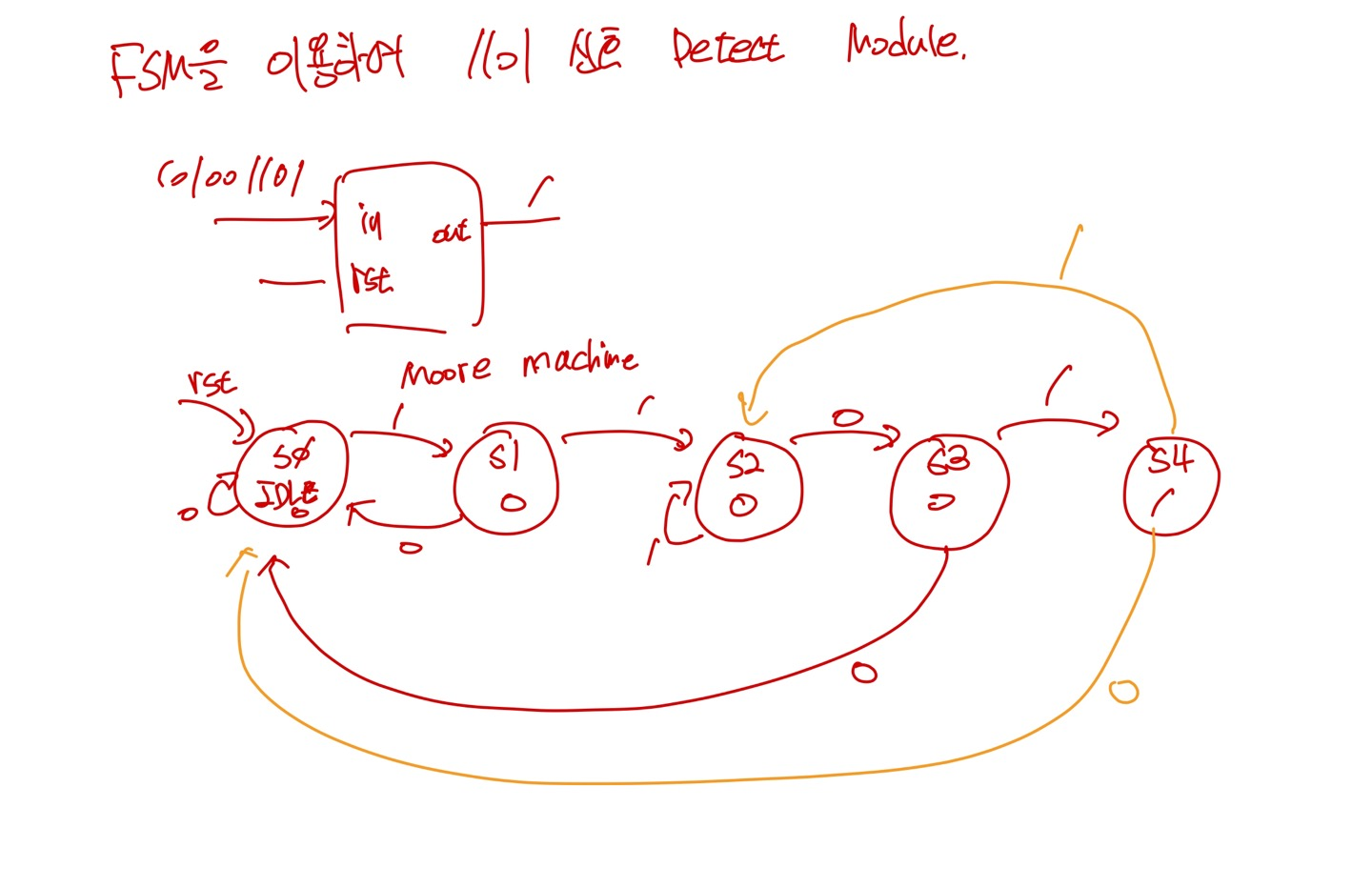

FSM

무어머신

- 입력과 현재 상태 두개가 합쳐져서 next상태에 영향을 준다.

module pattern_FSM(

input clk,

input inData,

input reset,

output outData

);

reg [2:0] curState = 3'd0,nextState;

always @ (posedge clk, posedge reset) begin

if(reset)

curState <= 3'd0;

else curState <= nextState;

end

//next state combinational logic

always @ (curState,inData) begin

case(curState)

3'd0 : begin

if(inData == 1) nextState = 3'd1;

else nextState = 3'd0;

end

3'd1 : begin

if(inData == 1) nextState = 3'd2;

else nextState = 3'd0;

end

3'd2 : begin

if(inData == 0) nextState = 3'd3;

else nextState = 3'd2;

end

3'd3 : begin

if(inData == 1) nextState = 3'd4;

else nextState = 3'd0;

end

3'd4 : begin

if(inData == 1) nextState = 3'd2;

else nextState = 3'd0;

end

default : nextState = 3'd0;

endcase

end

//output combinational logic

always @ (curState) begin

case(curState)

3'd0 : outData = 1'b0;

3'd1 : outData = 1'b0;

3'd2 : outData = 1'b0;

3'd3 : outData = 1'b0;

3'd4 : outData = 1'b1;

default : outData = 1'b0;

endcase

end

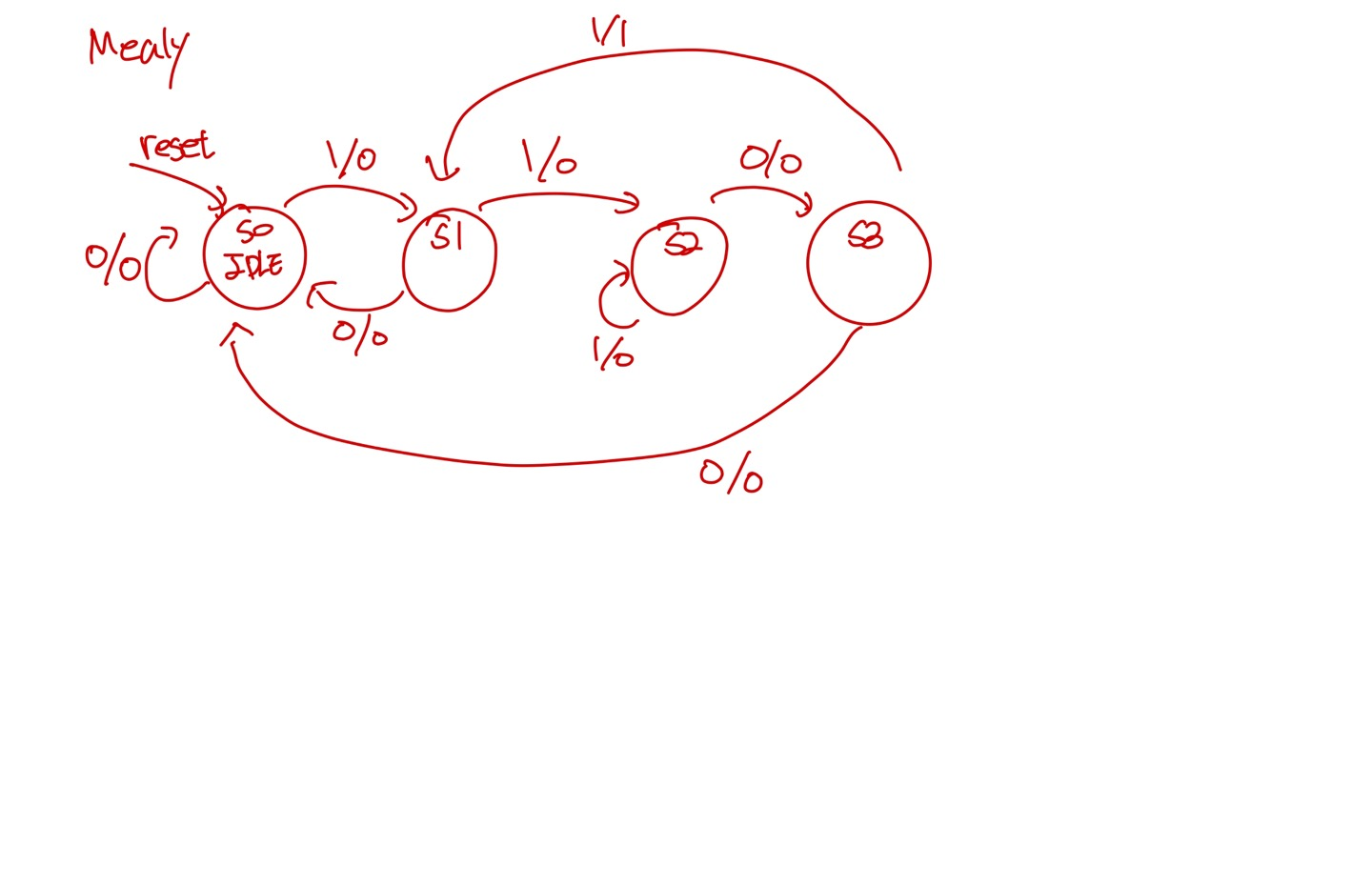

endmodule밀리머신

- 입력과 현재 상태 두개가 합쳐져서 next상태에 영향을 준다.

- 입력과 현재 상태 두개가 합쳐져서 output logic에 영향을 준다.

module pattern_FSM_Mealy(

input clk,

input reset,

input inData,

output outData

);

reg [1:0] curState = 2'd0, nextState;

always @ (posedge clk, posedge reset) begin

if(reset) curState <= 2'd0;

else curState <= nextState;

end

//nextState combinational logic

always @ (inData, curState) begin

case (curState)

2'd0 : begin

if (inData == 1'b1) nextState = 2'd1;

else nextState = 2'd0;

end

2'd1 : begin

if (inData == 1'b1) nextState = 2'd2;

else nextState = 2'd0;

end

2'd2 : begin

if (inData == 1'b0) nextState = 2'd3;

else nextState = 2'd2;

end

2'd3 : begin

if (inData == 1'b1) nextState = 2'd1;

else nextState = 2'd0;

end

default :nextState = 2'd0;

end

//output combinational logic

always @ (inData, curState) begin

case (curState)

2'd0 : begin

if (inData == 1'b1) outData = 1'd0;

else outData = 1'd0;

end

2'd1 : begin

if (inData == 1'b1) outData = 1'd0;

else nextState = 1'd0;

end

2'd2 : begin

if (inData == 1'b0) outData = 1'd0;

else outdata = 1'd0;

end

2'd3 : begin

if (inData == 1'b1) outData = 1'd1;

else outData = 1'd1;

end

default :outData = 1'd0;

end

endmodule

Register

- D-F/F의 묶음

ex) 8bit reg -> D-F/F 8개

가장 중요 (기술면접에 자주 나옴)

- time clock >= hold time + propagation delay + set up time + clock skew 이와 같이 클락을 결정

- metastable상태일 때 Q는 H/L둘다 아님 (모르는 상태)->시간이 지나면 H or L로 가게 된다

-> 해결방법: synchronizer로 만든다-> 어떻게 만드냐? -> 레지스터를 2개3개정도 serial로 만든다.