Today I learned(01/17)

Bus에 대해서...

bus = datapath

interface: 뭔가 상호작용하는 것(규격, 물리적장치, 규정, 방법이 될 수 있음)

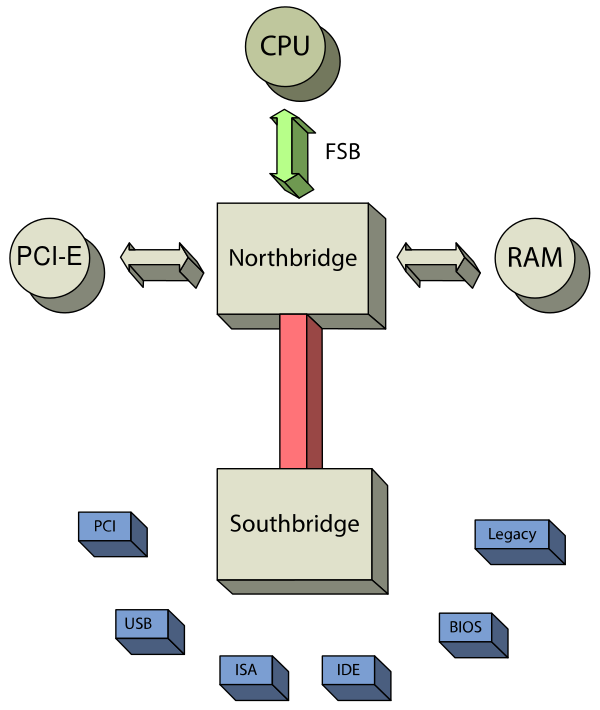

-Front Side Bus(FSB): CPU 외부에서의 접속 버스(CPU와 메모리 간, 엄밀히 말하면 CPU와 노스브릿지MCH 사이, CPU와 MCH간의 전송속도를 얘기하기도 함-ex. 대역폭400MHz)

노스브릿지(Memory Controller Hub):

일반적으로 CPU, RAM, BIOS-ROM, PCIe, Graphic Card, 그리고 사우스브리지(southbridge) 사이의 통신을 관장하는 IC칩, CPU의 고속화에 비해 주변장치의 클럭 속도가 따라가지 못하여 CPU에서 분리되어 나왔다. 최신의 CPU들은 다시 MCH를 내부에 내장하기 시작한 것도 있다. -Wikipedia-

사우스브릿지:

컴퓨터에 부착된 각각의 장치와의 입출력을 담당하는 IC칩. 인텔 칩셋을 갖춘 시스템에서는 입출력 컨트롤러 허브(I/O Controller Hub, ICH)라고 부르며, AMD의 경우 (AMD 퓨전 도입 이후) 퓨전 컨트롤러 허브(Fusion Controller Hub)로 부른다. -Wikipedia-

DMI(Direct Media Interface): 인텔이 개발한 인텔 노스브리지와 사우스브리지간의 상호 연결을 위한 점대점 인터페이스

-Back Side Bus(BSB): CPU 내부에서의 접속 버스(core와 L2 cache 간)

같이 읽으면 좋은 자료

https://blog.naver.com/lucky777a/100045967130

양자컴퓨터

TR(트랜지스터) 기반 logic대신 양자 사용

IBM Q

https://research.ibm.com/quantum-computing

상용화 by D-Wave systems

일단 나중에 공부하기로...

CPU

CISC 기반 cpu: x86, AMD(x86에서 확장) -> 보통 고성능 컴퓨터

RISC 기반 cpu: ARM -> 보통 모바일/임베디드

싱글코어의 한계(온도, 전력 문제) -> 멀티코어, 멀티코어도 한계...

메모리 장벽은 HBM으로 해결 가능? 병렬 프로그래밍은 개발자의 몫

CPU와 GPU를 하나의 칩에 같이 넣어 설계하는 APU도 있음

CPU die photo도 같이 보면 좋음

같이 읽으면 좋은 자료

https://velog.io/@jinh2352/%EB%A9%80%ED%8B%B0%EC%BD%94%EC%96%B4-%ED%98%81%EB%AA%85-%EC%B9%A9-%EB%A9%80%ED%8B%B0%ED%94%84%EB%A1%9C%EC%84%B8%EC%84%9C

https://velog.io/@jinh2352/%EB%A9%80%ED%8B%B0%EC%BD%94%EC%96%B4-%ED%98%81%EB%AA%85-%EB%A9%80%ED%8B%B0%EC%BD%94%EC%96%B4-%EA%B5%AC%EC%84%B1-%EB%B0%A9%EC%8B%9D%EA%B3%BC-%ED%95%9C%EA%B3%84

컴퓨터 사양

1. Process Technology

2. Architecture

3. 코어의 수

4. Thread의 수

5. 프로세서 기본 주파수

6. 최대 터보 주파수

7. 캐시

8. 버스 속도

9. TDP

https://m.blog.naver.com/PostView.naver?isHttpsRedirect=true&blogId=techref&logNo=222246966805

GPU

그래픽 처리 알고리즘은 행렬/벡터가 주가 된다

pixel 하나하나가 모여 큰 matrix 형태

GPU 구조는 이런 행렬/벡터 연산을 빠르게 병렬처리할 수 있는 구조

GPGPU란 것도 있다...(ex.NVIDA CUDA, Deep learning에 활용?)