이 포스팅은 숙명여자대학교 김윤진 교수님의 컴퓨터 구조론 특강을 바탕으로 작성되었습니다. 교수님께서 주신 인사이트를 제 언어로 정리한 포스팅입니다. 일부 강의 자료의 원본을 구글링 하다가 찾아서 그냥 올립니다 ^^

이 포스팅에서 설명하고자 하는 것

- 1bit를 저장하는 메모리 채택의 변화 (추상적임)

- Flip-flop의 동작 원리를 Latch와 Clock을 도입하여 설명하려고 합니다

Storage

먼저, Storage는 왜 필요한가?

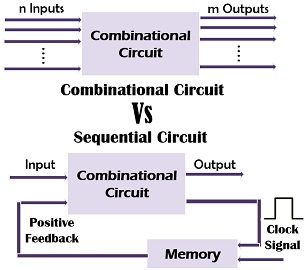

위 그림의 Combinational Circuit과 Sequential Circuit는 디지털 논리 회로에서 배웠다.

Combinational Circuit는 input만 알면 output을 확신할 수 있는 반면, Sequential Circuit는 input을 알아도 output을 확신할 수 없다. 이 회로는 과거의 input 값들을 저장하고 있다가 output을 결정할 때 사용한다. 따라서 값을 저장할 수 있는 storage가 반드시 필요하다.

값을 저장하는데 사용하는 예제

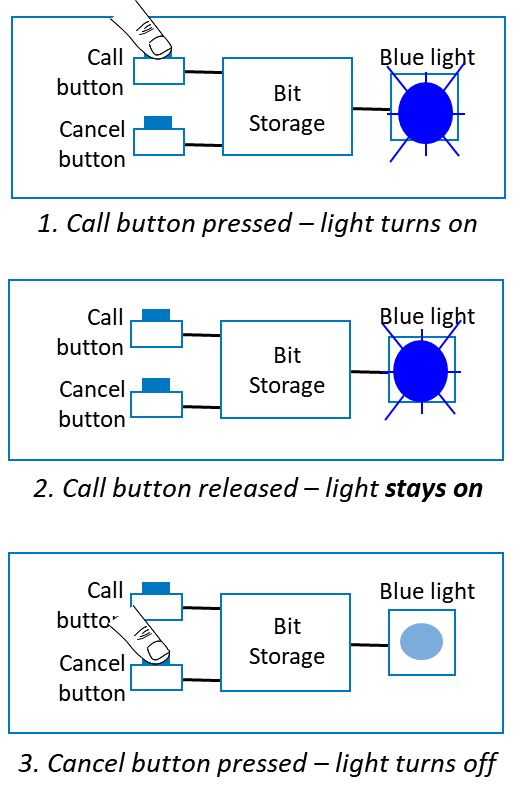

호출 버튼 예제를 사용했다. Call 버튼을 누르면 불이 켜지고, 버튼에서 손을 떼도 여전히 불이 켜져 있다. Cancel 버튼을 누르면 불이 꺼지는 기능을 가진다.

SR Latch

(사실 이 전에 단순한 로직들을 연결해보는 시도들이 있는데.. 내용을 자세하게 서술할 필요는 없다고 생각했다. 강의 내용을 다시 보니 단순함을 기반으로 하는 복잡성을 다시 발견할 수 있었다.)

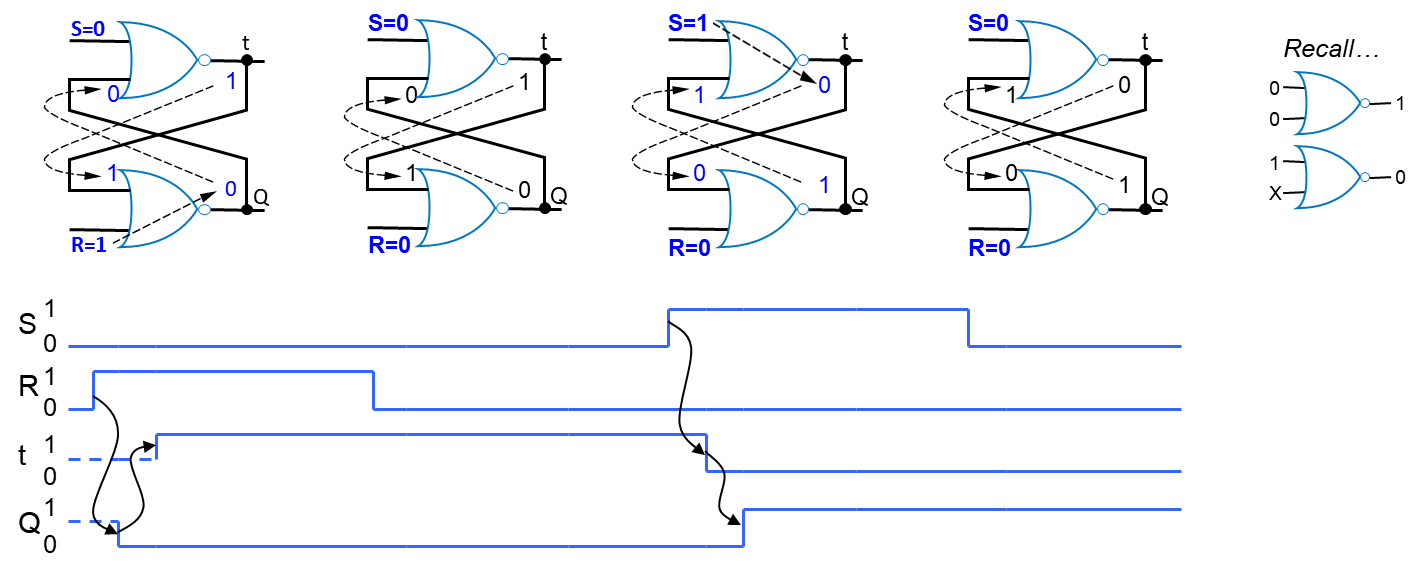

SR Latch의 진리표를 보면 이렇게 된다.

- Reset이 0→1 되면 Q는 0이 된다 (값을 초기화한다)

- Set이 0→1 되면 Q는 1이 된다 (Set 값을 저장한다)

SR Latch를 사용한 호출 버튼 구현

이제 호출 버튼의 저장 기능을 SR Latch를 사용하면 구현할 수 있다.

- Call

- Set에 1을 주면(Call Press) Q가 1이 된다

- Set이 0이 되어도(Call Release) Q는 1을 유지한다

- Cancel

- Reset에 1을 주면 Q는 0이 된다

SR Latch의 문제

하지만 SR Latch를 사용했을 때 피할 수 없는 문제가 있다. S와 R이 동시에 1이 되면 Q 값이 010101 바뀌는 것을 무한 반복한다. 이 문제를 Oscillation이라고 한다. 호출 버튼 예제에서는 Call과 Cancel 버튼을 동시에 누르는 경우이다. 무한 반복을 멈출 수 없게 되므로 전원을 차단할 때 까지 버튼은 계속 불이 깜빡깜빡 거릴 것이다. 시스템 설계는 언제나 사용자의 오용도 처리할 수 있어야 하고, 이 시스템이 단순히 호출 버튼이 아니라 미사일 발사 버튼이라면 오우.. 끔찍한 문제가 발생할 것이다. 이 문제는 필히 해결해야 한다.

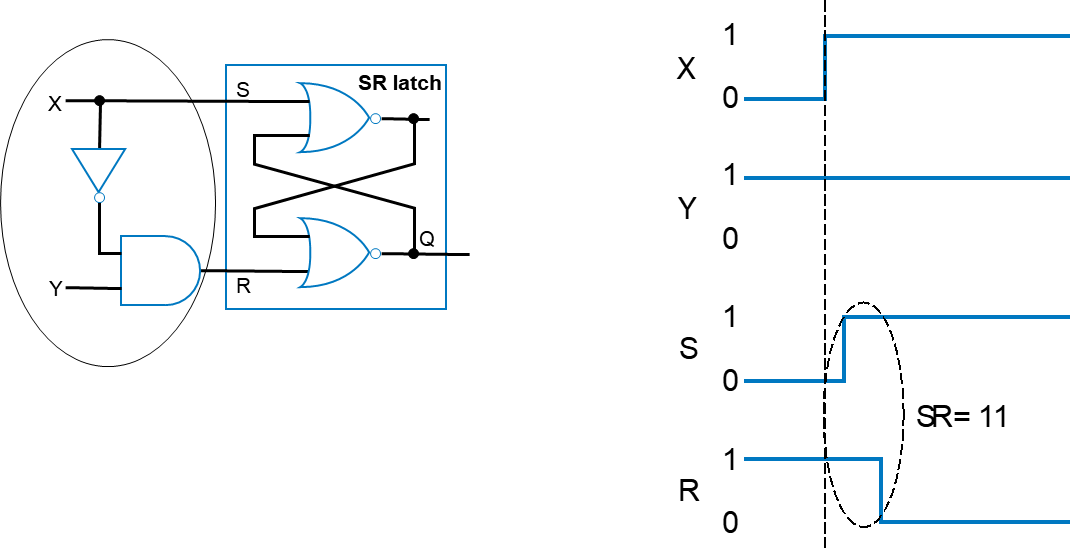

S와 R이 동시에 1이 되지 않도록 inverter와 and 게이트를 붙였다.

그러나 impulse diagram을 보면 알겠지만 하드웨어의 물리적 delay로 인해 S와 R이 동시에 1이 되는 순간이 발생한다. 찰나의 순간이겠지만.. 버튼의 회로 설계 오류로 미사일이 발사된다면?

Clock

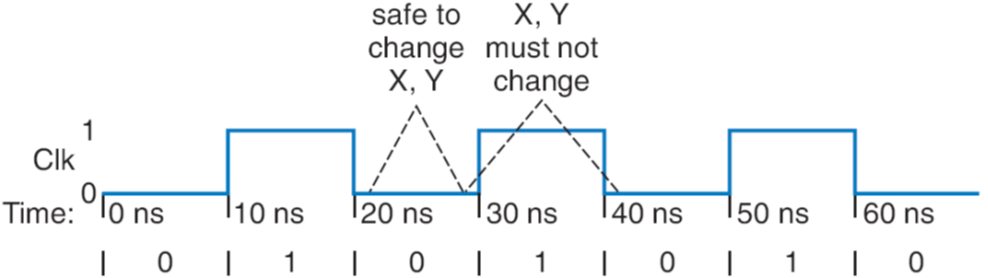

그래서 이 문제를 해결하기 위해 도입된 것이 Clock이다. 앞에서 로직 게이트를 붙였을 때는 물리적 한계 때문에 문제를 제대로 해결하지 못했다. 하지만 Clock은 또 다른 input이며, 0과 1을 일정 주기로 반복하며 값을 바꾼다. Clock이 1일 때만 input에 의미 있는 값이 실린다.

버튼 예제에 적용해보면 Clock은 SR이 둘다 1인 경우가 아닐 때까지 기다린다. 그러다 Clock이 1인 동안 S1과 R1에 값을 실어 보낸다.

Clock은 input 값이 안정화되는 것을 보고 움직이는 것이 아니다. Clock은 일정 주기로 0과 1을 반복하고, Clock이 1인 동안 input 값들이 타이밍을 맞춰서 들어간다.

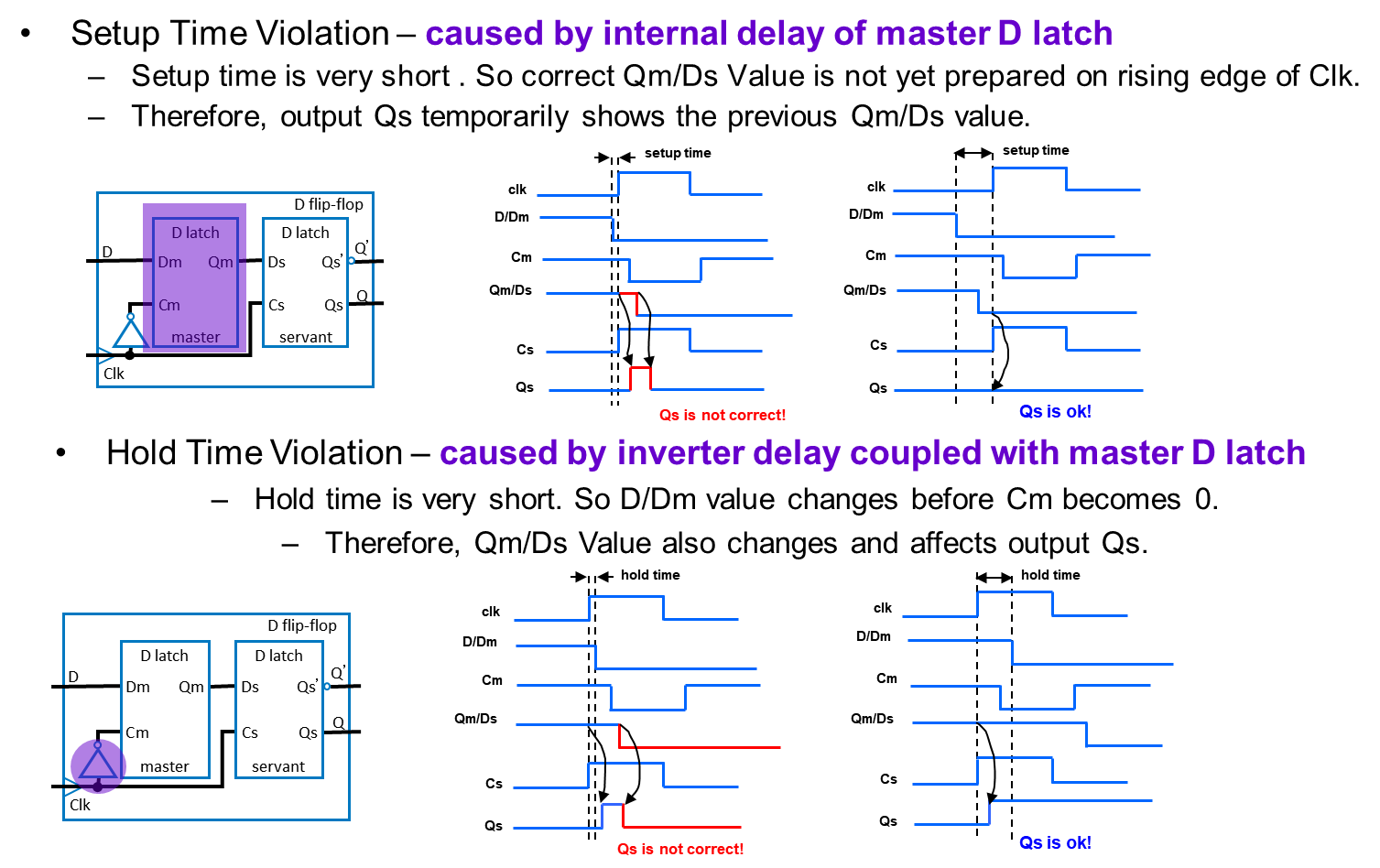

이때 input값들이 컴포넌트를 통과하는 것도 물리적 회로를 통해서기 때문에 앞에서 살펴봤던 delay가 발생한다. Flip-flop의 input을 바꿀 때, clock edge에 너무 임박해서 바꾸면 delay로 인한 오류가 발생할 수 있다. Setup Time Violation과 Hold Time Violation이 있다.

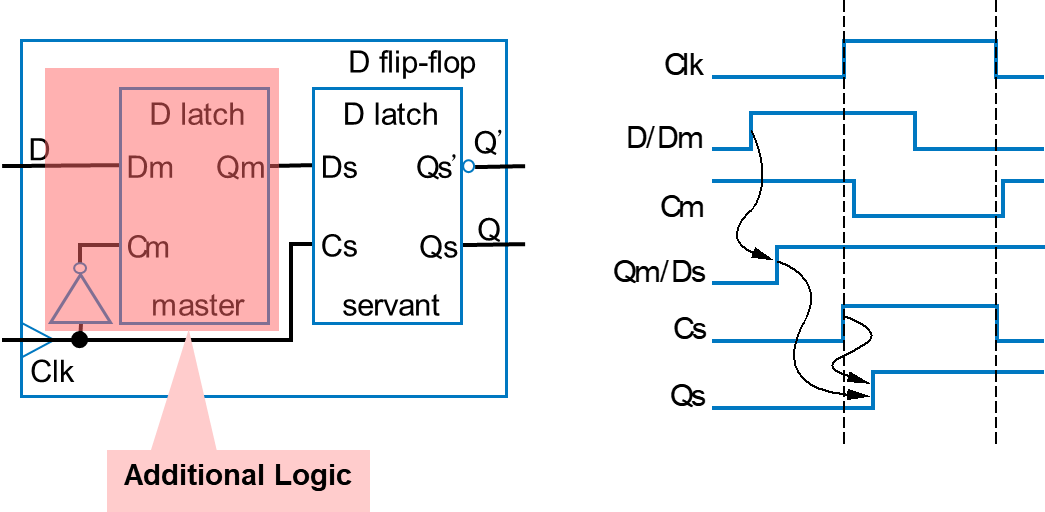

- set-up time : D는 edge 이전에 여유 시간을 가지고 바뀌어 안정되어야 한다. 위의 예에서 set-up time이 너무 짧아서, Cm이 떨어졌을 때 Ds에 Dm 값이 바로 반영되지 않았다. Qs가 1이 되는 순간이 잠깐 발생하므로 원하는 값이 반영되지 않는 순간이 발생한다.

- hold time : D는 edge 이후에 여유 시간을 가지고 안정되어야 한다. 위의 예에서 Cm이 떨어지는 것보다 Dm이 더 빨리 떨어져서, Ds에 떨어진 값이 반영되었다. 원하지 않는 값이 반영되었다.

- Set-up time과 Hold time은 짧을 수록 좋다. 빠를수록 더 빠른 clock이 들어갈 수 있기 때문이다.

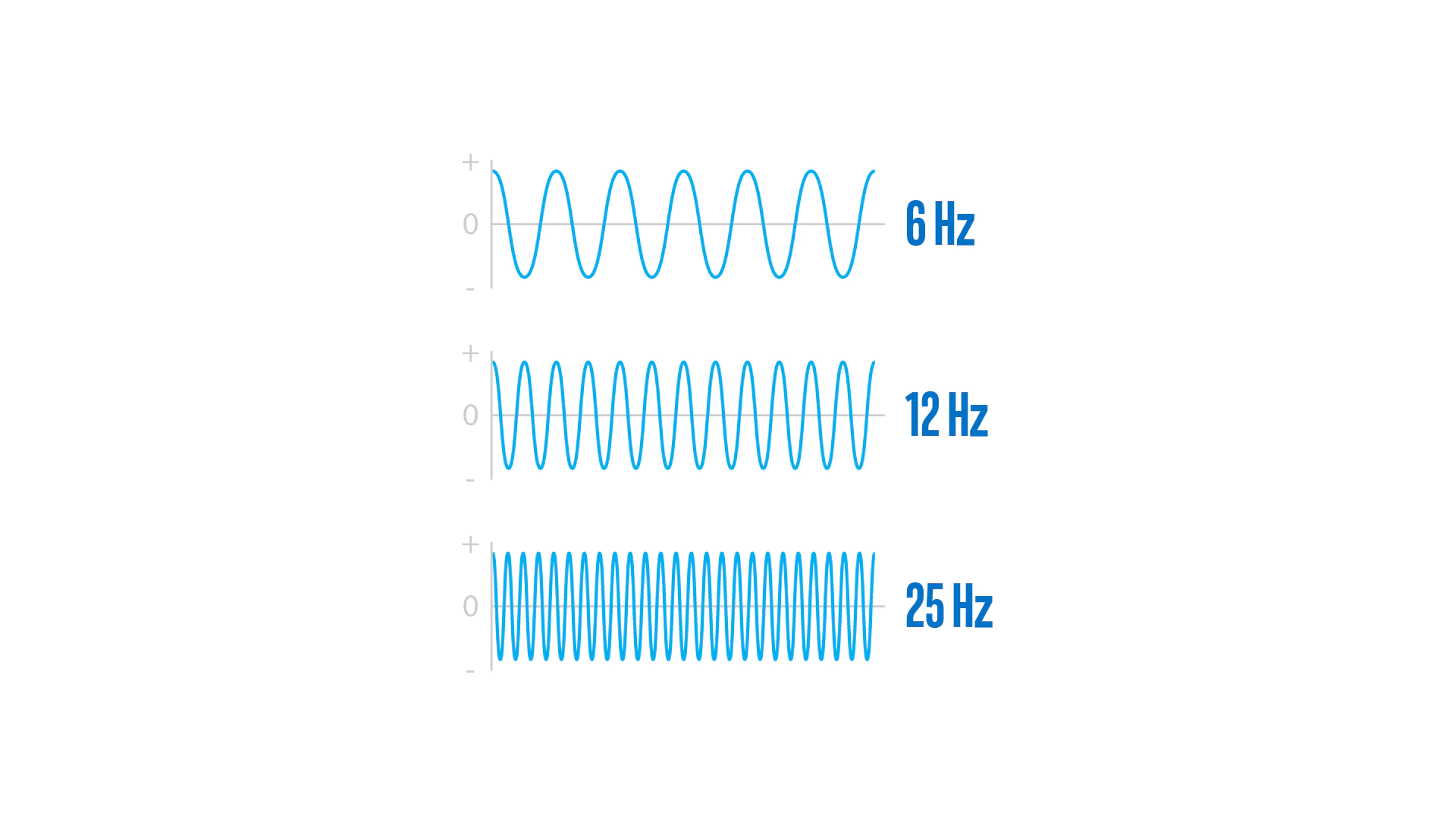

Clock Frequency

- Clock period : 한번 올라갔다가 내려가는(time interval) 시간

- Clock cycle : time interval이 몇번 반복되는지

- Clock Frequency : 1/period

Clock Frequency가 빠를 수록 더 많은 Cycle이 돈다. 클럭 속도가 3.2GHz인 CPU는 초당 32억 번의 사이클을 실행한다. 일반적으로 클럭 속도가 높을수록 CPU 속도가 빠르다. 클럭 속도가 빠르면 사이클이 많이 돌 수 있고, 연산을 할 때 input 값들이 들어가서 나오는 속도가 빠르다는 뜻이다.

SR Latch의 한계

Clock을 도입하여 SR Latch의 Oscillation 문제를 해결했음에도 SR Latch는 한계를 가진다. 1bit를 저장하는 예시는 매우 단순하기 때문에 SR Latch를 사용해도 큰 문제는 없다. 하지만 스토리지 간에 데이터 이동이나 교환이 일어나는 상황을 생각해보자. 단순히 1bit가 이동하는 경우는 없다. 더 많은 비트들을 커버할 수 있는 스토리지가 필요한데, SR Latch는 복잡한 스토리지 시스템에 사용되지 못한다.

SR Latch는 저장 기능에서 매우 훌륭한 기능을 가진 컴포넌트이다. 영원히 값을 저장할 수 있기 때문이다. 하지만 SR Latch에 너무 많은 권한을 부여했기 때문에 설계자가 제어하기 어렵다. 따라서 권한을 뺏어 설계자에게 제어권을 넘기려고 한다.

- 2개의 input을 가지면서 timeless storing capa를 가진다.

- Clk이 1이고 R이 0이면, S는 영원히 값을 저장한다.

- 컴퓨터 시스템에는 수십억개의 Latch가 들어가야 할텐데, input 값이 너무 많아지고 오류 위험도 커진다.

- Clk이 1인 시간에 의존적이다.

- 그 시간이 더 길면 많은 Latch를 통과하고, 그렇지 않으면 적은 Latch를 통과한다.

- 목표에 맞춰서 Clock을 다르게 줄 수 없다. 단위가 너무 세분화되어 복잡도를 감당할 수 없다.

Elaborate Bit Storage

앞에서 말한 SR Latch의 두 가지 한계점을 보완해 만든 스토리지를 알아본다. 한계점을 어떻게 보완했는지 하나씩 살펴보자.

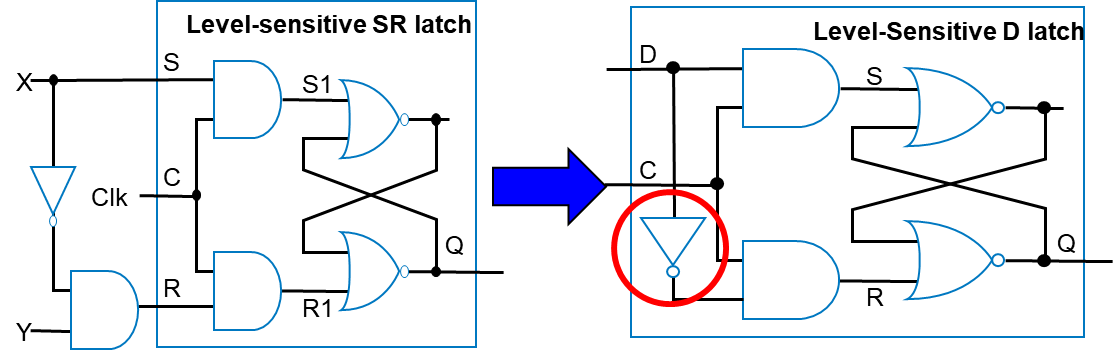

- 2개의 input을 가지면서 timeless storing capa를 가진다.

=> input은 1개, Storing Capa는 1 Cycle을 가지는 D Latch

- input이 SR 두개에서 D 한개로 바뀌었다.

- D 값이 0으로 떨어지면, inverter에 의해 Q가 reset된다.

- Clk이 1인 시간에 의존적이다.

=> Clk이 1인 동안이 아니라, 0→1 되는 순간(Clock Rising Edge)에 유효한 값을 전달하는 D Flip Flop

Additional Logic의 정체는 바로 컨버터가 붙은 D Latch이다!

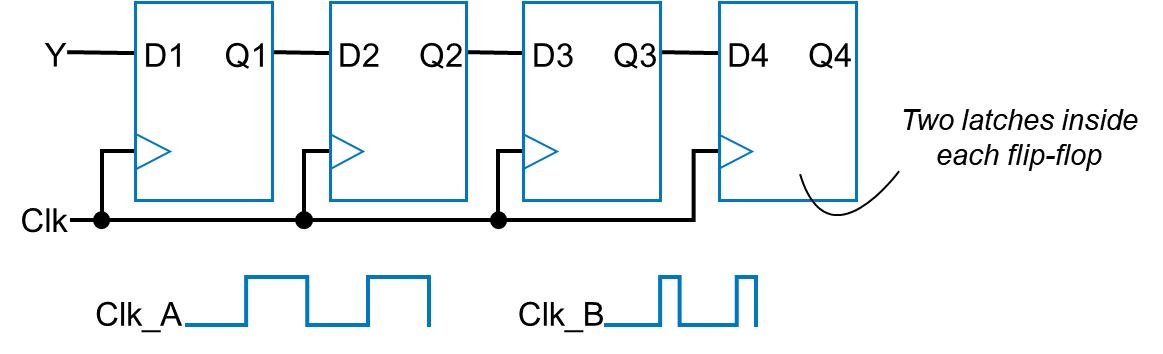

D Flip Flop은 두개의 D Latch가 붙어 만들어진다.

Additional Logic이 하는 일

- Rising edge 순간의 input value D를 저장했다가

- D의 값 변화는 상관 없이 D1에 input을 feed한다.

D Flip Flop

그리하여 1bit를 저장할 때 설계자가 제어하기 편하도록 만든 스토리지 컴포넌트인 D Flip Flop이 완성되었다! D FLip Flop을 다시 한번 정리해보자.

- input이 1개로 줄었다.

- Clock의 Rising Edge에만 값을 전달한다.

결론

내용이 상당히 많았는데, 서론에서 이 포스팅은 Flip-flop의 동작 원리를 Latch와 Clock을 도입하여 설명하기 위함이라고 했다. 지금부터 요약해서 답해보겠습니다. (요약이긴 했는데 흐름성을 강조하고 싶어서 매우 구구절절임)

SR Latch는 input인 Set이 1이 되면 그 값을 Q로 보내고, 내부적으로는 이 값을 영구적으로 유지합니다. 하지만 SR Latch는 사용자의 오용(동시에 버튼 누름)으로 인해 Oscilation 문제가 발생할 수 있는데, 이 문제를 해결하려면 S와 R이 동시에 1이 되지 않도록 막아야 합니다. 조합 로직을 붙여도 하드웨어의 delay 시간이라는 근본적인 문제 때문에 로직을 추가적으로 붙이는 방식으로는 해결할 수 없죠. 그래서 Clock이라고 하는 제 3의 input을 반강제로 도입합니다. Clock이 허락하는 경우에만 S1과 R1에 의미 있는 값이 실립니다. SR Latch의 내부 input은 Clock의 주기에 맞춰서 움직입니다. Clock이 수많은 컴포넌트 내부의 input에 다 맞춰서 움직여줄 수 없기 때문입니다. 이렇게 SR Latch가 만들어졌습니다. 1 비트를 저장하는데 더할나위 없는 컴포넌트입니다. 그럼에도 SR Latch는 여러개의 비트를 저장하는데 문제가 있습니다.

우선 input이 2개라는 점입니다. 비트 개수만큼의 SR Latch를 사용할 때 저장하고자 하는 비트가 수백개, 수천개로 늘어나면 집적도에서 문제가 발생합니다. 또 클락이 1인 시간에 의존적이게 됩니다. 1인 시간이 길면 더 많은 래치를 통과하죠. 이런 방식으로는 우리가 의도하는 속도로 데이터를 저장하기 어렵습니다. 그래서 SR Latch의 권한을 빼앗아 만든 것이 Flip Flop입니다. input을 SR 2개에서 D 1개로 줄였고, Rising edge of clock을 도입하여 클락이 1이 되는 순간에만 값이 저장되도록 합니다. 결국 Flip-flop은 input을 1개로 줄여 복잡한 비트를 저장하는 컴포넌트에서 집적도의 이점을 가져갔고, Riding edge of clock을 도입하여 데이터를 저장하는 속도를 설계자가 제한할 수 있는 통제권을 부여합니다.

이 포스팅에서는 1bit storage component의 변화와, clock을 알아보았다. Clock은 컴퓨터 시스템 성능 평가에서 워낙 중요한 요소이므로 알아두어야 하는 필수적 요소이고, 1bit storage component의 변화에서 SR Latch -> D Flip flop으로 가는 흐름에서 설계자의 통제를 위해 뛰어난 성능의 컴포넌트의 권한을 뺏고 기능을 제거하여 단순화했다. 나중에 Register File까지 살펴보면 알겠지만 이렇게 단순한 컴포넌트들을 붙여서 복잡한 단계의 컴포넌트로 도약하는 순간이 온다. 이러한 접근 방식은 HW뿐만 아니라 SW를 설계할 때도 적용되므로 앞으로 공부할 때 이런 접근들이 또 있는지 주의해보자.