✅ PCIe Lane 구조

지난번에 PCIe Generation에 대해서 찾아보다가 PCIe의 구조와 신호전달 과정에 대한 내용을 보고 궁금해져서 아래와 같이 그림으로 정리해보았다! 정확히 그림이 잘 안보이길래 여기저기서 주워온 정보를 바탕으로 그려보았다. 틀릴 수도 있다는 말이다.

PCIe는 Lane단위로 동작하는 직렬 고속 버스이다. 여기서 직렬이라는 의미는 하나의 차동 쌍(Differential Pair) 안에서 데이터를 1비트씩 순차적으로 Clock에 맞춰 보내는 방식이라는 의미이다. 즉 예를 들어서, 4개의 비트를 보낼 때, 4개의 신호선을 통해서 한번에 4비트를 보내는 것이 아니라 하나의 신호선을 이용해서 고속+연속으로 전송하는 것이다.

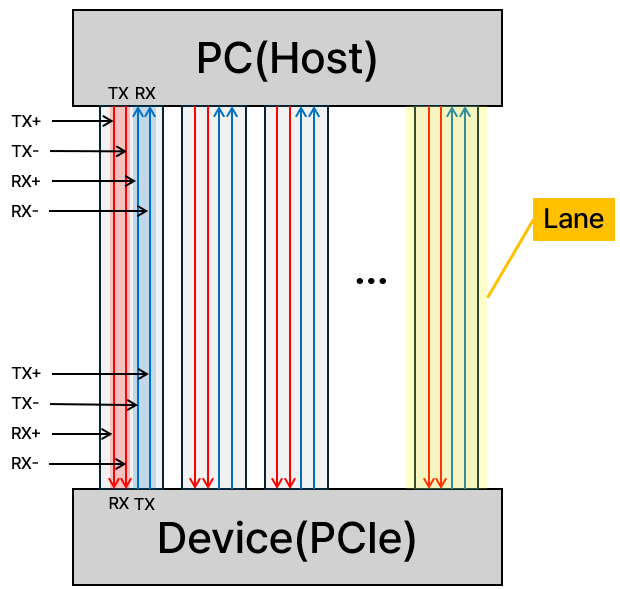

하나의 차동 쌍(Differential Pair)이라는 말이 나왔는데, 이 말은 위의 그림에서 볼 수 있듯이 TX pair와 RX pair를 의미한다. 하나의 Lane은 TX pair과 RX pair로 이루어져 있는데, TX는 송신, RX는 수신을 의미한다. 그러니까 PC의 TX와 RX가 각각 PCIe의 RX와 TX가 되는 것이다.

여기서 TX와 RX가 각각 +와 -로 차동 신호(Differential Pair)를 이루고 있는데, 이는 하나의 신호를 두 개의 선(Pair)에 서로 반대 극성으로 동시에 흘려보내는 방식이다. 즉,+선엔 신호가 +1V면, −선엔 −1V로 동일 신호를 반전하여 전송하는 것이다. 이런 방식을 사용하는 이유는 크게 1. 노이즈 제거 2.신호 품질 유지 (고속 무결성) 3. EMI (전자기파 간섭) 최소화 때문이다. 이러한 이유로 인해 고속 직렬 통신을 위한 PCIe는 반드시 차동 쌍으로 설계된다.

또한 PCIe는 한 Lane으로도 수 기가바이트 수준의 고속 직렬 전송이 가능하지만, 고해상도 GPU, 8K 비디오 스트림 처리, 대용량 고속 SSD 등에서는 한 Lane에서 처리할 수 없는 데이터의 수송신이 필요하므로 더 큰 대역폭이 필요하다. 이런 경우는 Lane 수를 늘려 대역폭을 선형으로 확장하게 되며 각 Lane은 병렬로 연결되게 된다. 표기는 x1, x4, x8, x16과 같이 표기한다.

✅ 의문점들

위에 내용을 적으면서 궁금했던 몇가지 의문점과 답을 정리하면 아래와 같다!

근데 병렬 버스 방식 처럼 신호선을 여러개 만들고 한번에 쫙 보내면 좋은거 아니야?

찾아보니 각 선의 길이를 나노초 단위까지 동일하게 맞춰야 하기 때문에 설계가 매우 어렵고 비용이 비싸다고 한다. 또한 선이 많아지면 Crosstalk(간섭화)가 많아지는 문제도 있어서 SATA, PCIe등 현대의 버스들은 모두 고속 직렬 방식을 사용한다고 한다. 이 때, 고속 직렬 버스에서 더 큰 대역폭이 필요한 경우는 Lane 수를 늘려 여러 직렬 경로를 병렬로 묶음(Lane) 으로 확장하는 방식을 사용한다.

고속 직렬 버스에서 Lane 수를 늘리는 것이나, 병렬 버스에서 신호선을 늘리는 것이나 똑같은거 아닌가?

이것도 알아보았는데, 위에서 적은 것처럼 병렬 버스는 같은 길이로 선을 맞추고 정밀하게 클럭을 맞추고 하는 등 물리적인 한계점이 생긴다면 Lane 기반 직렬 병렬 구조는 Lane을 늘려도 그런 문제들이 없었다. 대역폭을 늘리기 위해서 Lane의 수를 늘린다고 해도 Lane끼리는 독립된 신호들이라 동기화도 필요없고 간섭화 문제도 없다. 또한 클럭에 어떤 문제가 생긴다 해도 각 Lane은 자체 클럭 복구 기술(Clock Data Recovery, CDR)로 독립 전송을 하기 때문에 단순하게 Lane의 수를 늘리면 대역폭의 선형 확장도 가능하고 고속 전송도 유지되면서 설계까지 간단하게 이루어지는 것이다!