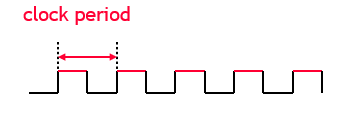

Clock

Clock 은 0과 1이 반복되는 signal이다.

Clock period의 역수는 진동수이고 단위는 헤르즈 hertz사용한다.

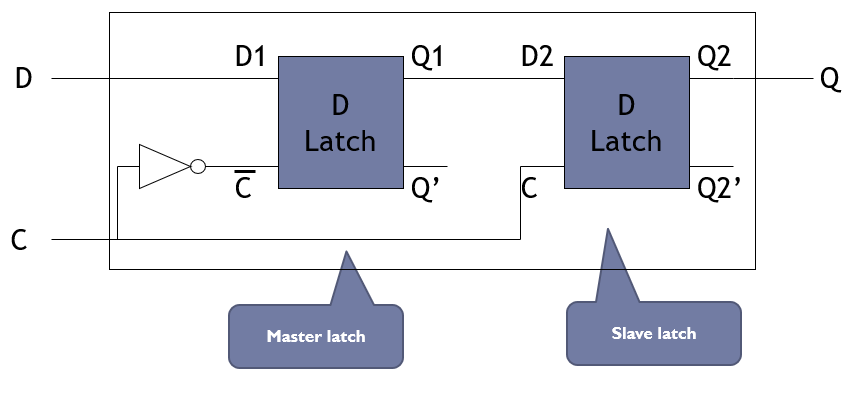

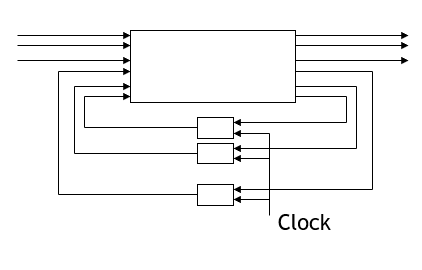

D Flip-flop

D flip-flop은 D Latch 2개를 이용해 구현한다.

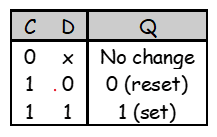

D Latch와 달리 D Flip-flop은 입력D가 아닌 C(clock)에 반응해서 출력이 변한다.

C=0

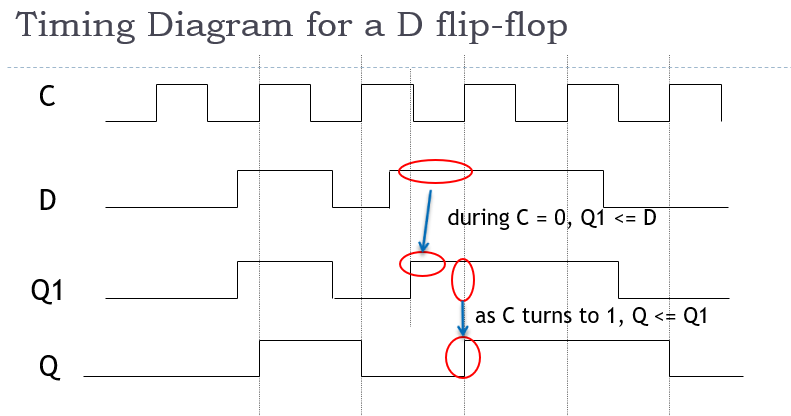

C=0일때

첫번째 Latch는 D를 출력에 전달하고 두번째 Latch는 현재의 state를 유지한다.

C=1

C=1이면 이전의 Latch가 비활성화 되고 직전의 D입력값이 된다.

다음의 Latch(Slave Latch)는 활성화 되어 이전의 Latch(Master Latch)의 출력값을 받아 전달한다.

결론적으로, D flip-flop은 c(clock)이 0에서 1로 바뀌는 순간 D가 Q에 반영이 된다.

- Clock이 0에서 1로 올라갈 때 Positive edge(rising edge)라 한다.

그래서 D flip-flop은 positive edge-triggered flip-flop이라 말하기도 함

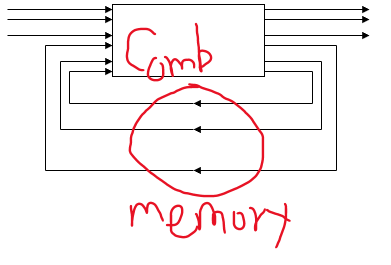

Asynchronous sequential logic

- Asynchronous sequential logic은 control이 1인구간에 state가 change된다(Latch 사용)

Synchronous sequential logic

- Synchronous sequential logic은 clock이 rising edge일때 state가 change(flip flop사용)

대부분의 Sequential Logic은 Synchronous sequential logic을 사용한다.

,

결국 flip flop은 현재의 D값이 다음의 Q값에 반영된다.

Reference 상명대학교 정진우교수님 강의자료

.jpg)