순차 논리(Sequential logic)

출력이 입력에 의해서만 결정되지 않고 기존에 들어왔던 입력들의 영향 또한 받는 논리 회로를 말한다. 조합 논리와 순차 논리의 가장 큰 차이점은 조합 논리는 현재 입력만을 통해 출력을 결정하지만 순차 논리는 그렇지 않다는 점이다.

따라서 순차 논리는 몇몇 종류의 컴퓨터 메모리나 기억 요소, 유한 상태 기계 등을 만드는 데 사용된다.(위키백과)

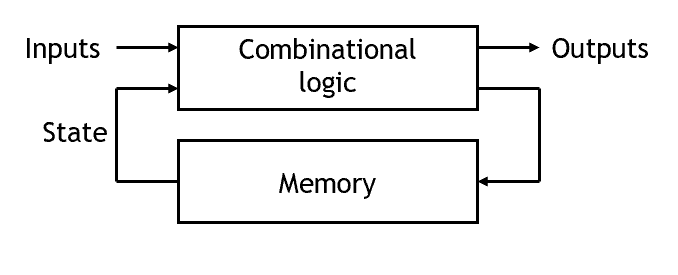

Sequential logic은 같은 input이라도 memory의 State에 따라 다른 Outputs을 만들어 낸다.

Memory

메모리는 최소 3가지 속성이 있어야한다.

1.값을 담을 수 있어야하고(to hold)

2.값을 읽어올수 있어야하고(to read)

3.값을 바꿀 수 있어야한다.(set, reset)

Latch

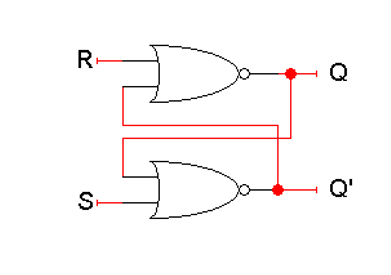

SR Latch

SR Latch 는 sequential logic을 구현할 수 있는 가장 단순한 소자이다.

여기서 Q와 Q'는 서로 complement하다.

1) SR = 00

Q=1이면 Q' = 0이고 Q = 0이면 Q'=1이되어 현재의 값을 유지할 수 있다.(hold)

2) SR = 10

S가 1이므로 Q' = 0이고 따라서 Q = 1이 된다. Q를 1로 만들어 주었다.(set)

3) SR = 01

R이 1이므로 Q = 0으로 고정이되고 Q' = 1이 된다 Q를 0으로 (reset)

4) SR = 11

Q와 Q'가 모두 0이 되기 때문에 Q와 Q'가 complemet하지 않다. 사용X

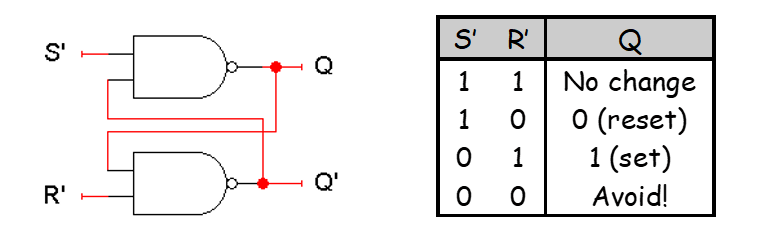

S와 R을 invert해서 NAND gate로 active-low SR Latch 구현 할 수 있다.

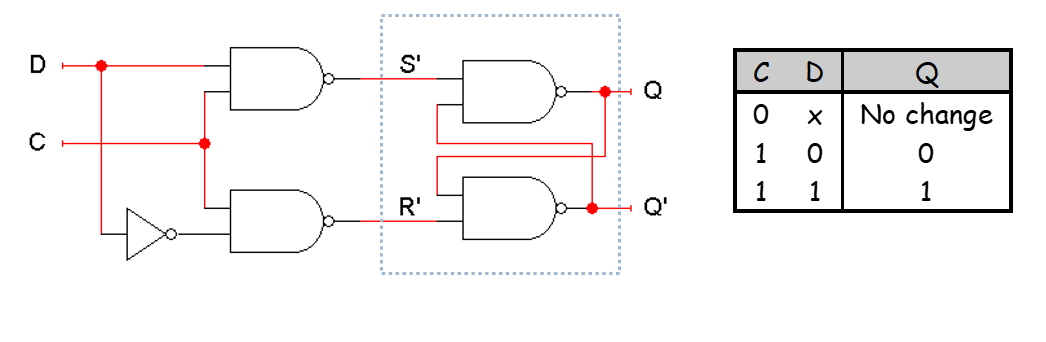

D Latch

SR Latch에서 SR=11일때의 문제를 해결하기 위해 D Latch를 사용한다.

C = 0이면 D Latch는 hold기능을 수행하고 C = 1면 output Q는 D의 값을 따라간다.(set, reset)

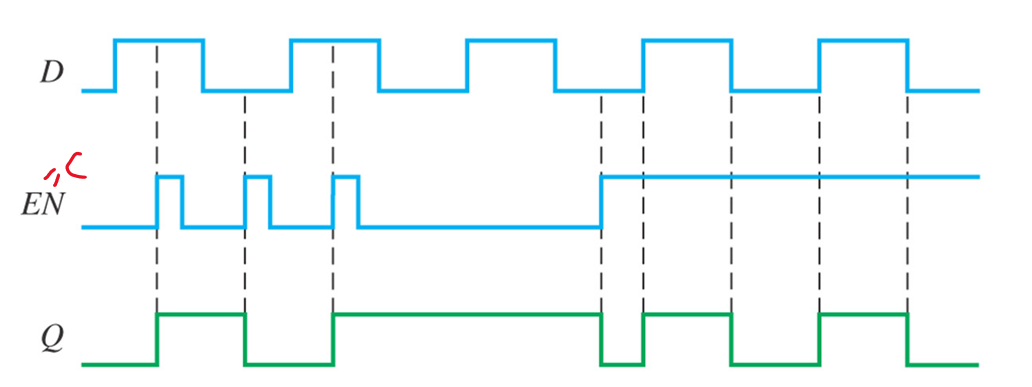

D-latch의 timing diagram

Q는 EN(=C)값이 0이면 hold되고 1이면 D의 값을 따라가는 것을 알 수 있다.

D Latch는 'level-triggered device'라고도 한다. Q는 en(C)의 level(0, 1)에 따라 trigger(반응)해서 D값이 Q에 반영된다.

Reference 상명대학교 정진우 교수님 강의 자료

.jpg)