VHDL(VHSIC Hardware Description Language)

디지털 회로 및 혼합 신호(mixed-signal, 아날로그 신호 포함)를 표현하는 하드웨어 기술 언어이다. FPGA나 집적회로 등의 전자공학 회로를 처리하는 설계 자동화에 사용한다.(위키백과)

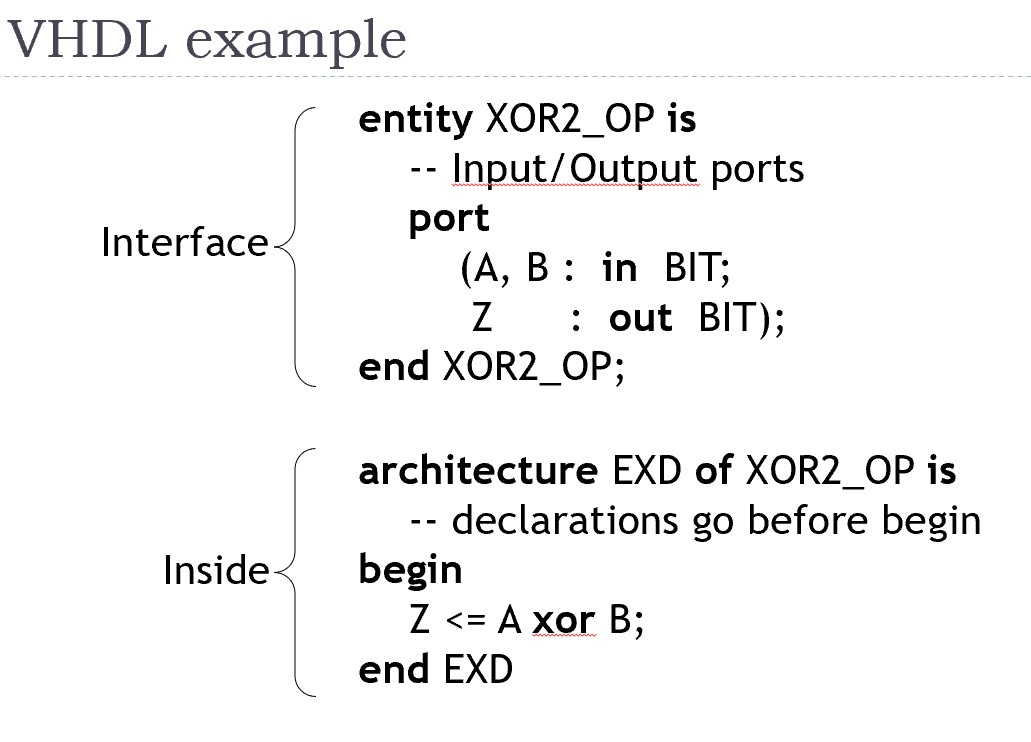

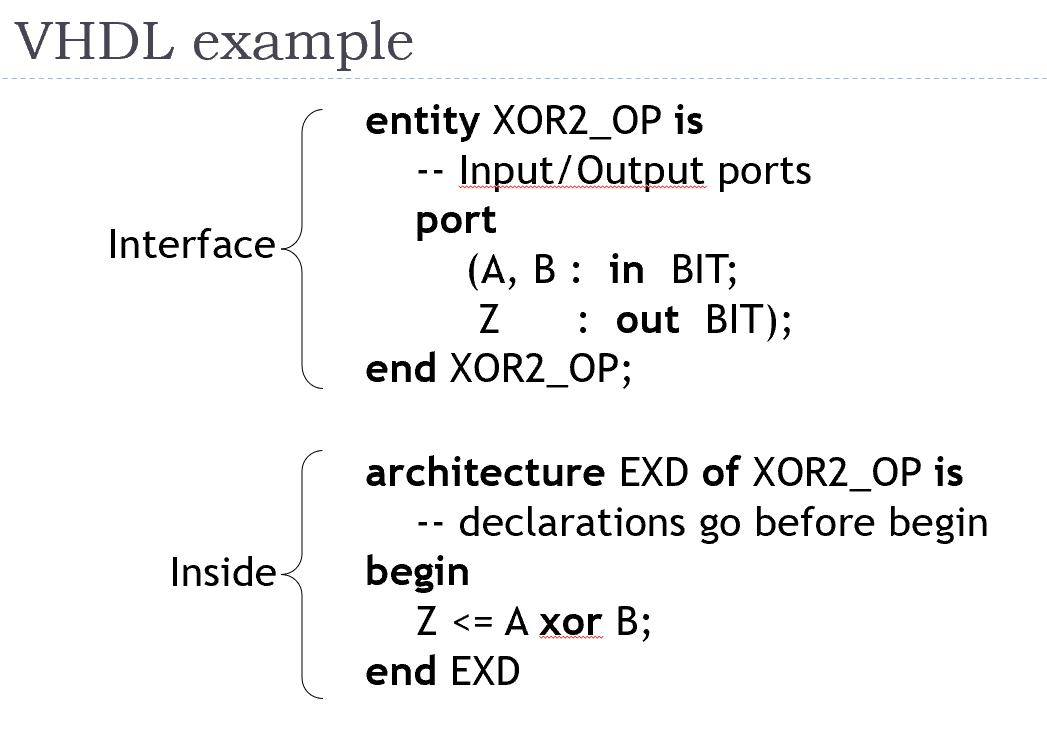

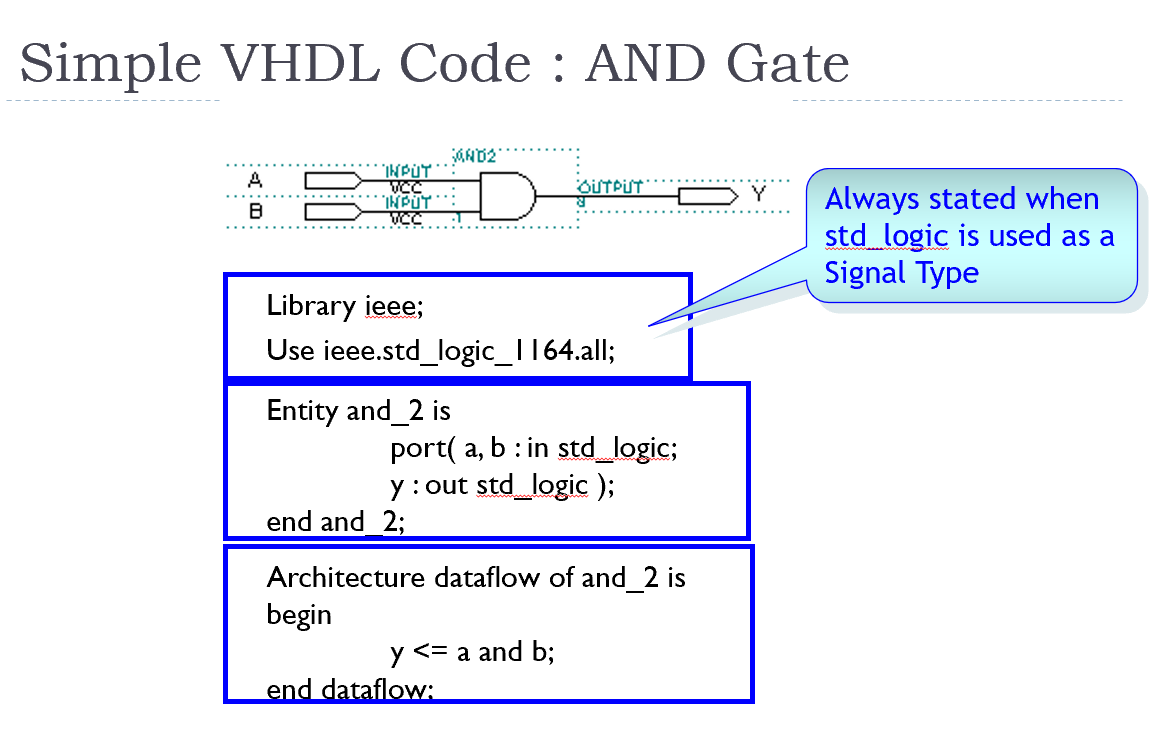

VHDL은 크게 Entity와 Architecture로 구분 할 수 있다.

Entity는 외부 인터페이스를 정의한다. Entity는 껍데기이고 Architecture는 내부동작을 수행한다.

Archtecture는 begin이라는 부분으로 또 나뉜다.

위의 예시에서 entity이름부분(XOR2_OP)에서 VHDL naming rule은 영어, 숫자, 언더바만 쓸 수 있고 이름의 첫 부분은 항상 알파벳이다.

VHDL은 대소문자를 구분하지 않는다.

Entity

PORT

Entity의 port부분에서는 Data_type를 정의해야한다.

Data_type에는 scalar와 vector값이 있다.

Scalar는 single-value값이고 Vector는 그 값들이 모인 Multu-value값이다.

Scalar: bit('0' or '1'), std_logic, integer 타입이 있다.

Vector:bit_vector, std_logic_vector 등이 있다.

std_logic 또는 std_logic_vector 타입을 쓸 땐 아래와 같은 라이브러리를 선언해 주어야 한다.

Library ieee;

Use ieee.std_logic.all;downto 와 to

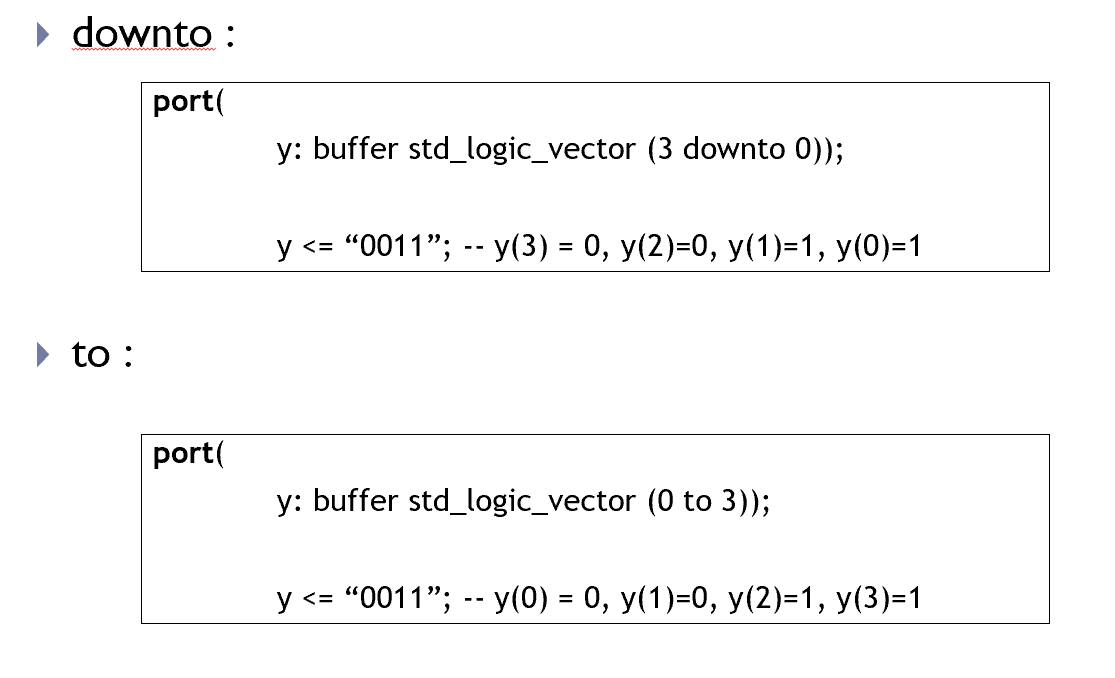

MSB를 명시할 때 downto와 to를 활용하는데 downto는 MSB가 왼쪽, to는 오른쪽

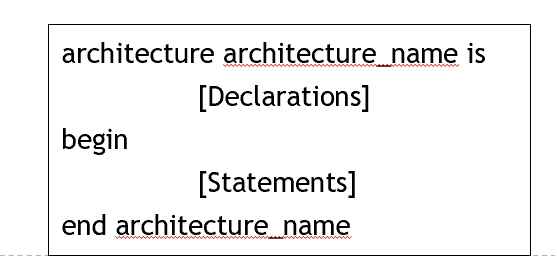

Architecture

Architecture역시 naming은 entity와 같은 룰을 따른다.

Architecture는 크게 Declaration부분과 Statements부분으로 나뉜다.

Declaration부분에서는 사용할 type, signal, componet, subprogram을 선언해준다.

Statements부분에서는 구성 요소의 조직 및/또는 기능적 작동을 설명하는 설명을 포함한다.

VHDL코드로 간단한 AND Gate를 구현한 것

Reference 상명대학교 정진우교수님 강의자료

.jpg)