source

mux.v

`timescale 1 ns / 1 ns

//port

module mux

(

output reg y ,

input wire s ,

input wire i1 ,

input wire i0

);

always @ (s or i1 or i0)

if (s == 1)

y = i1 ;

else

y = i0 ;

endmodule

~

mux_test.v

`resetall

//`include "defines.inc"

`timescale 1 ns / 1 ns

module mux_test;

wire y ;

reg i0 ;

reg i1 ;

reg s ;

//MUX instance([module name] [instance name]

mux mux1(

y,

s,

i1,

i0

);

task display ;

begin

$display

(

"time=%0d" , $time, " ns"

, " s=", s

, " i1=", i1

, " i0=", i0

, " y=", y

);

end

endtask

initial

begin

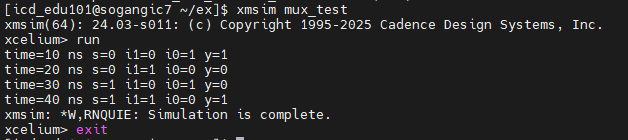

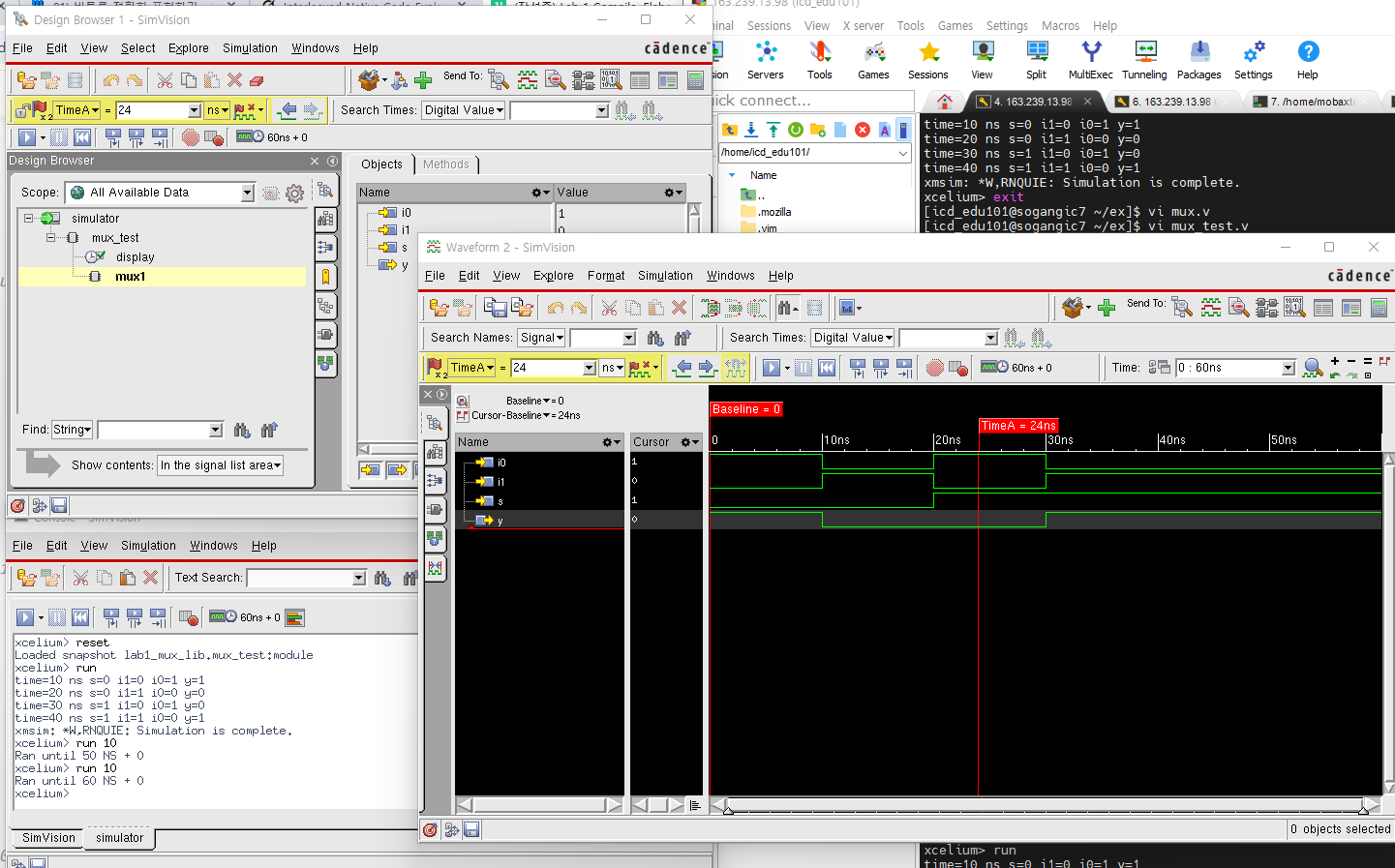

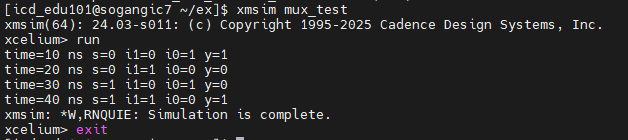

s = 0 ; i1 = 0; i0 = 1 ; #10 ; display;

s = 0 ; i1 = 1; i0 = 0 ; #10 ; display;

s = 1 ; i1 = 0; i0 = 1 ; #10 ; display;

s = 1 ; i1 = 1; i0 = 0 ; #10 ; display;

end

endmodule

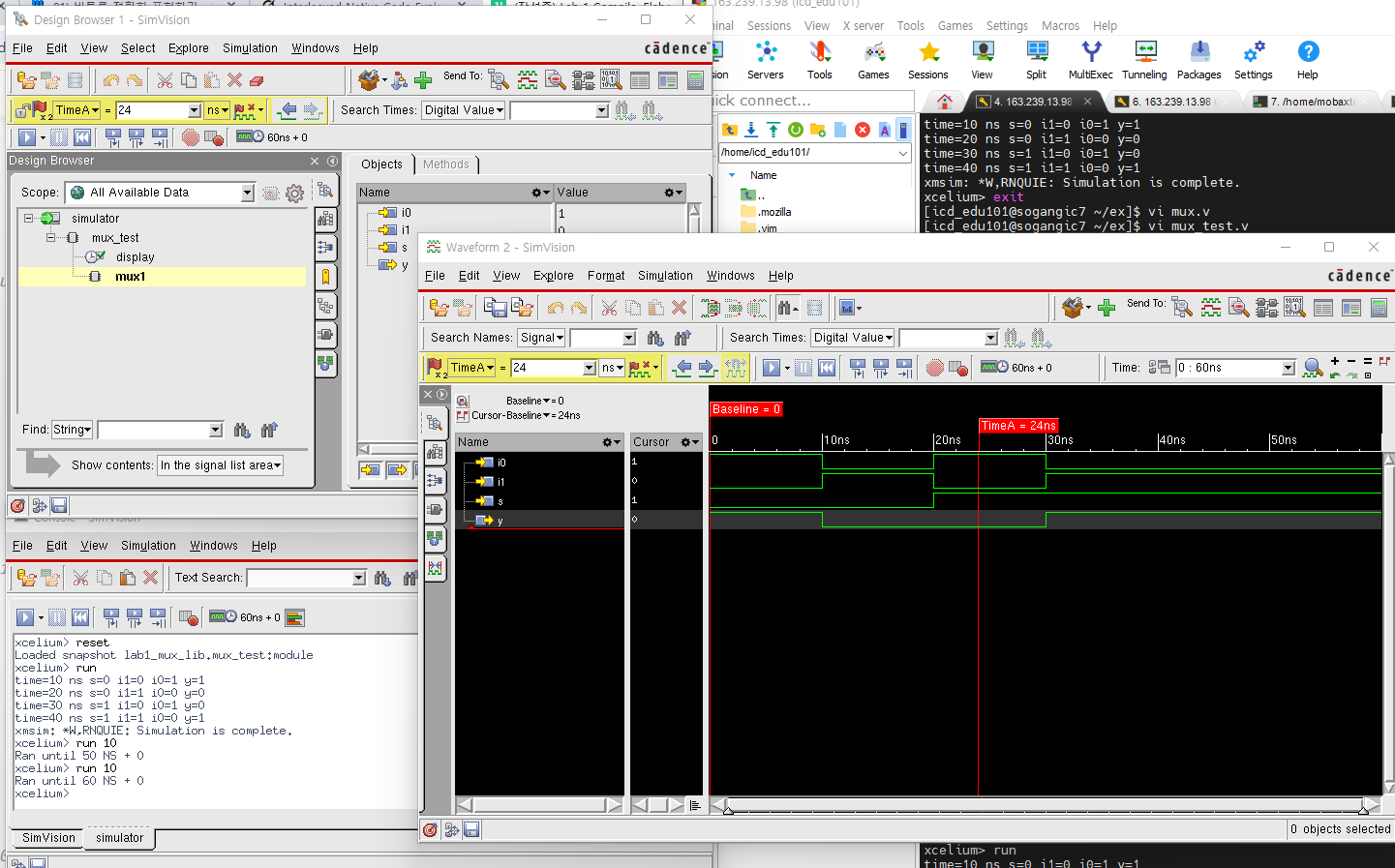

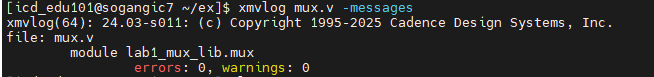

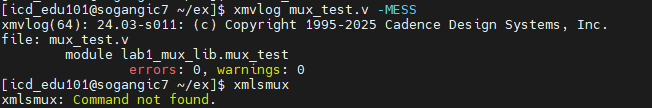

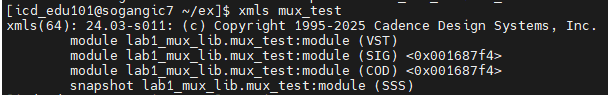

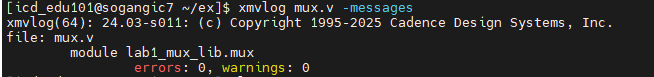

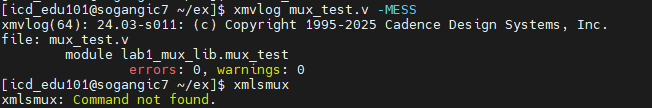

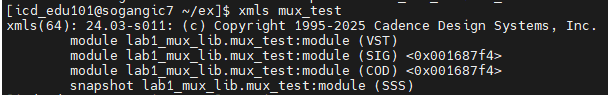

xmvlog

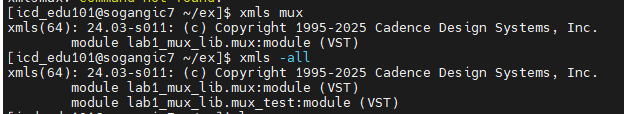

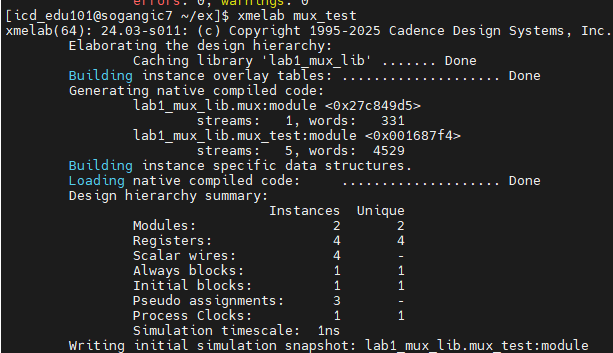

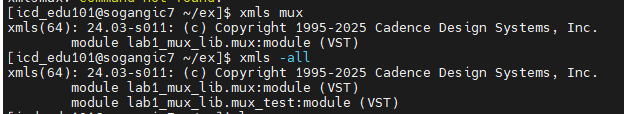

xmelab

xmelab -access RWC top (gui 접근 설정)

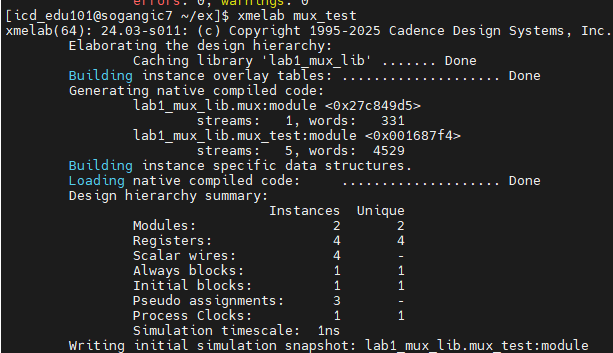

xmsim

xmsim -gui -run mux_test