Memory Component

- 보다 많은 bit를 기억하기 위해 register를 많이 사용하게 됨.

- 어느 register에 저장할 지, 다시 load할 때도 어느 register에서 load할 지를 알아야 함.

- 위와 같은 이유로

address가 도입.address는 memory의 특정 위치를 가르키며 실제 데이터가 memory의 어디에 저장되어 있는지를 나타냄.

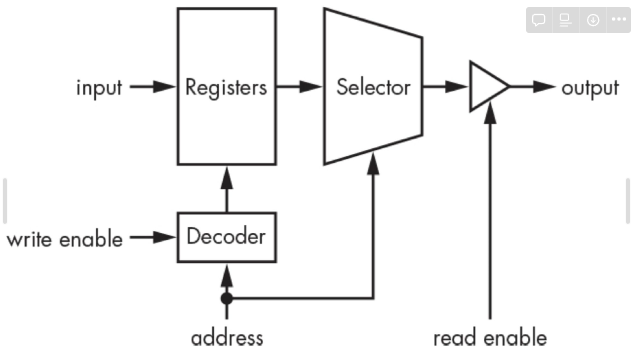

Memory with Address

- 위 그림은 address를 이용한 memory component의 구조

Decoder를 통해 address를 이용하여 실제 저장된 register를 선택.Selector(Mux)를 이용하여 여럿 연결된 register의 출력 중 address에 해당하는 register의 출력을 출력tri-state output을 선택하여 여러 memory component들을 묶음.

cf) 여러 output들을 하나의 핀으로 묶을 경우 open-drain or tri-state가 쓰임.

GPIO and BUS

- General Purpose I/O는 chip에서 제공하는 핀의 수가 한정되어 있기에 특정 핀들을 입력과 출력으로 같이 쓰는 경우를 말함. tri-state output으로 구현됨.

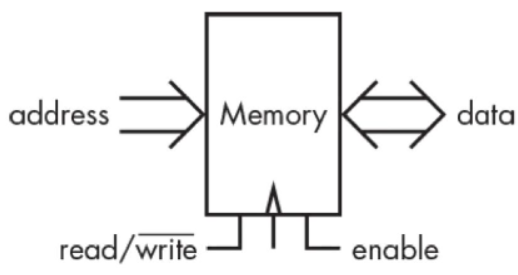

- memory의 경우 read와 write가 동시에 이루어지는 경우가 거의 없기 때문에 GPIO를 이용하여 핀의 수를 줄임.

BUS는 1bit의 개별 signal 대신 연관된 signal들을 묶은 것.- Memory의 경우 address signal들을 묶은 Address bus, data signal들을 묶은 Data bus를 가짐.

- 위의 그림은 이전의 Memory component에 tri-state를 적용하여 입출력 단자를 공유하고, Bus를 도입한 Schematic diagram.

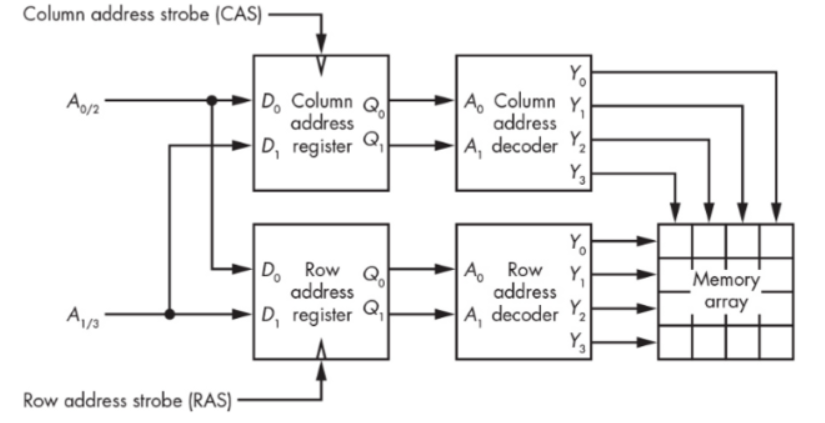

Address Register(Row and Column)

- Memory의 용량이 커질수록 address의 길이가 길어지기 때문에 address를 상위, 하위로 나누고 address register들(column address register, row address register)과 address strobe들 (CAS, RAS)를 도입하여 address bus의 폭을 절반으로 줄여서 사용.

- 상위, 하위로 나누는 것을 matrix의 row와 column으로 생각할 수 있음.

- 특히 상위 address(row address)는

Page라고 불림. - 일반적으로 같이 많이 쓰는 데이터는 한

Page내에 같이 저장되어 row는 고정하고 column만 변화시켜 처리하는 방식으로 동작하여 입출력 성능 향상 - Strobe는 parallel connection에서 신호를 구분하기 위해 사용하는 신호로 memory에서는 Column address strobe(CAS), Row address strobe(RAS)가 있음.

- 위의 그림에서 row와 column register에 parallel하게 과 이 연결되어 있는데 CAS, RAS를 통해 과 이 row에 대한 주소 , 로 쓰이는지 아니면 column에 대한 주소 , 로 쓰이는지가 구분됨.

- strobe에 의해 memory의 속도(latency)가 결정됨. 일반적으로 Column Access Strobe(CAS)가 memory latency를 결정

References:

1) https://dsaint31.me/mkdocs_site/CE