Gates

Combinational Logic Circuit의 Boolean function들을 구현한 H/W- 보통 IC chip으로 제공되지만, transistor로도 구현 가능하며 FPGA에서는 HDL을 통해 programming 형태로 이용할 수 있도록 제공하기도 함.

Combinational logic

- Boolean algebra의 logic function을 구현한 것이

combinatorial circuit. combinational logic circuitorcombinational logic이라고 불림.- Digital system의 instaneous system.

Instaneous system

- logic function의 출력은 해당 출력 시점에서의 입력들의 combination에 의해 결정됨.

- Boolean function을 구현하고 있는 combinational logic circuit은 결국 instaneous system으로 내부 상태를 저장하는 memory가 없음을 의미.

- 이와는 반대로 memory가 있어서 이전의 상태를 기억하고 이를 반영하여 출력이 결정되는 system을 dynamic system이라고 함.

(Logic) Gates

- Combinational logic에서 사용되는 Boolean function들을 구현하고 있는 chip(or circuit)을 의미

NAND와NOR이 가장 기본적인 gate로 사용.AND,OR,NOT을 조합하여 모든 boolean expression이 가능하지만 실제로는NAND,NOR로 구성되는 경우가 대부분이며 그중에서도NAND가 주로 사용됨.- symbol, truth table, De Morgan's Law 등에 관한 내용은 아래 링크 참조.

Bits and Boolean-Algebra

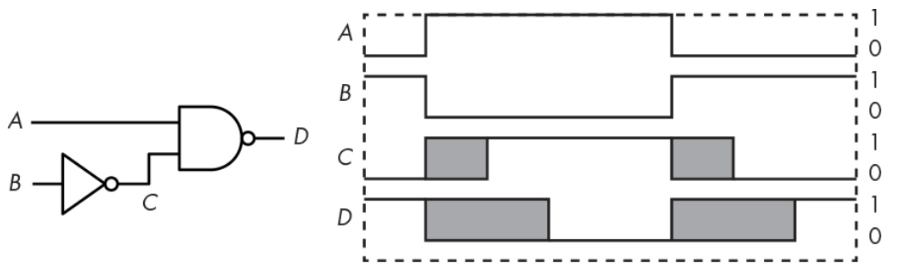

Noise Glitch

- Digital system에서의 Glitch는 아주 짧은 시간 동안 원래 의도한 값이 아닌 error value들로 출력 신호들이 나오는 현상

- 이러한 noise glitch의 경우 Schmitt trigger 등을 사용하여 해결함.

Schmitt trigger

- Hysteresis(이력현상)을 이용한 logic gate.

- Hysteresis를 이용하거나 Differential signaling을 통해 noise를 줄일 수 있음.

- Noise immunity가 필요한 경우 사용되는 소자로 noise가 심한 경우에도 output에서의 glitch가 적어짐.

- Feedback이 필요함.

hysteresis

- 물질이 거쳐 온 과거가 현재 상태에 영향을 주는 현상

- 현재의 어떤 물리량이 현재의 물리조건(input)만으로 결정되지 않고 이전에 그 물질이 경과해 온 과정에 의존하는 특성

- 위 그림은 Transfer function of a Schmitt trigger를 보여줌.

- 위 그림은

U와 같은 입력에 대해서A는 고정된 threshold를 사용한 경우이고,B는 schmitt trigger를 사용한 경우.

- 위의 그림들은 차례대로 schmitt trigger의 symbol과 inverted schimitt trigger symbol을 나타낸 것임.

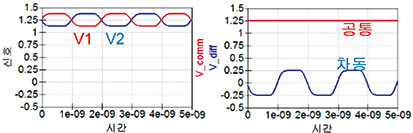

Differential signaling

- signal을 전송할 때, Driver를 통해 원래 신호와 해당 신호의 complementary(반전된 신호)를 만들고 이들 각각을 2개의 전송선으로 전송한 후 receiver에서 이들의 차이를 계산하여 다시 하나의 신호로 만드는 방식

- 일반적으로 differential pair에서는 2개의 정보가 전송됨.

differential signal: Driver에서 나온 신호()와 complementary()의 차이common signal: 원래 신호와 complementary의 공통성분으로 noise 등이 포함되어 있음.

Common Mode Rejection Ratio(CMRR)

- Differential signaling에서 처리가 가능한 noise의 한계를 나타내는 specification.

- Ideal한 differential signaling의 경우, receiver로 들어온 원래 신호와 complementary 간의 전압 차이가 아무리 적어도 정확히 차이를 구할 수 있음.

- 하지만, 실제는 매우 작은 차이의 전압은 구분하지 못할 수 있으며 이 경우 제대로된 출력이 불가능함. 이 때 차이 전압을 구분해 내는 능력을 척도로 나타낸 것이 Common Mode Rejection Ratio.

- CMRR은 Common mode를 제거 또는 거부하는 정도를 나타내며 성능을 결정짓는 매우 중요한 요소임.

Prepagation Delay

- Logic gate등의 device들로 구성된 system or system을 구성하는 단일 device 등에서 input의 변화가 output의 변화로 나타나는데 걸리는 시간

- 구성 부품 수나 온도와 같은 외부 환경 및 제조 과정에서의 편차 등이 반영되기 때문에 하나의 상수로 표현되기보다는 통계적인 특정치로 표시됨.

- 일반적으로 logic gate에서 minimum과 maximum을 같이 기재하며, 발생되는 propagation delay는 이 범위 내에 존재함.

- ripple-carry adder를 사용하지 않고 carry look-ahead adder가 사용되는 이유가 바로 prepagation delay 때문.

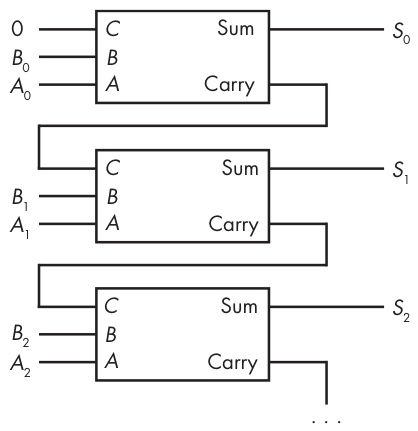

Ripple-carry adder and Carry look-ahead adder

Ripple-carry adder는 carry가 아래쪽 bit부터 바로 위쪽 bit로 물결이 퍼져나가는 것처럼 전달됨.- 비트를 하나 처리할 때마다 gate 2개에 해당하는 출력 시간 지연이 발생하게 됨. 32bit, 64bit adder를 만드는 경우 이 delay가 더 커짐.

Carry look-ahead adder을 사용하면 각 자리에서 자리올림에 대한 연산을 수행하고 본 함수부에서 수학적인 분석을 통해 기존 자리의 연산을 기다리지 않고 단번에 계산을 이끌어내는 방식으로 propagation delay를 제거할 수 있음.

Example

- 위의 그림에서 gray area에서는 해당 signal 값의 보장이 어려움.

- ideal device의 경우 즉시 변하겠지만, propagation delay가 gray area를 만들어냄.

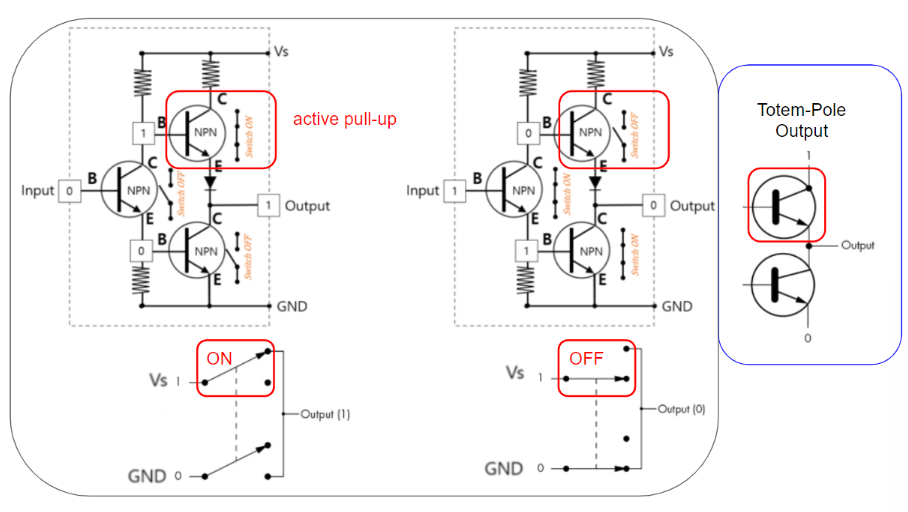

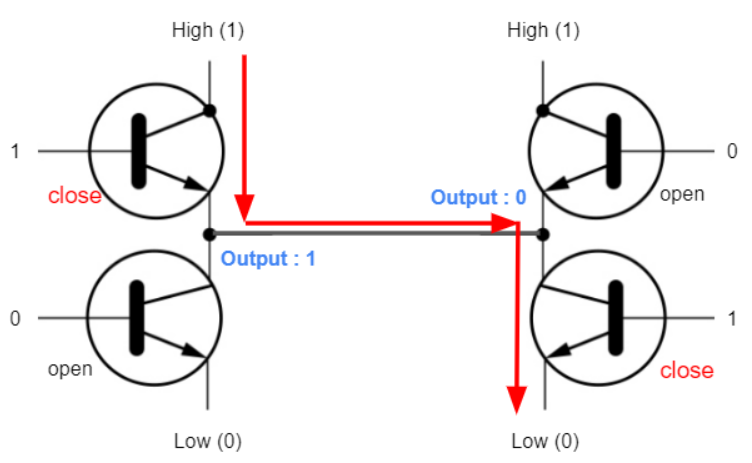

Gates Output: Totem-Pole Output

- NPN BJT가 연결되어 totem처럼 보인다 하여 totem-pole이라 불림.

- input이

0이 들어갈때, Totem-pole의 상단에는1이, 하단에는0이 들어가며 이로 인해 output이 1이 나옴. - 위의 반대의 경우 output이

0이 나옴. - 상단의 NPN BJT는 일종의 active pull-up으로서 출력을 high voltage와 연결하는 역할

- 0인 출력과 1인 출력을 같이 연결할 경우 음극과 양극을 서로 같이 연결하는 것과 같은 일이 벌어져 부품이 타는 현상이 발생. 따라서 상하의 NPN BJT의 base에서 들어가는 input은 항상 달라야 함.

- 아래 설명할 open-collector(FET의 경우 open-drain)의 경우와 달리 totem-pole output을 위와 같이 서로 연결하여 한쪽이 1로 다른 쪽은 0인 경우 short가 일어나 출력단에 연결된 BJT가 망가지게 됨.

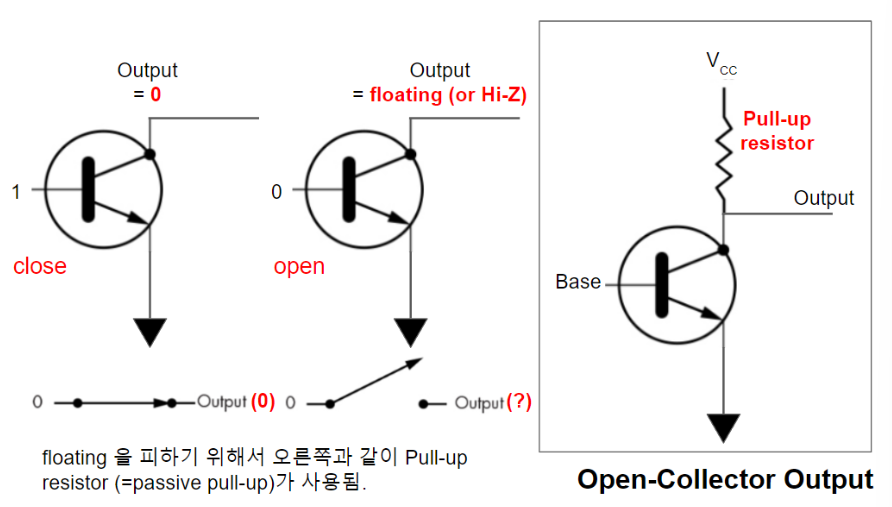

Gates Output: Open-Collector Output

- Totem-pole output과 달리 Open-collector(or open-drain) output은 여러 개를 같이 연결할 수 있다는 장점 보유.

- 또한 Totem-pole output보다 높은 current 처리 가능.

- Open-collector output에서는 신호가 1일때 확실하게 0을 출력.

- 신호가 0인 경우 output을 명확하게 알 수 없음.

- 위의 그림 왼쪽에서 보이는 것처럼 도체가 공중에 떠있는

floating(Hi-Z) 상태에서는 voltage를 정의할 수 없음. - 그래서 위의 그림 오른쪽에서 보이는 것처럼

pull-up resistor를 연결하여 base가 0일 때 collector의 output이 floating이 아니라 1로 되도록 collector를 high voltage()에 연결해줌. - base에 0이 가해지면 transistor는 끊긴 상태로 저항이 무한대가 되어 전압 대부분이 transistor에 걸리기 때문에 output은 1이 출력됨.

- base가 1인 경우 output은 gnd와 연결되어 0이 출력됨.

- Open-collector output의 단점으로는 Totem-pole output보다 속도가 느리고 pull-up resistor로 인해 0을 출력할 때 전력을 소비하게 됨.

- 낮은 pull-up resistor일수록 높은 current가 흐르기 때문에 전력 소모가 커지게 됨.

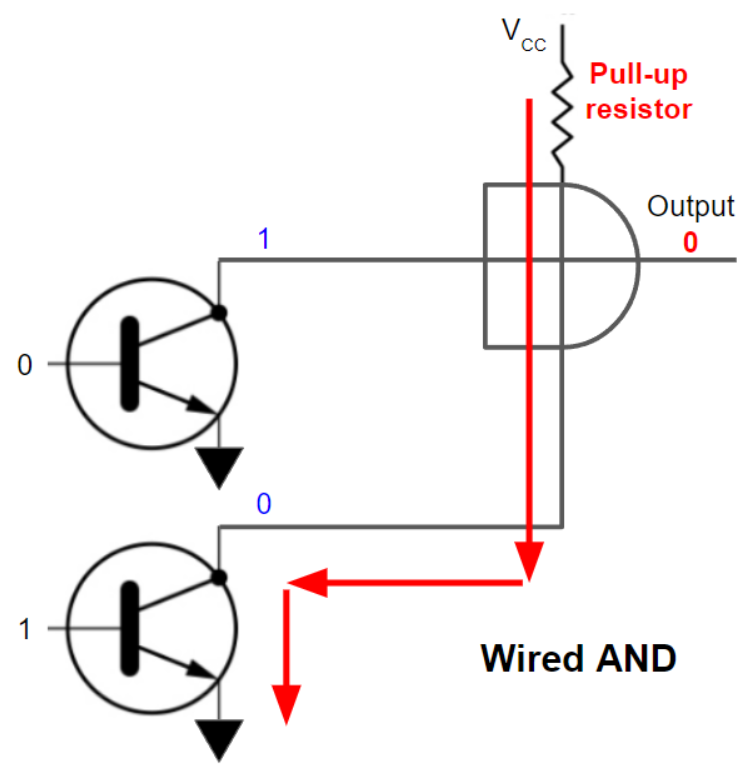

Wired-AND

- Open-collector output을 여러개 연결할 경우 일종의

ANDgate를 묶은 출력으로 볼 수 있음. - 위 그림에서 왼쪽의 Open-collector output 중 하나라도 0인 경우에 해당 transistor는 close되어 와 ground간의 circuit이 생성되고 output은 0이 출력됨.

- 연결된 Open-collector output 모두가 1인 경우에만 이들이 연결된 output에서 1이 출력됨.

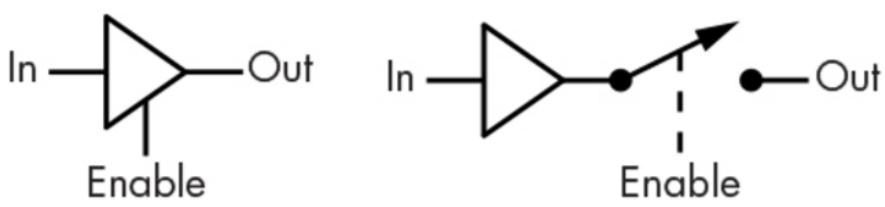

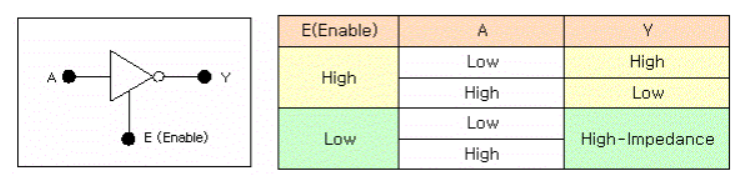

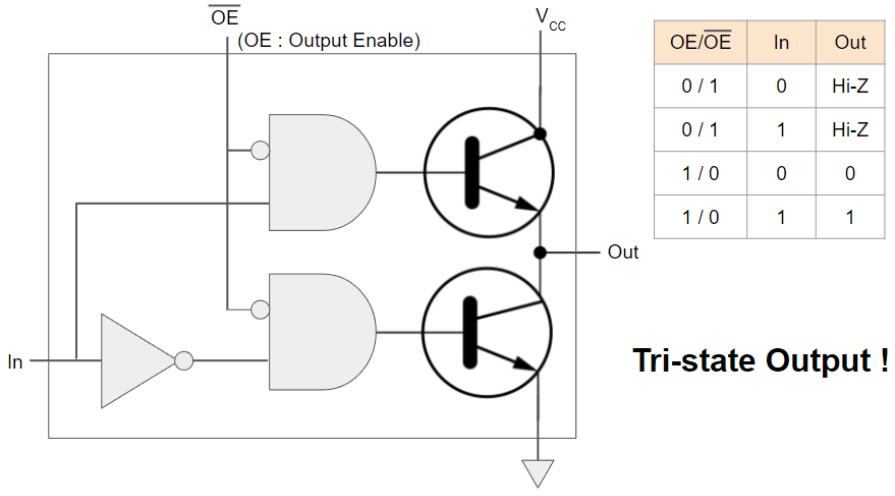

Gates Output : Tri-state Output

- 일반적으로 digital circuit은

0or1의 2개의 상태를 가지고 있지만 Tri-state는 High-Impedance 상태를 추가적으로 가지고 있음. Enable입력을 추가해서, 해당 output을 사용하려면Enable(orOE(Output Enable))에 activate 신호가 주어지면 output이 input과 연결된다고 생각하면 됨.

Enable이 low인 경우가offorhi-Z라고 부름- 로

Enable을 표기하기도 함.

- 위 그림의 Tri-state output에선 위아래의 transistor들의 base에 동시에 1이 들어가지 못하게 설계됨. 만약 1이 동시에 들어가면 meltdown 현상 발생

- Tri-state output은

Enable을 도입하면서 open-collector output처럼 여러 개가 연결될 수 있음. 단, 연결된 여러 output들 중 사용할 output에만Enable을 activation시키고, 나머지는 deactivation시켜야 함.

References:

1) https://dsaint31.me/mkdocs_site/CE

2) https://en.wikipedia.org/wiki/Schmitt_trigger

3) https://www.seminet.co.kr/channel_micro.html?menu=content_sub&com_no=800&category=article&no=4201

4) Jonathan E., The Secret Life of Programs, p.62

5) https://en.wikipedia.org/wiki/Carry-lookahead_adder

6) https://ansan-survivor.tistory.com/1214