Time and Memory(1)

- Sequential logic의 경우 과거의 출력값에도 영향을 받기 때문에 memory device가 필요함.

- 현재 input 이외의 과거 상태 및 현재 상태 값들을 고려하여 출력이 결정되기 때문에 time을 나타내는 device 필요.

Oscillator

- 일정시간에 맞춰 반복되는 주기적인 펄스를 발생시켜 computer등에서 time 정보를 제공하는 역할

- CPU 등에서 동작 clock 등이 해당 device가 어떤 빠르기로 동작하는지를 나타내며, 이와같은 동작 clock을 제공하는 것이 oscillator

- 주로 piezoelectric effect를 이용하는 crystal로 만들어짐. crystal에 전기를 가하는 경우, 일정 시간 이후 crystal이 다시 전기를 만들어내는데 이 때 시간 간격이 매우 정확함.

- 위와 같은 원리를 이용하여 clock signal을 발생시키는 oscillator가 만들어짐.

Clock

- computer나 circuit의 동작 pace.

- 보통 [Hz]로 표현하며 초당 몇번의 pulse signal이 반복되는지로 빠르기를 나타냄.

- computer나 circuit을 구성하고 있는 여러 device들은 propagation delay 등의 특성이 다르기 때문에 clock에 맞춰서 정상적인 동작이 이루어지도록 동기화되는 경우가 대부분.(비동기 방식이 없지는 않지만, 제어가 매우 어려움)

- 일반적으로 device들의 시간과 관련된 특성들은 variation이 다양하기 때문에 통계적인 측정치로 표시되며 일정 range에서 정상동작이 보장되는 특징을 가짐.

Latch

- Gate를 조합하여 1bit의 정보를 기억하는 역할을 하는 회로

- 1bit의 정보를 기억하는

flip-flop과의 대표적인 차이점은 clock signal에 대해 high(or low) level에서 기억이 이루어지는지, rising(or falling) edge에서 기억이 이루어지는지에 있음. latch는 주로 high level에서 기억이 이루어지며,flip-flop의 경우 주로 rising edge에서 기억이 이루어지는 version이 많이 사용됨.

OR Latch

- feedback연결과

ORgate를 이용하여 1bit의 정보를 기억한다는 점에서 가장 간단한 latch - 기억만 가능할 뿐 다시 reset이 불가능함.

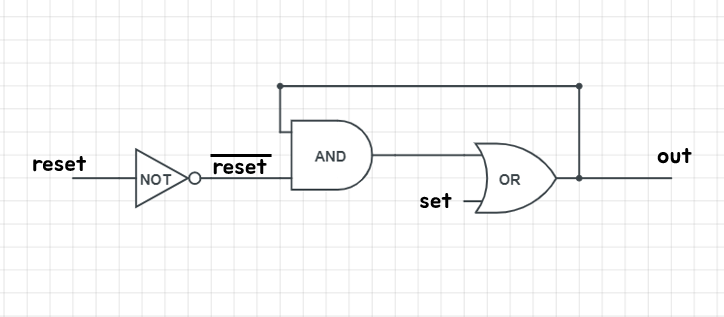

AND-OR Latch

ORlatch의 feedback connection을OR에 직접 연결하지 않고OR앞에 연결된AND에 연결하고 동시에 해당AND에 을 입력시켜 reset 기능을 추가한 latch.ORlatch에서 reset이 되지 않는다는 단점을 보완한 것으로 정보의 기억 및 기억된 정보의 출력, 기억될 정보의 수정이 가능한 가장 간단한 memory.- 대칭구조(symmetric structure)가 아니기 때문에 propagation delay에 취약함.

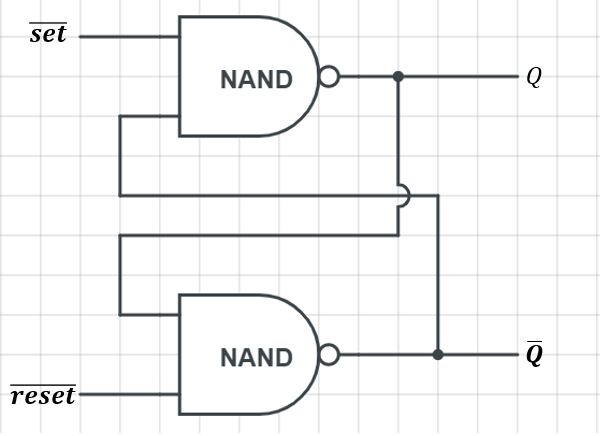

S-R Latch

| 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 1 | |

| 1 | 1 | |||

| 0 | 0 | 1 | 1 | not intended for use |

AND-ORlatch와 같은 역할이지만NAND,NOR로 구현하여 symmetric structure를 가지도록 구현됨.- 흔히 latch라고 하면

S-R latch를 가르킴. - 과 이 동시에 activation 되는 경우 사용하지 않음.(not intended for use)

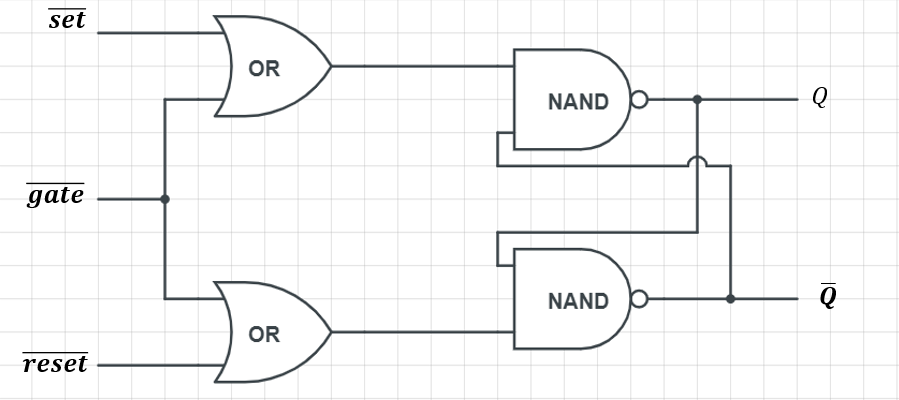

Gated S-R Latch

- clock signal을 입력받아서 특정 시점의 정보를 기억하도록

S-R latch를 확장한 것. - 개념적인

S-R latch가 아닌 실제 회로 등에서 얘기하는 latch는 Gated S-R Latch를 가르키는 경우가 많음. - S-R latch의 과 의 입력단 각각의 앞에

OR을 붙이고 각OR에서 과 의 입력을 받고, 동시에 각OR은 clock이 입력될 동안 입력을 받는 구조. - 위 구조에서 과 은 동시에 1이 될 수 없기에 하나의 신호로 받아 하나는 이를 그대로 입력하고 다른 쪽은 inverter를 거쳐 입력하는 구조로 만드는 것이 나음.

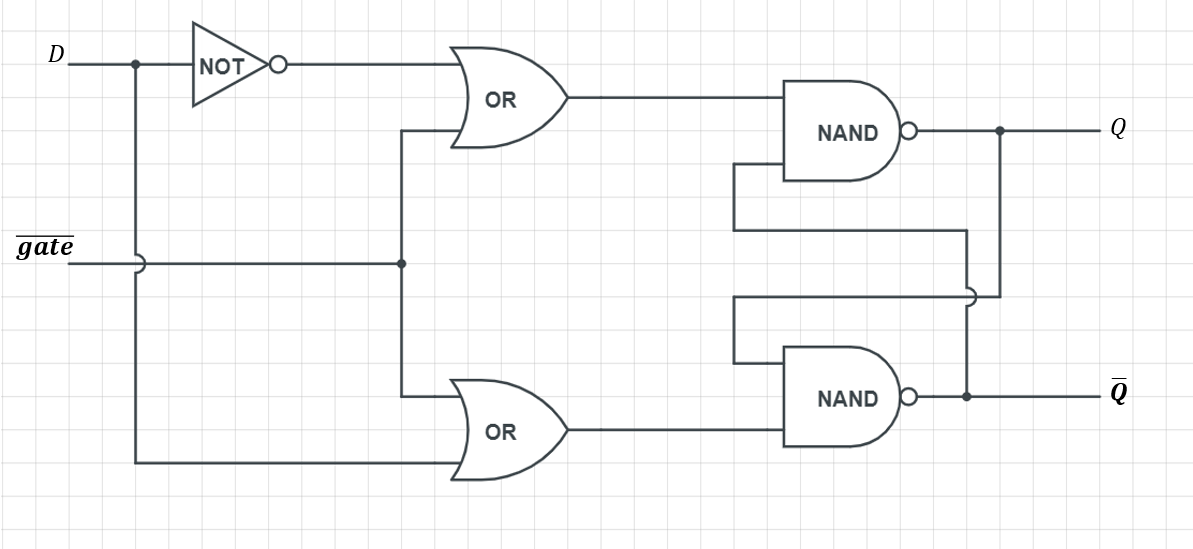

Gate-D Latch

- 위에서 설명한 것을 구현한 것이 D latch.

- 입력을 D라고 하면 이 latch는 해당 D의 1bit 정보를 에 따라 지정된 시간만큼 기억하는 memory로 동작하게 됨.

- 가 low인 경우(=0)에 D의 signal이 그대로 출력 Q에 전달.

따라서 가 low인 경우에는 D의 상태가 변한다면 해당 변화가 그대로 출력 Q로 전달됨.

References:

1) https://www.nutsvolts.com/magazine/article/may2015_HamWorkbench

2) https://soojong.tistory.com/entry/%EC%9E%91%EC%84%B1%EC%A4%91%EC%88%9C%EC%B0%A8%ED%9A%8C%EB%A1%9C-%EB%9E%98%EC%B9%98