Flip-Flops

- 특정 시점의 1bit의 정보를 기억하는 memory device

Latch는 기억이 이뤄지는 시점이 level로 결정되어 해당 level 기간동안 입력이 변경될 수 있음.Flip-Flop은edge(transition between logic level)로 기억이 이뤄지는 시점이 결정됨.edge는 짧은 시간동안 입력을 받아들이기 때문에 해당 시간에 입력이 변경될 확률이 latch에 비해 매우 낮음.- SR Flip-Flop, D Flip-Flop, JK Flip-Flop, T Flip-Flop이 있음.

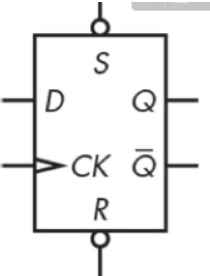

D Flip-Flop

- : input

- : output

- : set, PR(preset), bubble로 인해 active low인

- : reset, CLR(clear), bubble로 인해 active low인

- : Clock Pulse

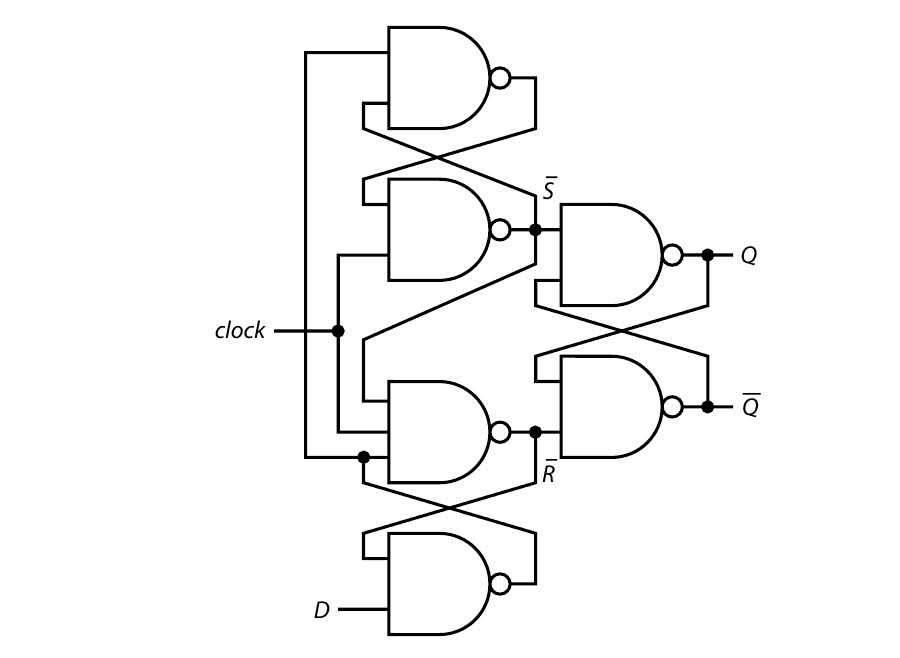

- Gate로 D flip-flop의 구조를 보면 위와 같이 S-R Latch 3개를 이용한 모습임.

Setup and Hold Times

- Flip-Flop처럼 edge에서 입력이 이루어지는 경우, ideal하게 순간의 값이 저장되어야 하지만 현실적으로는 정상적인 입력을 위해 앞뒤로 시간이 필요함.

Setup time: 정상적으로 입력이 이루어지기 위해 입력 signal을 받아들이는 clock edge가 발생하기 전에 input signal이 유지되어야 하는 시간. 으로 표시함.Hold time: 정상적으로 입력이 이루어지기 위해 입력 signal을 받아들이는 clock edge가 발생한 후에 input signal이 유지되어야 하는 시간. 로 표시함.

Counter

- 일정한 순서로 state가 반복하여 변화하는 일종의 Register.

- Oscillator의 clock pulse를 입력받아 Digital System에서 time에 대한 정보를 주는 소자

- Counter의 출력은 Counter의 state가 됨. oscillator의 pulse train의 주기에 정수배한 주기 신호들을 만들어낼 수 있음.

Asynchronous(Ripple) Counter

- Signal이 CK에 들어가면서 signal이 0에서 1로 변할 때마다 count를 세어서 에 출력함.

- Signal은 보통 oscillator로부터 오고, 들은 각각 앞의 입력에 비해 2배 더 긴 주기의 신호를 생성해냄.

- D flip-flop의 부분에 가 연결되어 있기 때문에 1로 올라가고 나서 다시 0으로 떨어지게 되며 이를 CK에 들어오는 signal에 맞춰 반복하게 됨.

- propagation delay에 취약.

Synchronous Counter

- CK를 공유함으로써 모든 flip-flop들이 정확히 같은 시간에 값이 변하게 됨.

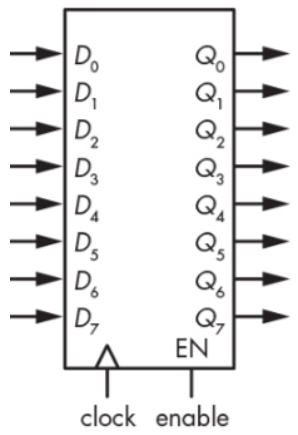

Register

- Flip-Flop 여러 개를 묶어서 여러 bit를 기억하도록 만들어진 device.

- CPU 내부에 위치하며 ALU 등이 직접 접근하여 사용되는 memory.

- 보다 많은 bit를 기억하기 위해서는 각각의 값들이 어느 registor에 저장되는지를 나타내는 address가 필요하며, 이를 위해 decoder와 selector가 연결된 memory device가 등장하게 됨.

clock: rising edge에서 입력 D의 값이 Q에서 출력enable: 해당 입력이 active여야 register가 동작. (여기서는 1이어야 함.)

References:

1) https://bugoverdose.github.io/computer-science/latch-and-flip-flop/

2) https://dsaint31.me/mkdocs_site/CE