1. Paging System

- 프로그램 같은 크기의 블록으로 분할(Pages)

- Page: 프로그램의 분할된 Block

- Page frame: 메모리의 분할 영역

Page와 같은 크기로 분할

- 특징

- 논리적 분할이 아님 (크기에 따른 분할)

- Page 공유(sharing) 및 보호(Protection) 과정이 복잡함

Segmentation 대비

- 간단하고 효율적임

Segmentation 대비

- No external fragmentation (외부 단편화)

- Internal fragmentation (내부 단편화) 발생 가능

- Windows page size: 4KB

1.1 Address Mapping

- Virtual Address: v = (p, d)

- p : Page Number

- d : Displacement(offset) - Address Mapping

- PMT(Page Map Table) 사용 - Address Mapping Mechanism (맵핑 방법)

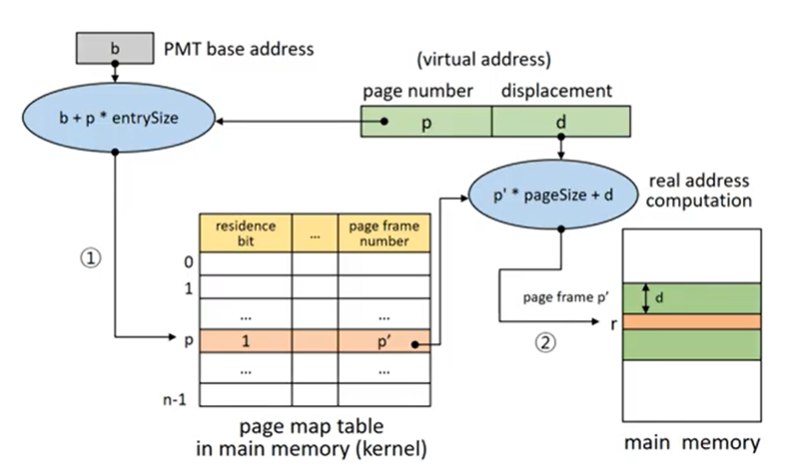

1. Direct Mapping(직접 사상) = block 맵핑과 비슷함

2. Associative Mapping(연관 사상)

- TLB(Translation Look-aside Buffer)

3. Hybrid direct / Associative Mapping

1. Page Map Table (PMT)

- PMT entry size = entry size (한 행의 크기를 entry size)

- Page size = PageSize (프로세스의 page 크기)

2. Direct Mapping

- 해당 프로세스의 PMT가 저장되어 있는 주소 b에 접근

- 해당 PMT에서 Page p에 대한 entry 찾음

- p의 entry위치 = b + p * entrysize- 찾아진 entry의 존재 비트 검사

1). Residence bit = 0인 경우 // Page fault

- Swap device에서 해당 page를 메모리로 적재, PMT를 갱신한 후 3-2 단계 수행

2). Residence bit = 1인 경우, 해당 entry에서 Page frame 번호 p'를 확인- p'와 가상 주소의 변위 d를 사용하여 실제 주소 r 형성

- r = p' * pagesize + d- 실제 주소 r로 주기억장치에 접근

2.1 Direct Mapping Problem

- 메모리 접근 횟수가 2배이다. 이말은 즉, 성능 저하로 이루어진다.

해결방안으로 Associative Mapping(TLB)가 있다 - PMT를 위한 메모리 공간이 필요하다.

해결방안으로 PMT를 위한 전용 기억장치를 사용하는 방안이 있다.

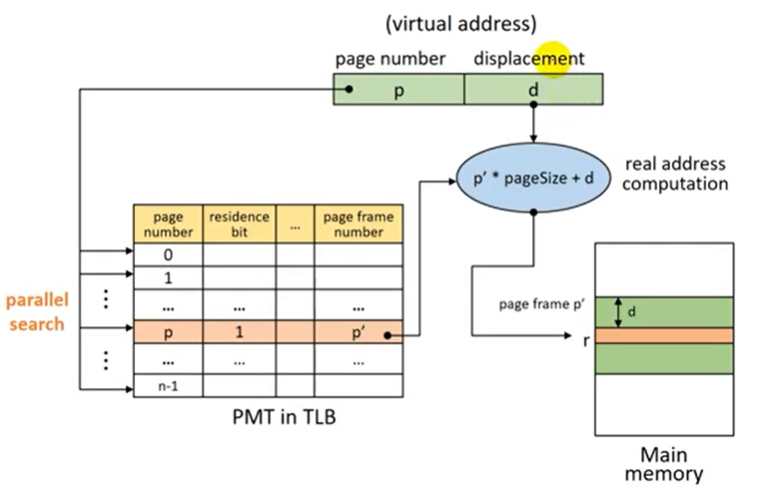

3. Associate Mapping

- Direct Mapping의 메모리 접근 횟수 단점 보완

- TLB(Translation Look-aside Buffer)에 PMT 적재

- PMT를 병렬 탐색

- Low overhead, high speed

- 비싸서 큰 PMT를 다루기가 어려움

3.1 Associate Mapping

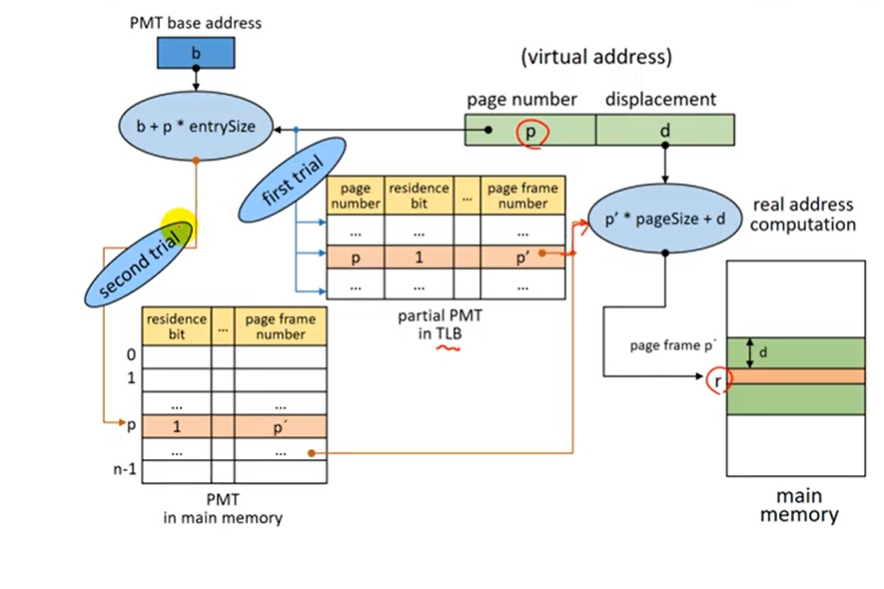

4. Hybrid Direct / Associative Mapping

- Direct Mapping과 Associate Mapping을 혼합하여 사용

- 작은 크기의 TLB 사용

- PMT: 메모리(커널 공간)에 저장

- TLB: PMT중 일부 entry들을 적재

최근에 사용된 page들에 대한 entry 저장

- Locality(지역성) 활용

프로그램의 수행과정에서 한번 접근한 영역을 다시 접근

or 인접 영역을 다시 접근 할 가능성이 높음

4.1 Hybrid Direct / Associative Mapping

>> 프로세스의 PMT가 TLB에 적재되어 있는지 확인

1. TLB에 적재되어 있는 경우

- residence bit를 검사하고, Page frame 번호 확인

2. TLB에 적재되어 있지 않은 경우

- Direct Mapping으로 Page frame 번호 확인

- 해당 PMT entry를 TLB에 적재함

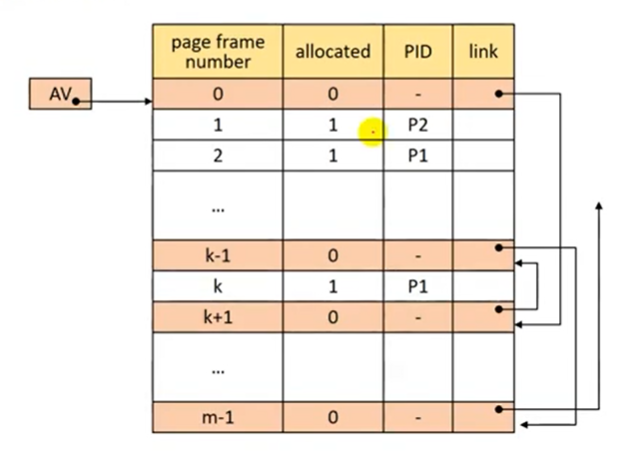

5. Memory Management

- Page와 같은 크기로 미리 분할하여 관리 / 사용

- page frame

- FRM 기법과 유사 - Frame Table

- Page frame당 하나의 entry- 구성

- Allocated / available field

- PID field

- Link field: For free list (다음에 누가 비어져있나 가리켜주는 애)

- AV : Free list header (빈 공간을 찾아주는 포인터)

- 구성

5.1 Page Sharing

- 여러 프로세스가 특정 Page를 공유 가능

Non-continuous allocation

>> 공유 가능 Page

1. Procedure Pages

- Pure code

2. Data Page

- Read-only data

- Read-write data

병행성(concurrency) 제어 기법 관리하에서만 가능

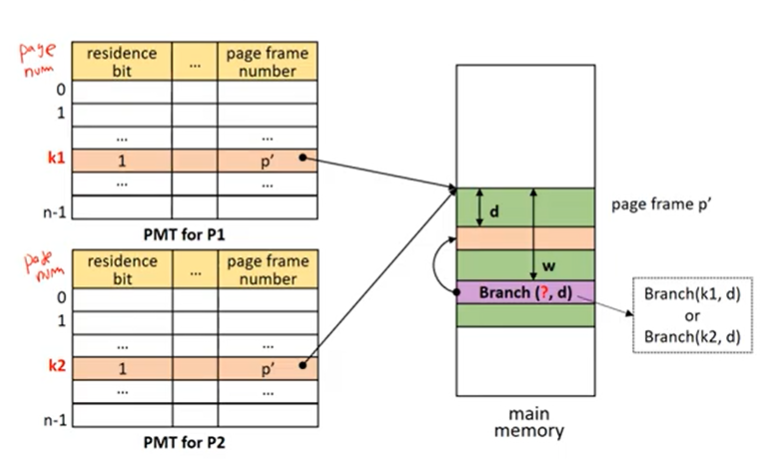

- 아래 사진은 Page를 공유하는 사진입니다. 다만, 다음과 같이 부르는 이름이 다르게 되면 엉뚱한 곳에 도달할 수 있다는 문제점을 가지고 있습니다.

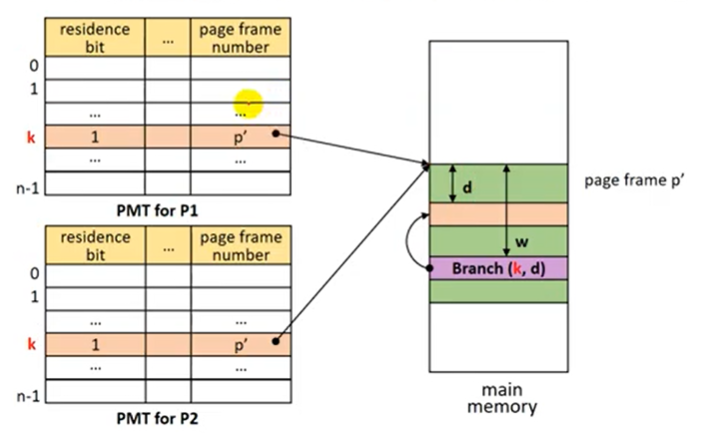

- 위와 같은 문제점을 해결하기 위해, 공유할 Data의 이름을 같게 하는것 입니다. 프로세스들이 shared page에 대한 정보를 PMT의 같은 entry에 저장하도록 합니다.

5.2 Page Protection

- 여러 프로세스가 Page를 공유할 때, Protecton bit 사용

| VRWE | Bits 종류 |

|---|---|

| 1100 | 타당, 비타당(V) 비트: 메인 메모리에 적재 여부 |

| 1110 | 읽기(R) 비트: 읽기 여부 |

| 0000 | 쓰기(W) 비트: 수정 여부 |

| 1111 | 실행(E) 비트: 실행 여부 |

5.3 Paging System Summary

- 프로그램을 고정된 크기의 Block으로 분할(Page)

- 외부 단편화 문제 X

- 메모리 통합 / 압축 불필요

- 프로그램의 논리적 구조 고려하지 않음

Page Sharing이 복잡 - 메모리를 Block Size로 미리 분할(Page frame)

- 필요한 Page만 Page frame에 적재하여 사용

- 메모리의 효율적 활용 - Page Mapping overhead

- 메모리 공간 및 추가적인 메모리 접근 필요

- 전용 H/W 활용으로 해결 가능

하드웨어 비용 증가

지금까지의 내용은 HPC Lab의 강의와 자료를 참조했습니다