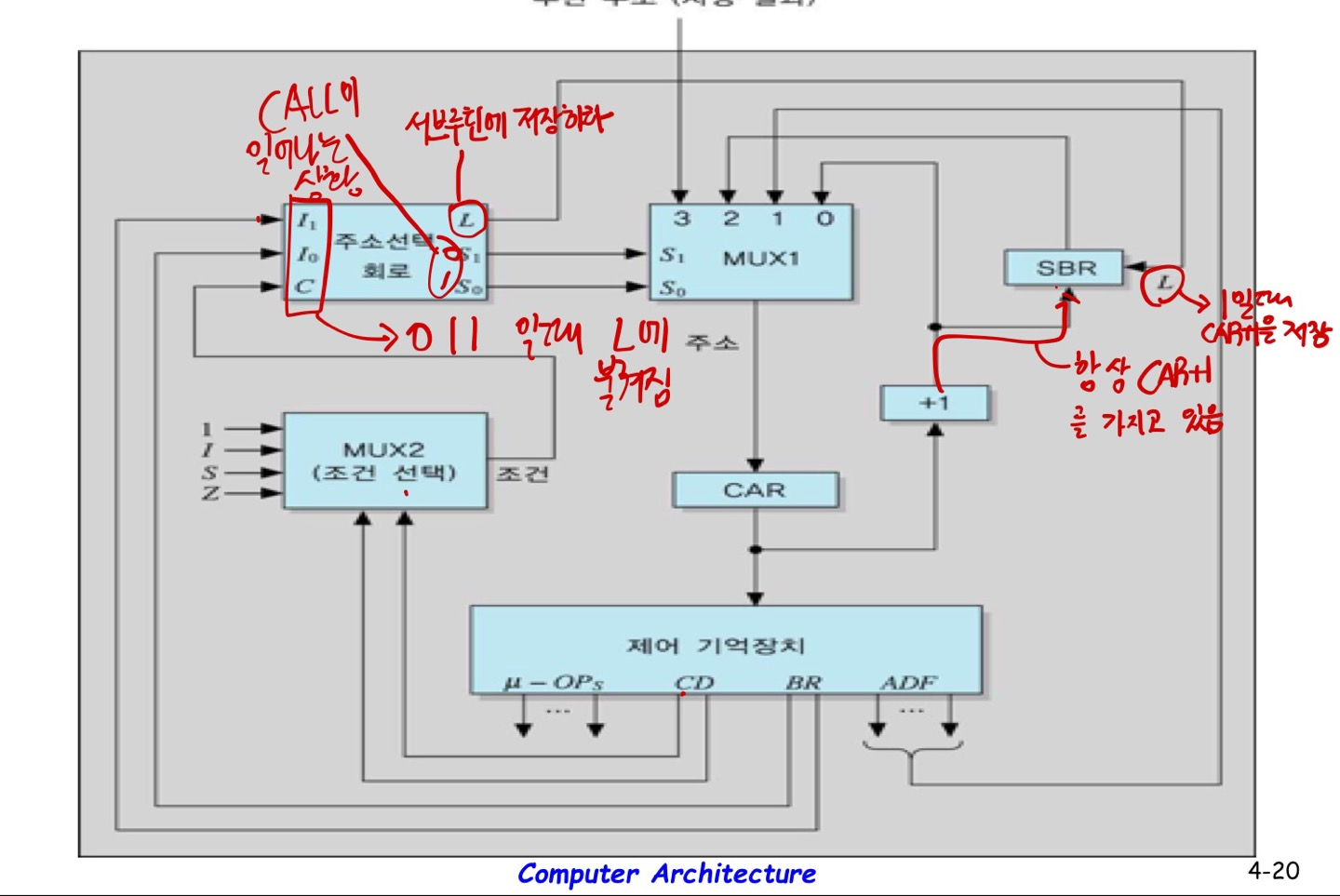

💎 마이크로프로그램의 순서제어

- 순서제어 회로가 포함된 제어 유니트의 구성도

💍 수직적 마이크로프로그래밍

-

Vertical microprogramming

-

마이크로명령어의 연산 필드에 적은 수의 코드화된 비트들을 포함시키고, 해독기를 이용하여 그 비트들을 필욯나 수 만큼의 제어 신호들로 확장하는 방식

-

장점 : 마이크로 명령어의 길이를 최소화 -> 제어 기억장치 용량 감소

-

단점 : 해독 동작에 걸리는 만큼의 지연 시간 발생

💍 수평적 마이크로프로그래밍

-

Horizontal microprogramming

-

연산 필드의 각 비트와 제어 신호를 1:1로 대응시키는 방식

-

필요한 제어 신호 수만큼의 비트들로 이루어진 연산필드 비트들이 마이크로명령어에 포함되어야 함

-

장점 : 하드웨어가 간단하고, 해독에 따른 지연 시간이 없음

-

단점 : 마이크로명령어의 비트 수가 길어지기 때문에 제어 기억장치의 용량이 증가

💎 기억장치

💍 기억장치의 액세스 유형

-

순차적 엑세스 : 저장된 정보를 처음부터 순서대로 액세스 ex) 자기 테이프

-

직접 액세스 : 액세스할 위치 근처로 직접 이동한 다음에, 순차적 검색을 통하여 최종 위치에 도달하는 방식 ex) 디스크, CD-ROM

-

임의 액세스 : 주소에 의해 직접 기억 장소를 찾아 액세스하며, 어떤 기억 장소든 액세스하는 시간이 동일 ex) 반도체 기억장치

-

연관 엑세스 : 저장된 내용의 특정 비트들을 비교하여, 일치하는 내용을 액세스 ex) 연관 기억장치(캐시)

💍 기억장치의 설계 / 전송 단위/ 주소지정 단위

-

기억장치 시스템을 설계하는데 있어서 고려해야 할 주요 특성들

1) 용량

2) 액세스 속도 -

전송 단위 : CPU가 한 번의 기억장치 액세스에 의하여 읽거나 쓸 수 있는 비트 수

- 주기억장치 = 단어 단위

- 보조저장장치 = 블록(512B or 1KiB) 단위 -

주소지정 단위

1) 주소가 지정된 각 기억 장소 당 저장되는 데이터 길이

2) 바이트 단위 혹은 단어 단위

3)

주소 비트의 수 A, 주소지정 단위의 수 N

💍 데이터 전송률

- (1/액세스 시간) x (한 번에 읽혀지는 데이터 비트 수)

ex) 액세스 시간 = 100ns , 액세스 단위 = 32B인 경우,

데이터 전송률 = (1/100ns) * 32/8B = 40MB/sec

💎 계층적 기억장치 시스템

-

가격대비 성능비,

1) 액세스 속도가 높아질수록, 비트당 가격은 높아진다.

2) 용량이 커질수록, 비트당 가격은 낮아진다.

3) 용량이 커질수록, 액세스 시간은 길어진다. -

지역성의 원리

1) 기억장치의 액세스가 몇몇 영역에 집중되는 현상

2) 캐시의 경우 프로그램이 실행하는 곳 근처의 내용들을 가져와서 저장하고 있는다.

3) 지역성의 원리가 적용되는 경우, 평균 기억장치 액세스 시간이 단축됨 -

캐시 기억장치

- 주기억장치의 액세스 속도가 CPU에 비하여 현저히 느리기 때문에 주기억장치로부터 데이터를 읽어오는 동안에 CPU가 오랫동안 기다려야 하므로, 그에 따른 성능 저하를 줄이기 위하여 CPU와 주기억장치 사이에 설치하는 고속의 반도체 기억장치

💎 반도체 기억장치

- RAM 특성

1) 임의 액세스 방식

2) 반도체 직접회로 기억장치

3) 데이터 읽기와 쓰기가 모두 가능

4) 휘발성

💍 제조 기술에 따른 분류

-

DRAM : 집적 밀도가 높다 - RAM

-

SRAM : 속도가 빠르다 - 캐시