ARM Cortex-M 코어 레지스터: 펌웨어 개발자를 위한 핵심 개념 정리

임베디드 펌웨어 개발에 관심 있는 분들을 위해 ARM Cortex-M 프로세서의 핵심 레지스터와 실행 모드에 대한 내용을 정리해보았다.

CPU의 상태와 동작 방식을 파악하는 것은 안정적이고 효율적인 펌웨어 개발을 위해 반드시 이해해야 할 주제라고 생각한다.

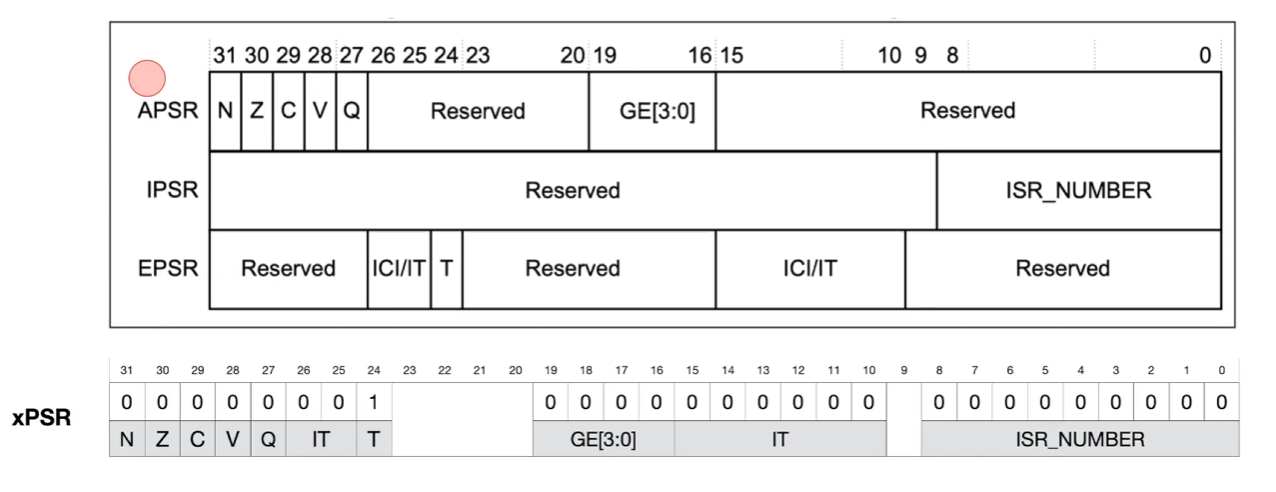

1. xPSR (Program Status Register)

xPSR은 ARM Cortex-M의 단 하나의 32비트 상태 레지스터.

다음의 세 가지 논리적 레지스터를 포함:

- APSR: Application Program Status Register

- IPSR: Interrupt Program Status Register

- EPSR: Execution Program Status Register

이들은 각각 독립된 레지스터가 아니라 xPSR의 일부 비트 영역을 의미.

1.1 APSR (Application Program Status Register)

ALU 연산 결과에 따른 플래그를 포함:

N (Negative): 연산 결과가 음수Z (Zero): 연산 결과가 0C (Carry): 캐리 발생 여부V (Overflow): 오버플로우 발생 여부Q (Saturation): 포화 연산 발생 여부

조건 분기(BEQ, BNE 등)에 직접적인 영향을 준다.

1.2 IPSR (Interrupt Program Status Register)

- 현재 실행 중인 예외 번호(ISR 번호)를 나타낸다.

- 디버깅 시, 어떤 인터럽트가 처리 중인지 판단할 수 있다.

1.3 EPSR (Execution Program Status Register)

- Thumb 상태 비트(T-bit): Cortex-M은 항상 Thumb 상태로 실행 (0이면 UsageFault 발생)

- ICI/IT 비트: IT(If-Then) 블록 상태를 저장

EPSR은 소프트웨어에서 직접 읽을 수 없음, 디버거를 통해 확인 가능하다.

1.4 오버플로우 & 세츄레이션 비트

V-flag: 부호 있는 정수 연산에서 범위 초과 시 1C-flag: 부호 없는 정수 연산에서 캐리 발생 시 1Q-flag: 포화 연산 발생 시 1 (예: QADD)

2. 스택 포인터 및 특수 레지스터

2.1 MSP (Main Stack Pointer)

- 리셋 이후 기본 스택

- 예외 핸들러 및 커널 코드가 사용하는 스택

- 시스템 생존에 핵심

유닉스의

PID 0과 같은 개념으로 볼 수 있습니다.

2.2 PSP (Process Stack Pointer)

- RTOS 환경에서 TASK 별 스택으로 사용

- 태스크 격리, 보안, 안정성 확보에 유리

언제 PSP가 꼭 필요한가?

- 필요 없음: 베어메탈에서

main()+ 인터럽트 구조만 사용할 때 - 필요함:

- 태스크 스택 격리

- 비특권 모드에서 실행 보장

- RTOS에서의 컨텍스트 스위칭 지원

3. 실행 모드 및 권한 제어 레지스터

3.1 CONTROL 레지스터

| 비트 | 이름 | 기능 |

|---|---|---|

| Bit 2 | FPCA | FPU 컨텍스트 활성화 여부 |

| Bit 1 | SPSEL | 스택 선택 (0: MSP, 1: PSP) |

| Bit 0 | NPRIV | Thread mode 권한 (0: Privileged, 1: Unprivileged) |

3.2 PRIMASK

- 모든 마스커블 인터럽트 비활성화

- NMI, HardFault는 예외

- Critical Section 보호에 사용

3.3 FAULTMASK

- HardFault까지 비활성화

- NMI만 허용

- 치명적 상황에서만 사용 권장

3.4 BASEPRI

- 설정된 우선순위 이하 인터럽트만 차단

- 세밀한 인터럽트 제어에 유용

4. 핵심 레지스터 요약

| Name | Type | Privilege | Reset Value | Description |

|---|---|---|---|---|

| R0-R12 | Read-Write | Either | Unknown | General-purpose registers |

| MSP | Read-Write | Privileged | See desc. | Main Stack Pointer |

| PSP | Read-Write | Either | Unknown | Process Stack Pointer |

| LR | Read-Write | Either | 0xFFFFFFFF | Link Register |

| PC | Read-Write | Either | See desc. | Program Counter |

| PSR | Read-Write | Privileged | 0x01000000 | Program Status Register (xPSR alias) |

| APSR | Read-Write | Either | 0x00000000 | Application PSR |

| IPSR | Read-Only | Privileged | 0x00000000 | Interrupt PSR |

| EPSR | Read-Only | Privileged | 0x01000000 | Execution PSR |

| PRIMASK | Read-Write | Privileged | 0x00000000 | Priority Mask Register |

| FAULTMASK | Read-Write | Privileged | 0x00000000 | Fault Mask Register |

| BASEPRI | Read-Write | Privileged | 0x00000000 | Base Priority Mask Register |

| CONTROL | Read-Write | Privileged | 0x00000000 | Control Register |

결론

ARM Cortex-M의 xPSR, 특수 레지스터, MSP/PSP 구조를 명확히 이해하면,

- 디버깅 능력

- RTOS 설계 적응력

- 시스템 보안 및 안정성 확보

에 강력한 기반을 갖출 수 있습니다.

깊이 있는 이해는 단순한 지식 습득이 아니라, 문제를 해결하고 설계할 수 있는 역량으로 이어진다.