FPGA 보드에 microblaze 시스템을 만들어 올려보자. 프로세서 위에 Hello world Application을 실행시키는 것까지 해보자.

1. 개발 환경

개발 환경은 아래와 같다.

- Digilent Arty-A7-100T

- Vivado 2022.02 on Windows 10

- Vitis 2022.02 on Windows 10

2. Vivado, Vitis 설치

Vivado와 Vitis를 설치해야 한다.

Vitis를 설치하면 자동으로 Vivado도 같이 설치되기 때문에, Vitis 인스톨러만 다운로드하여 실행하면 된다.

아래 링크에서 Xilinx Vitis 최신 버전을 받을 수 있다.

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vitis.html

3. Vivado 프로젝트 생성

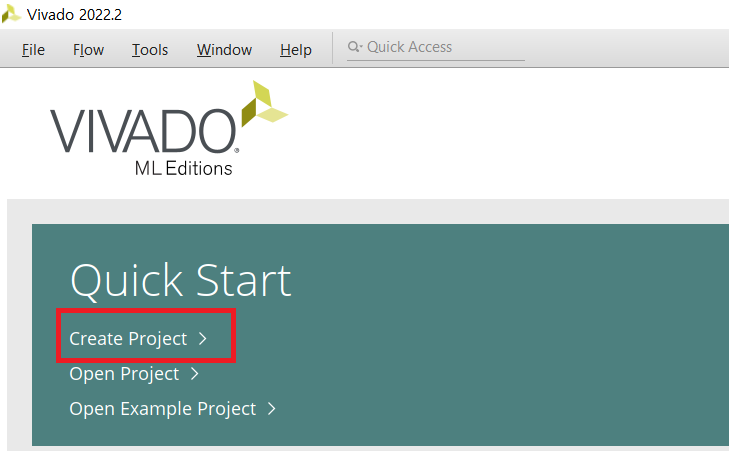

Vivado 실행 후 Create Project를 클릭한다.

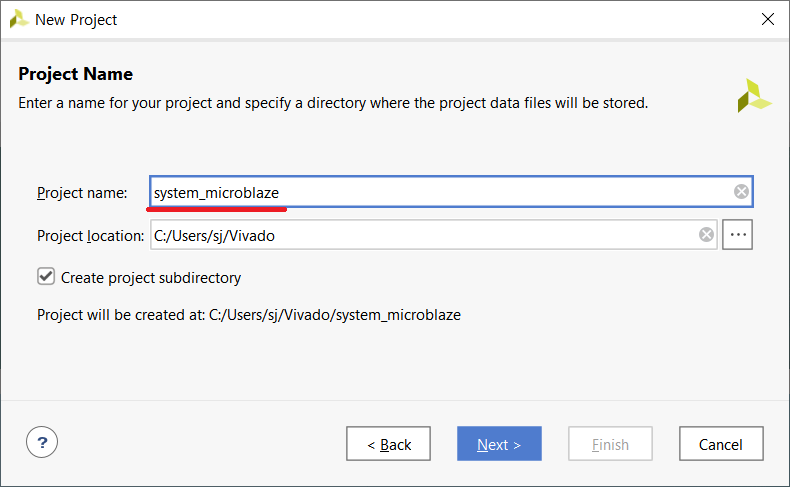

프로젝트 이름을 적절히 입력한 후 Next를 누른다.

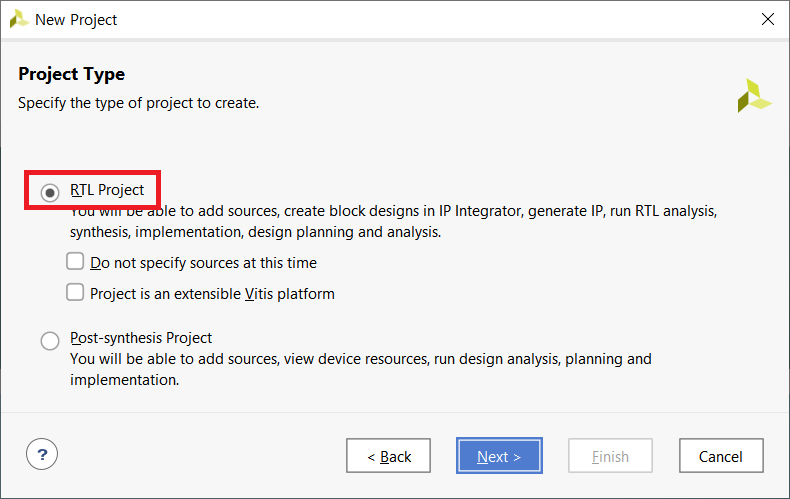

RTL Project로 생성한다.

Add Sources 와 Add Constraints 는 Next를 눌러 넘어간다.

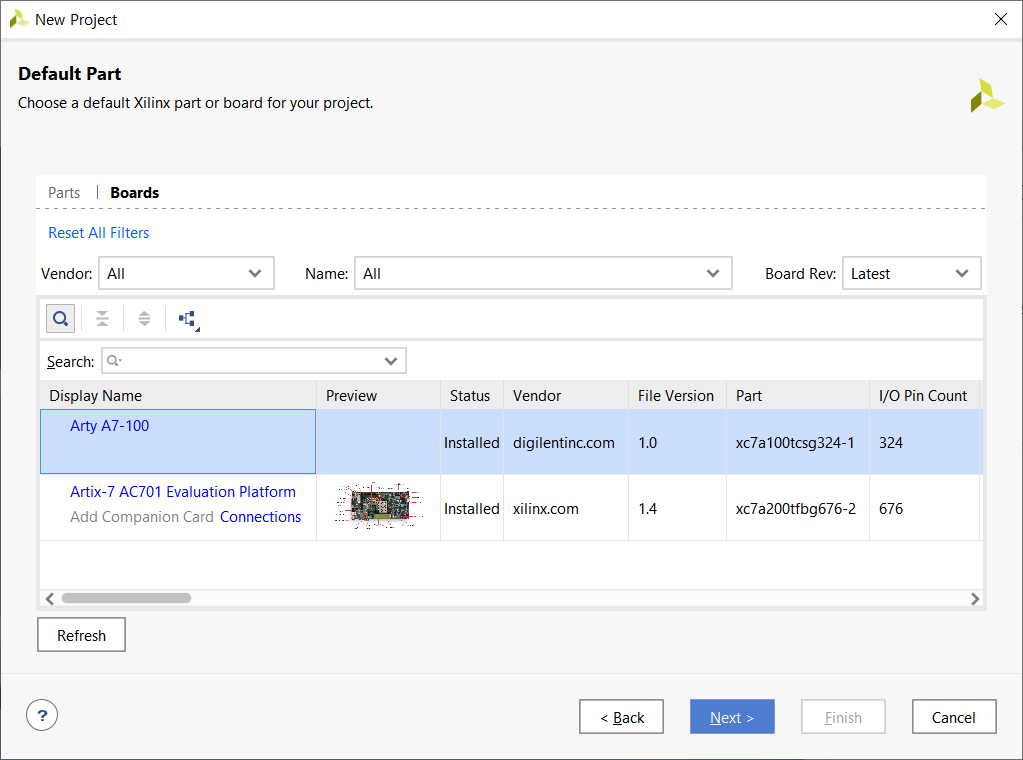

Default Part 에서 Arty-A7-100 보드를 검색하여 선택한 후 Next를 누른다.

그리고 Finish를 눌러 프로젝트를 생성한다.

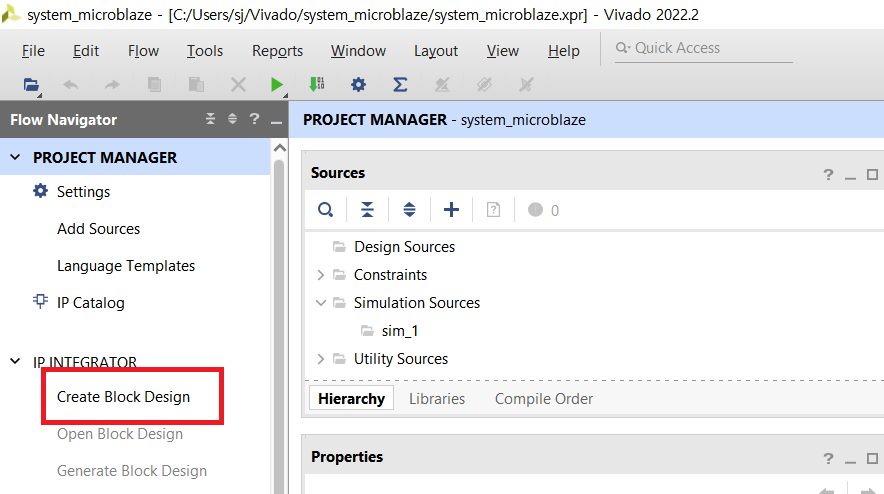

4. Block Design

Flow Navigator의 IP INTERGRATOR에서 Create Block Design을 누른 후 OK를 눌러 Block Design을 생성한다.

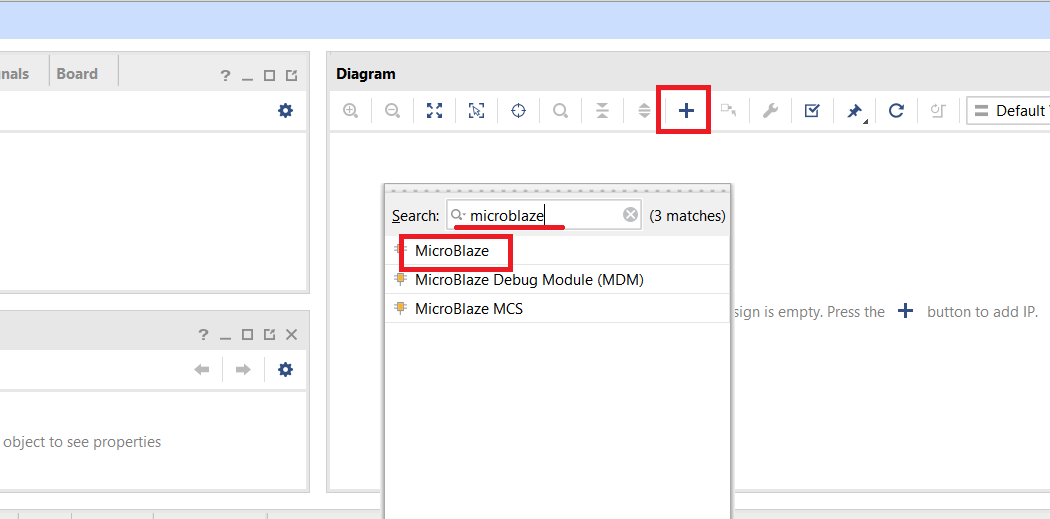

4-1. Microblaze 추가

Diagram에서 Add IP 버튼을 누르고 Microblaze를 검색한 후 더블 클릭하여 추가한다.

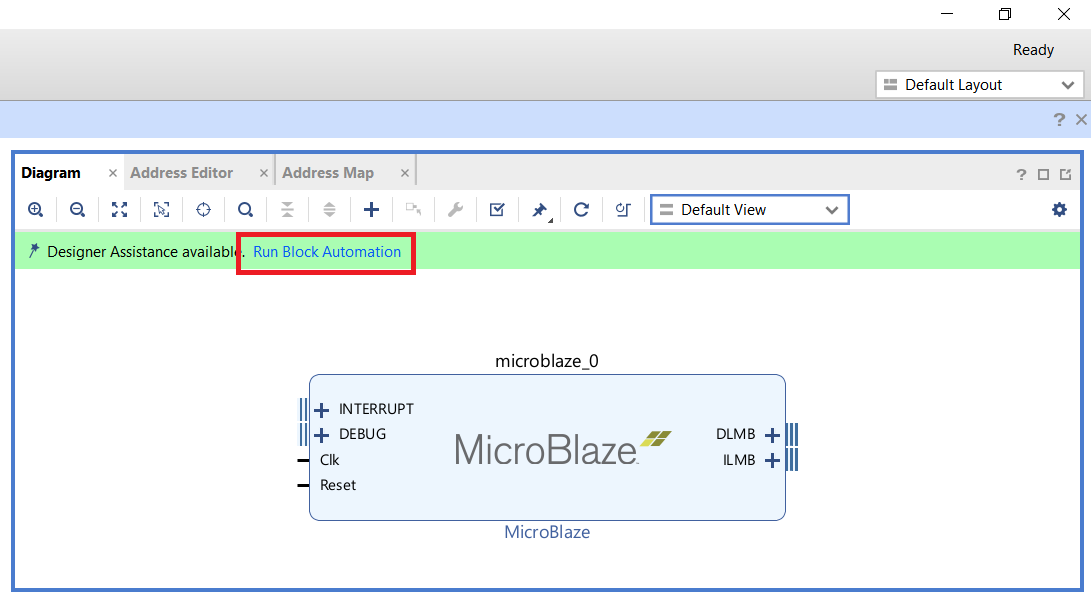

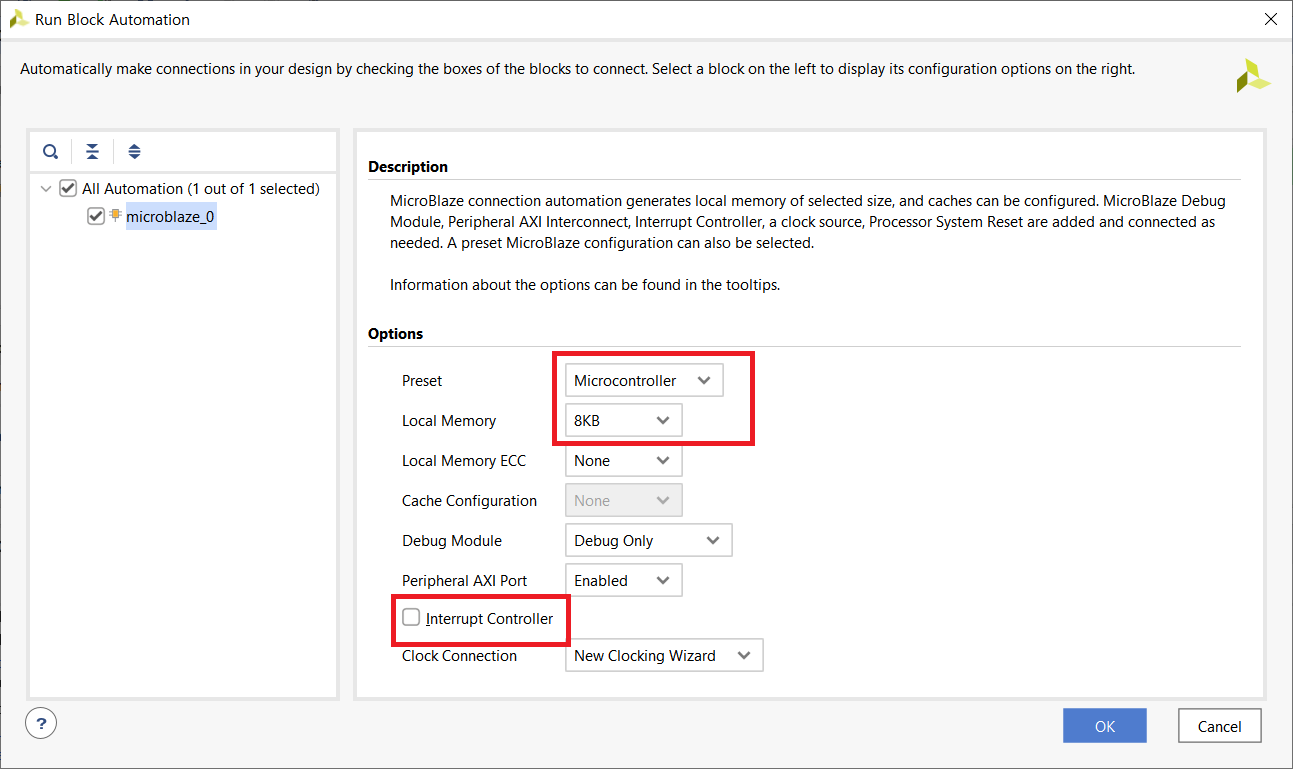

그리고 Run Block Automation을 누른다.

여기서 Preset을 Microcontroller로 해준다. Local Memory는 8KB 그대로 해줘도 되도 늘려도 된다. (본 글에서는 8KB 이상이 필요하진 않다.)

Interrupt Controller도 안 쓸 거라서 우선 체크 해제하였다.

설정한 후에 OK를 누른다.

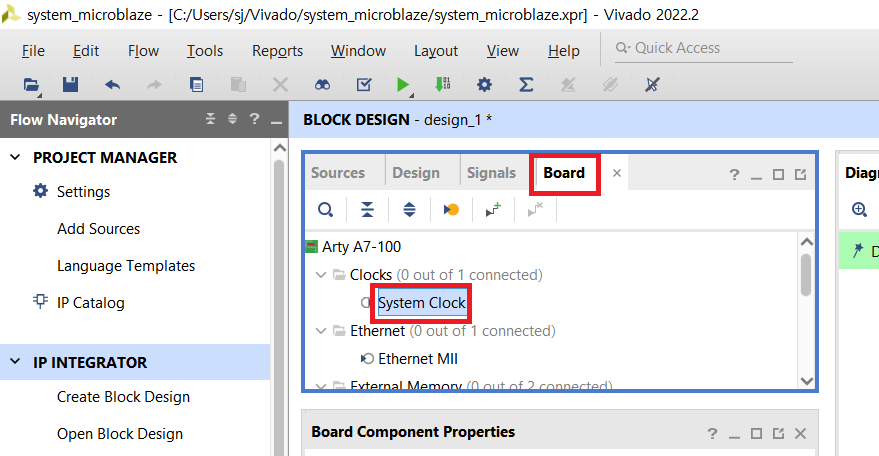

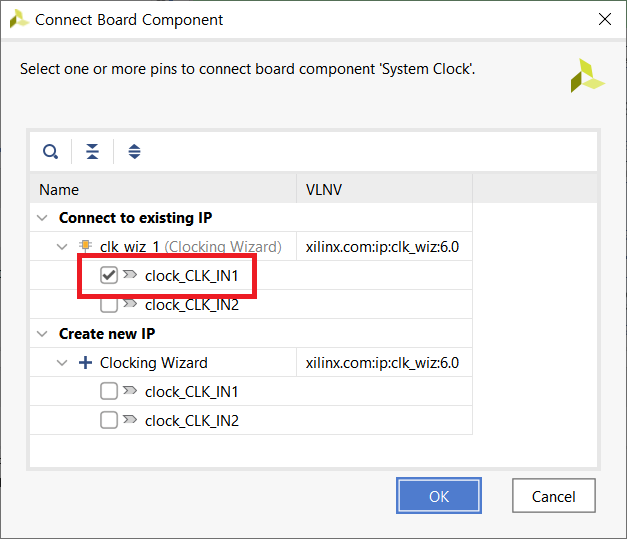

4-2. System Clock 추가

Block Design의 Board 탭에서 System Clock을 더블 클릭하여 추가해준다.

기본 설정 그대로 둔 후 OK를 누른다.

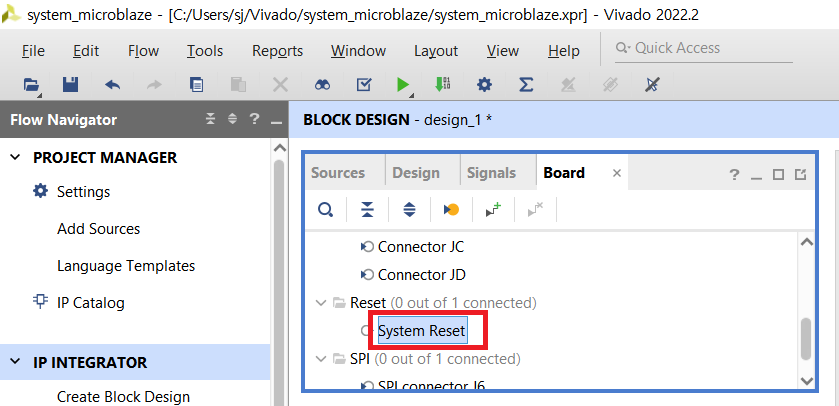

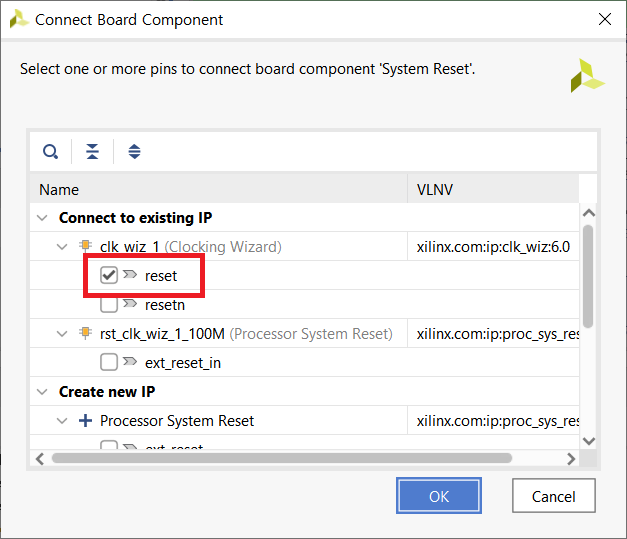

4-3. System Reset 추가

Board 탭에서 System Reset을 더블 클릭하여 추가한다.

기본 설정 그대로 둔 후 OK를 누른다.

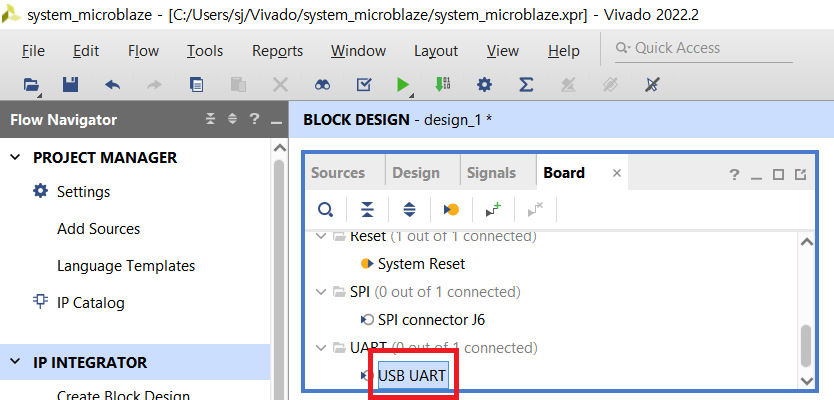

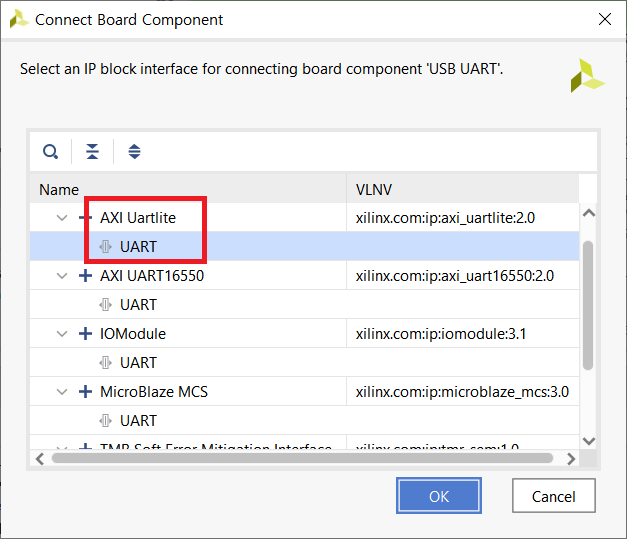

4-4. USB Uart 추가

Board 탭에서 USB UART를 더블 클릭하여 추가한다.

여담이지만, Arty-A7 보드의 USB Controller가 라인이 FPGA의 UART랑 JTAG 포트에 모두 연결되어 있어서, USB를 통해서 UART도 되고 JTAG도 된다고 한다. (참고)

기본 설정 그대로 AXI UartLite로 설정한 후 OK를 누른다.

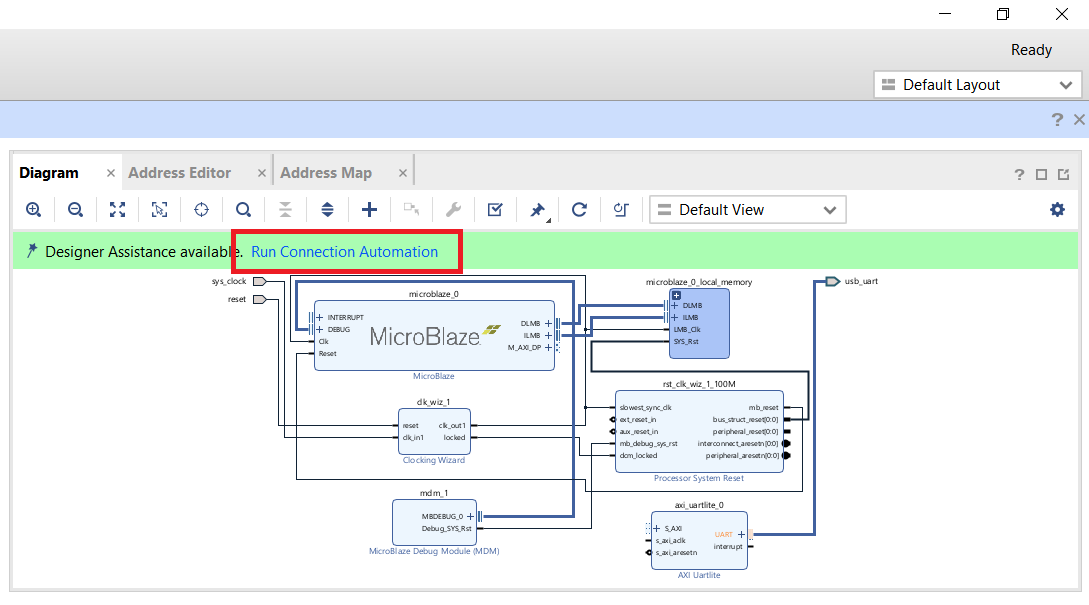

4-5. 모듈 연결

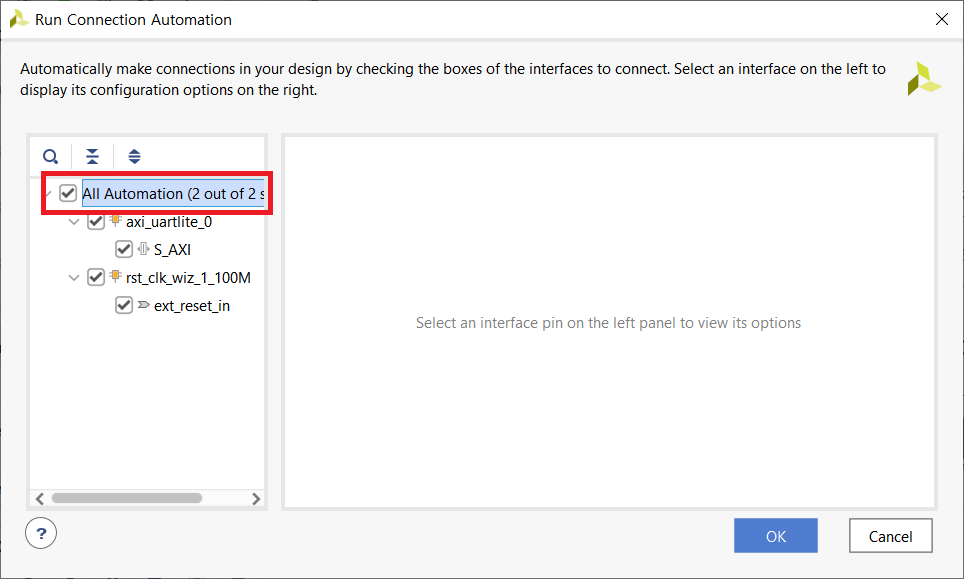

추가할 만한 모듈은 다 추가하였으니 Run Connection Automation을 누른다.

All Automation에 체크한 후 OK를 누른다.

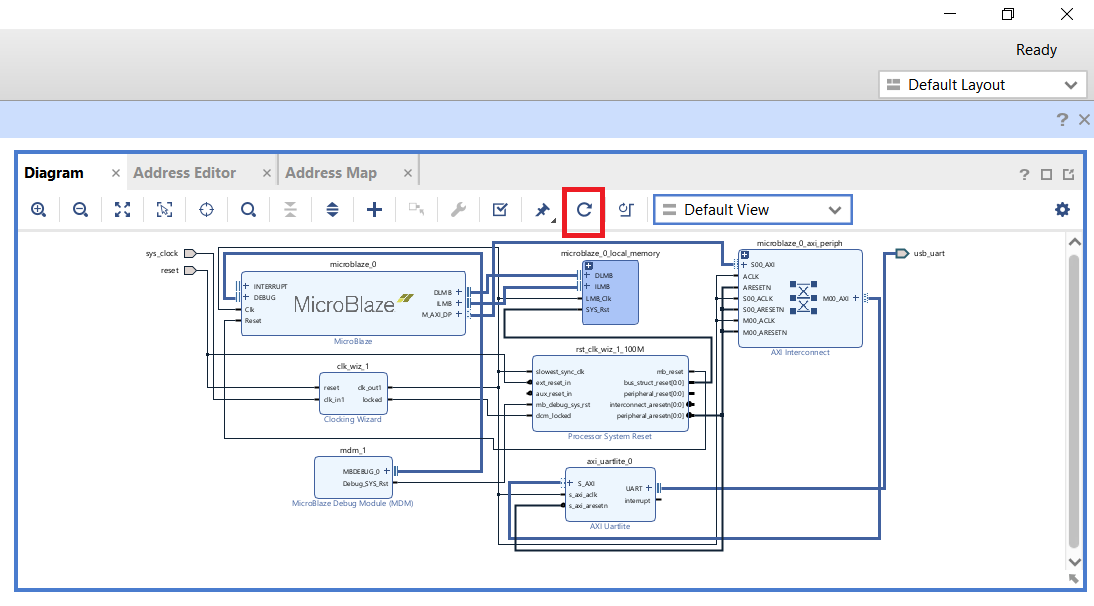

거의 다 완성되었다. Regenerate Layout 버튼을 누른다.

그럼 아래처럼 모양이 이쁘게 정리된다.

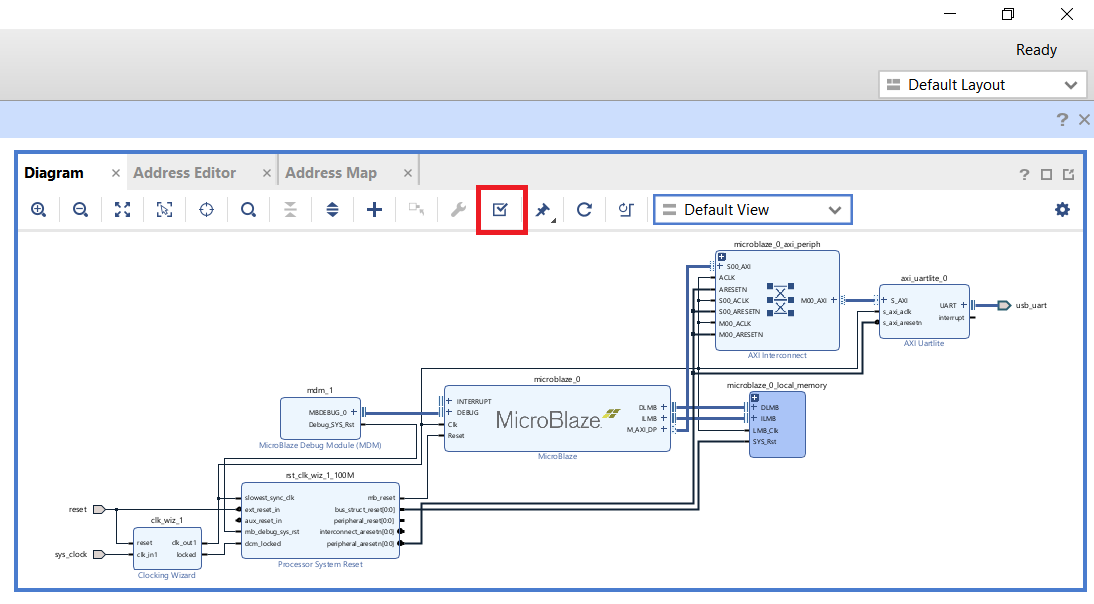

그리고 Validate Design 버튼을 눌러서 Design에 문제가 없는지 확인한다.

5. H/W Design 수정

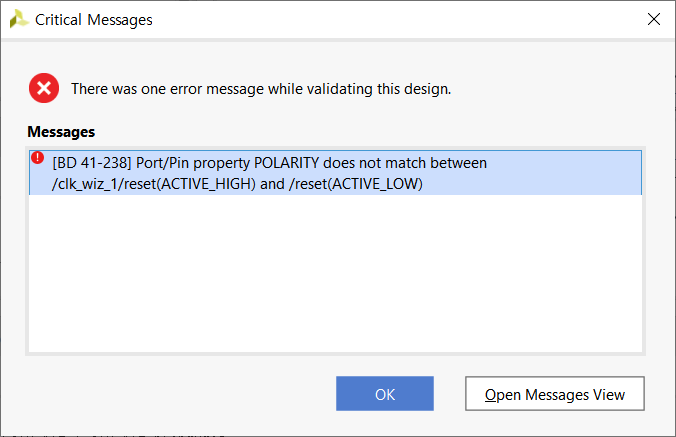

아마 Arty-A7 보드라면 아래와 같이 에러가 날 것이다.

[BD 41-238] Port/Pin property POLARITY does not match between

/clk_wiz_1/reset(ACTIVE_HIGH) and /reset(ACTIVE_LOW)

에러가 나는 이유는 핀 마다의 동작 레벨이 다르기 때문이다.

보드의 리셋 핀은 Active Low인데 반해 Clocking Wizard의 reset은 Active High로 되어있다. 또 Processor System Reset의 ext_reset_in은 Active Low로 되어있다.

얘네 간의 Polarity를 맞춰주어야 한다. 결론부터 말하면 보드의 리셋 핀과 Clocking Wizard의 reset 사이에 NOT 게이트를 넣어주면 된다.

당장 이 에러뿐만 아니라도, 나중에 아래의 에러가 나오는 것을 미리 방지하기 위해 본 작업을 해주어야 한다.

Cannot stop MicroBlaze. MicroBlaze is held in reset.5-1. NOT Gate 추가

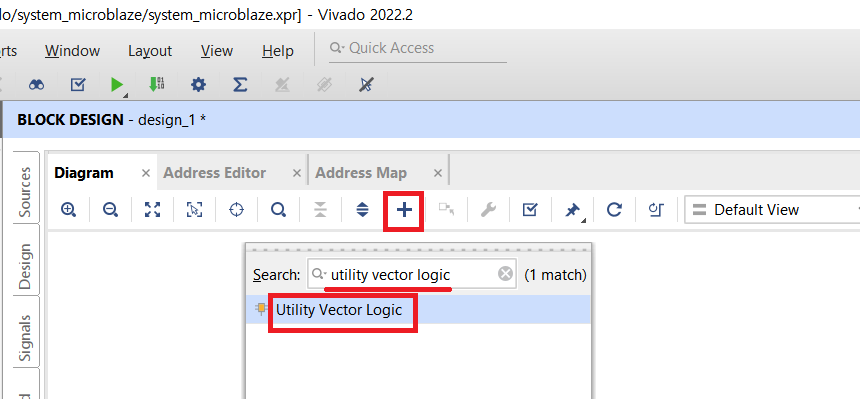

NOT 게이트를 넣는 방법은 간단하다. Diagram 창에서 Add IP를 누른 후 Utility Vector Logic을 검색한 후 더블 클릭한다.

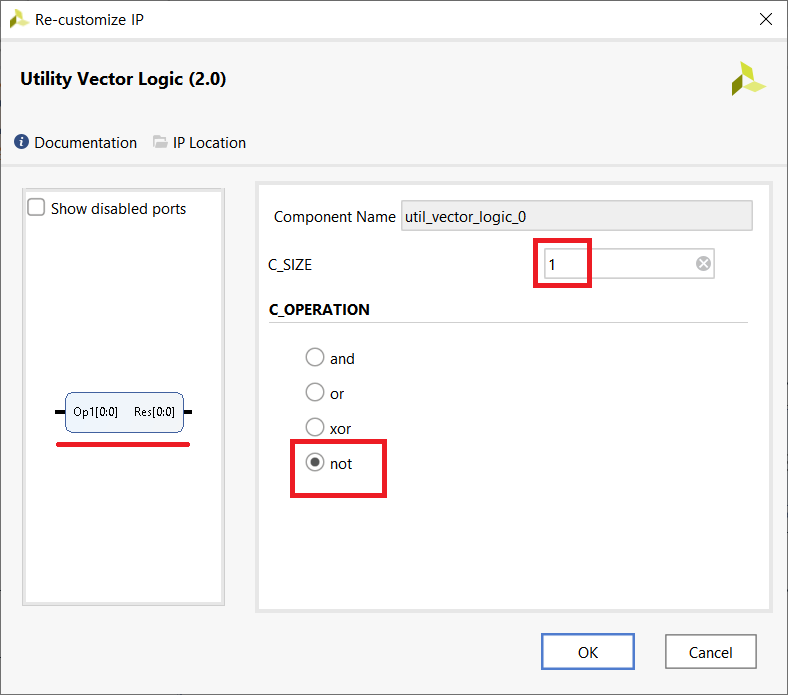

생성된 Utility Vector Logic을 더블 클릭하여 아래와 같이 설정한다.

not 왼쪽의 라디오 버튼을 클릭하고, C_SIZE를 1로 설정한 후 OK를 누른다.

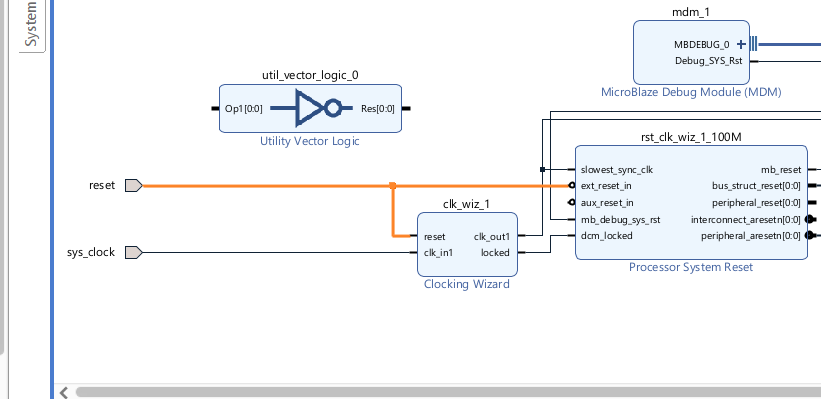

보드의 리셋 핀과 연결된 라인을 오른쪽 클릭한 후 삭제한다.

그리고 리셋 라인을 아래와 같이 연결해준다. 그러면 각 리셋 핀의 Polarity를 그대로 유지한 채 원하는 신호를 전달할 수 있다.

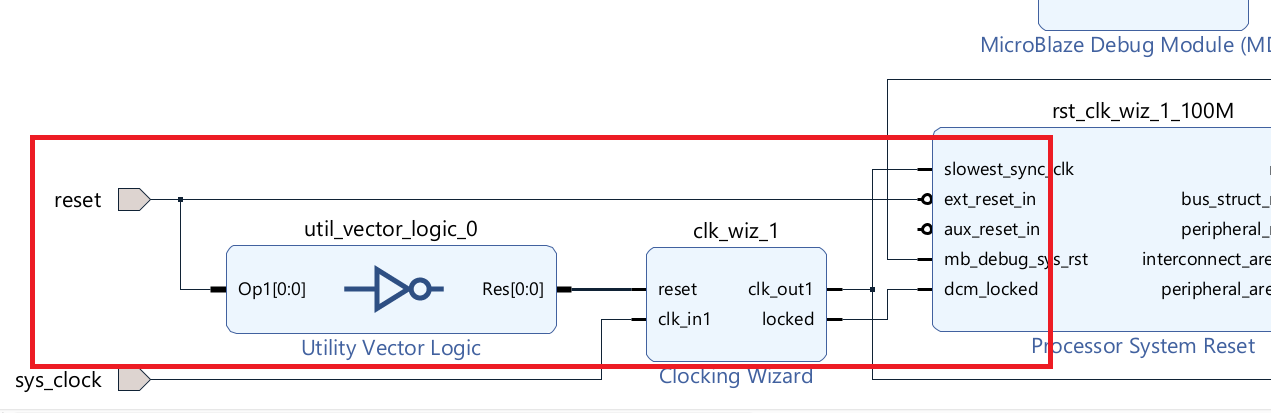

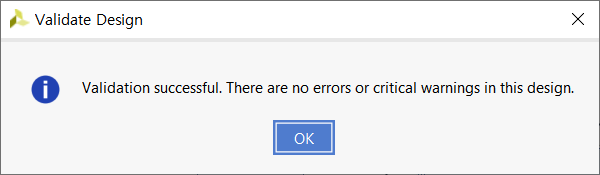

Regenerate Layout을 누른 후 Validate Design을 누른다. 그러면 아래와 같이 Validation Successful이라고 뜬다.

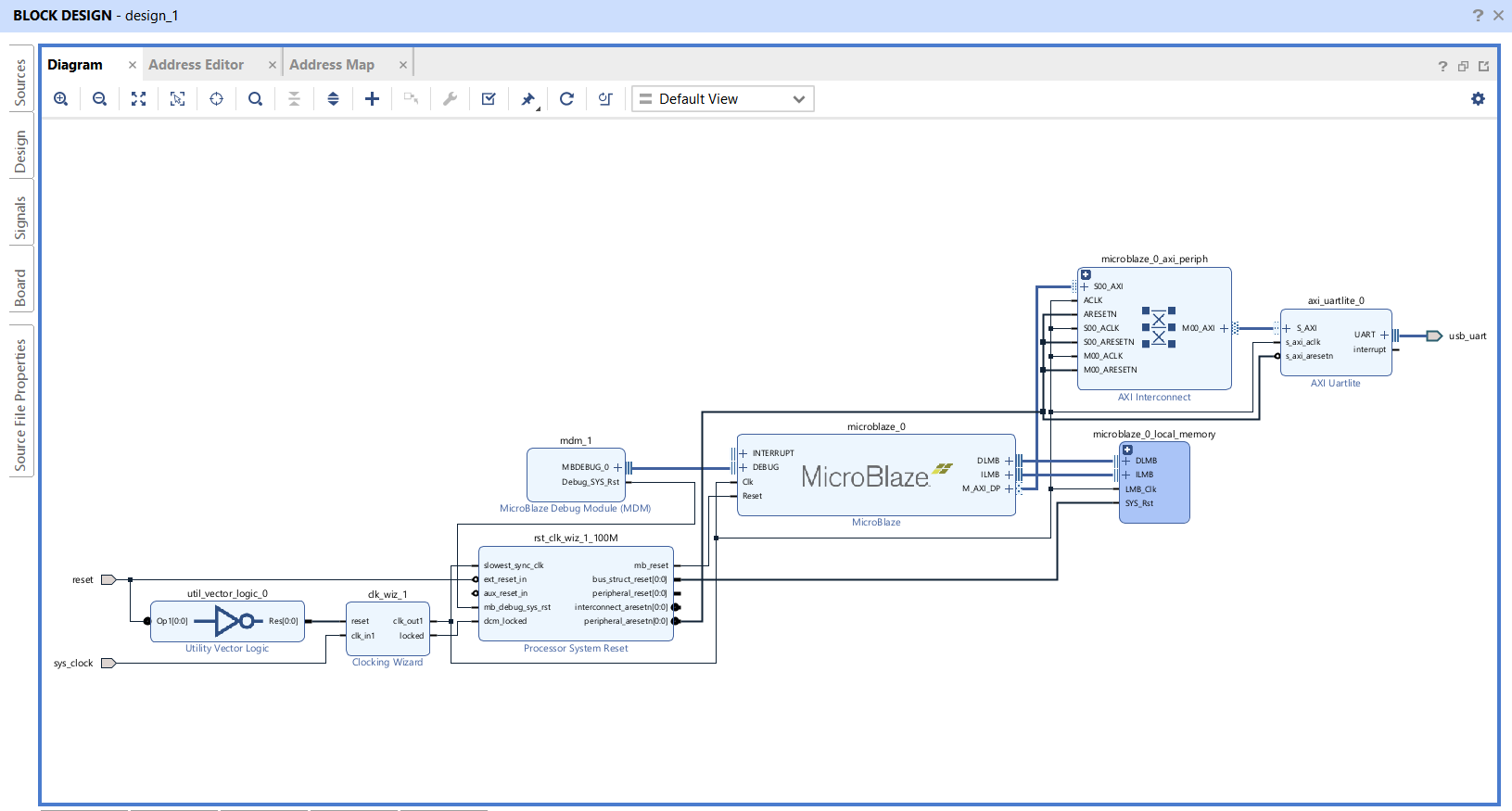

최종 완성된 Design은 아래와 같다.

Ctrl + S를 눌러 저장한다.

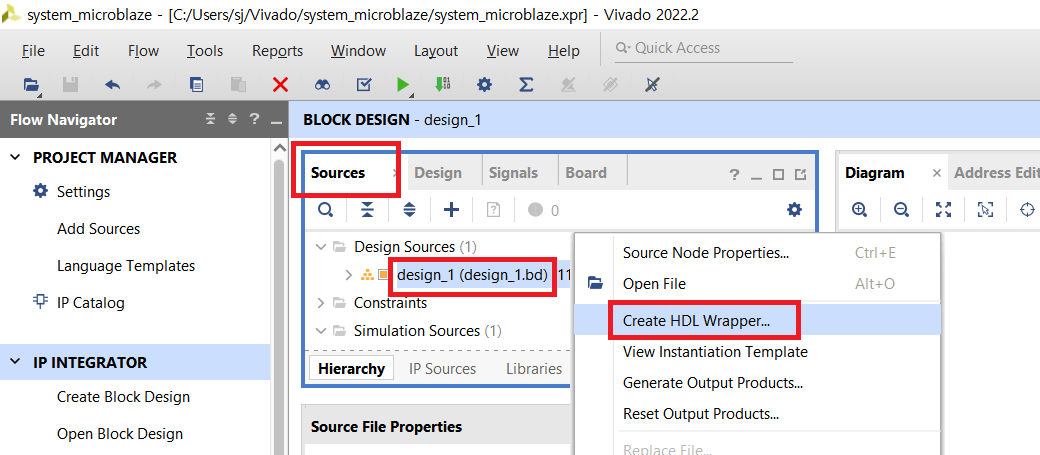

6. HDL Wrapper 생성

Sources 탭에서 Design Sources에 있는 *.bd 파일을 오른쪽 클릭한 후 Create HDL Wrapper를 누른다.

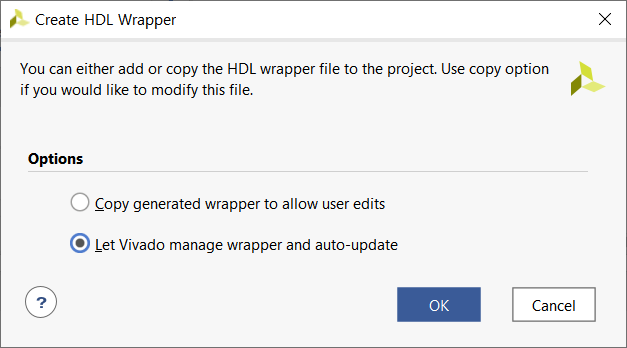

그리고 OK를 누른다.

그러면 위 Microblaze 시스템이 하나의 HDL 모듈 형태로 만들어진다.

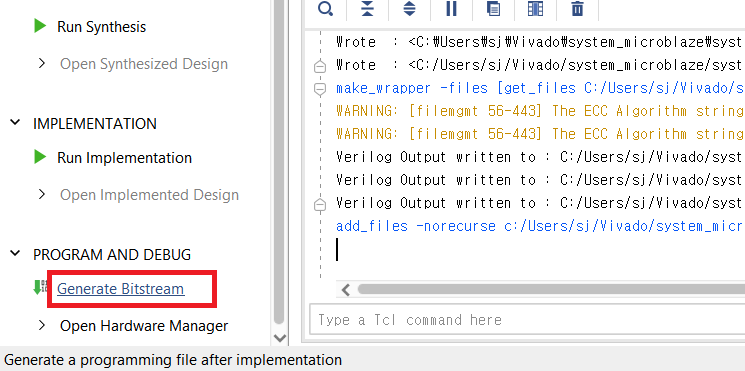

7. Bitstream 생성

Flow Navigator의 PROGRAM AND DEBUG에서 Generate Bitstream을 누르고 OK를 누른다.

그러면 우리가 위에서 만든 HDL 모듈이 합성 및 구현을 거쳐 Bitstream으로 만들어진다.

만드는 데 약 15분 정도 걸린다.

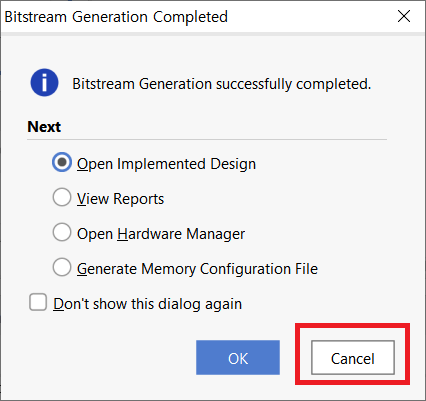

Bitstream 생성이 완료되면 아래와 같이 창이 뜬다. 여기서 Cancel을 눌러주자.

8. XSA 파일 내보내기

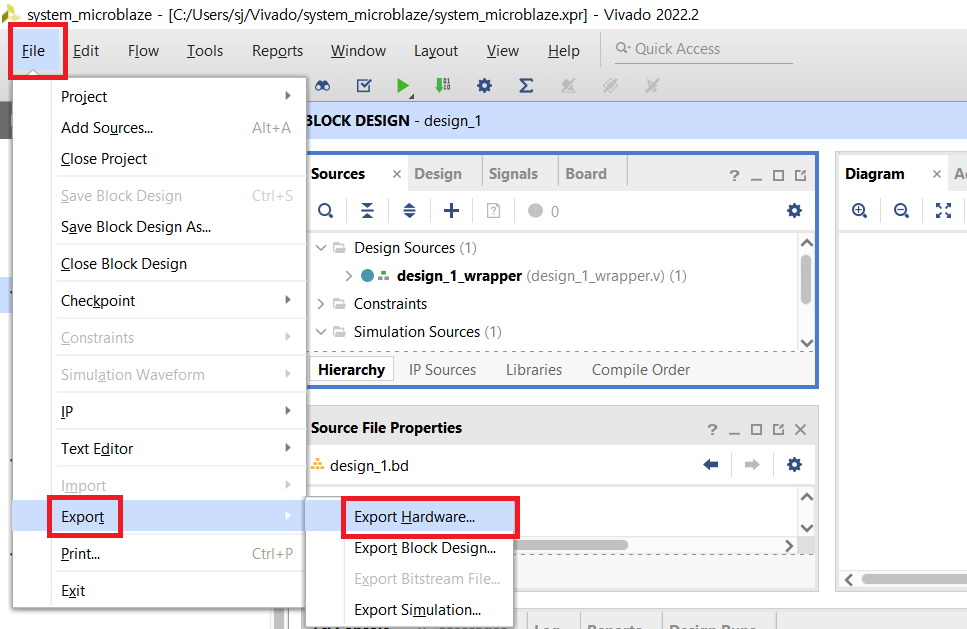

Bitstream 생성이 완료되면 File > Export > Export Hardware를 누른다.

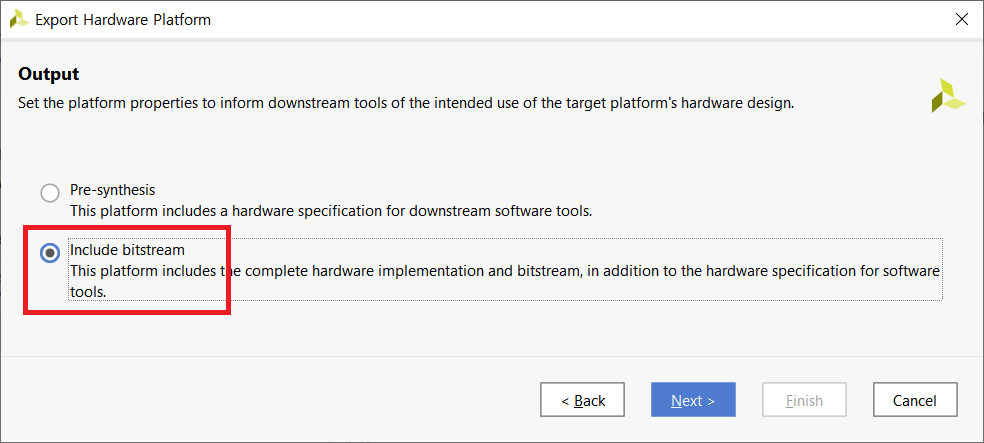

Output에서 Include bitstream을 선택한 후 Next를 누른다.

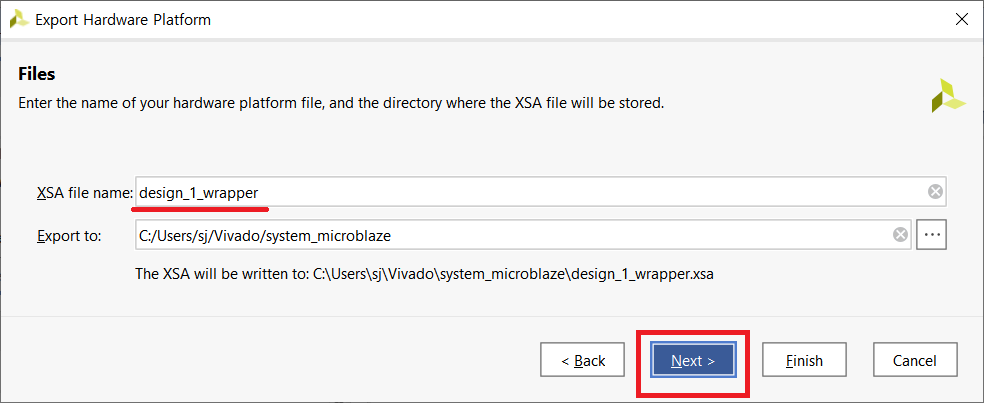

내보낼 XSA 파일 이름을 적절히 입력한 후 Next를 누른다.

그리고 Finish를 눌러 마무리하면 Vivado에서 해줄 작업은 끝났다.

이후 작업 중에 메모리를 늘리고 싶거나 하드웨어 구성을 바꾸고 싶은 경우, Vivado에서 자유롭게 수정한 후 위 과정을 그대로 수행해주면 된다. Bitstream 재생성 및 XSA 파일을 내보내기 하여 Vitis에서 불러오면 된다. 그리고 Vitis Project를 재빌드해주면 된다.

Vitis 사용법은 다음 글에서 작성하겠다.

다음 글 : https://velog.io/@pikamon/FPGA-4

참고

아래 페이지들을 참고하여 작성하였다.

https://blog.naver.com/chcbaram/222425158237

(좋은 글 감사합니다!)

https://www.fpgadeveloper.com/2017/11/artix-7-arty-base-project.html/

https://www.hackster.io/whitney-knitter/hello-microblaze-on-arty-a7-70d9e1

안녕하세요. 2년 전 글이지만 너무나 유익하게 참고하고 있습니다. 혹시 port와 실제 board에서 사용하는 pin을 mapping하기 위한 .xdc 파일은 따로 생성하지 않으신건가요?