PML4

PML4는 x86_64 아키텍처에서 사용하는 4단계 페이지 테이블의 가장 상위 레벨입니다.

즉, 64비트 가상 주소 → 물리 주소 변환 시, PML4는 첫 번째 인덱스로 접근되는 테이블입니다. (PML4는 "주소 변환의 첫 번째 인덱스")

필요성

64비트 주소는 최대 2⁶⁴개의 주소 공간을 다룰 수 있습니다. 하지만, 현실에서는 그렇게 큰 테이블을 한 번에 만수 없기 때문에, 4단계로 나누어 계층적으로 접근합니다. 이 구조는 페이지 테이블을 부족하게 만들고, 메모리를 절약할 수 있게 해줍니다.

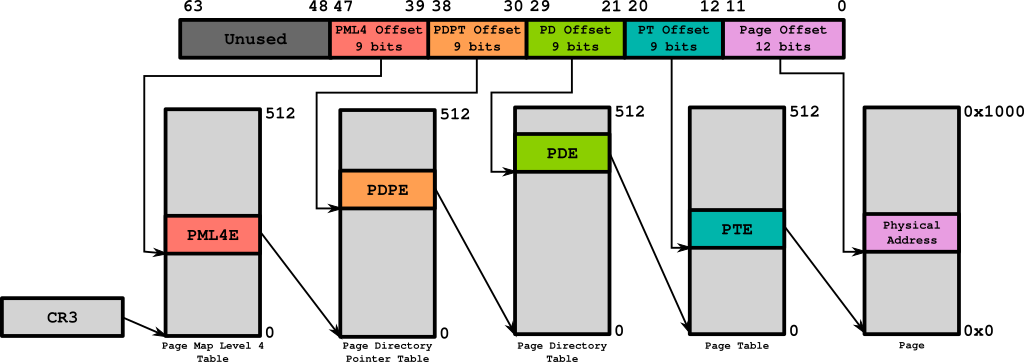

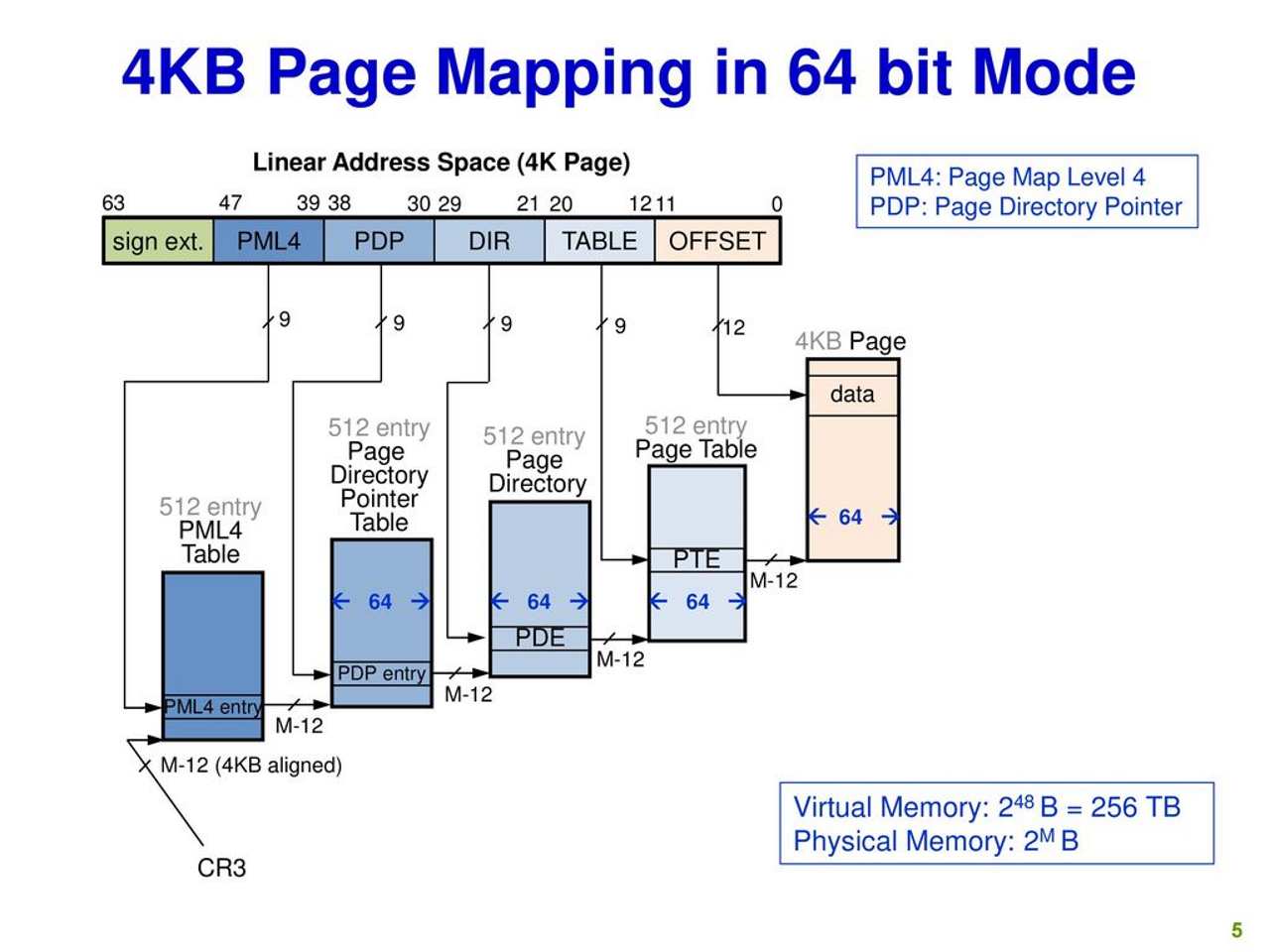

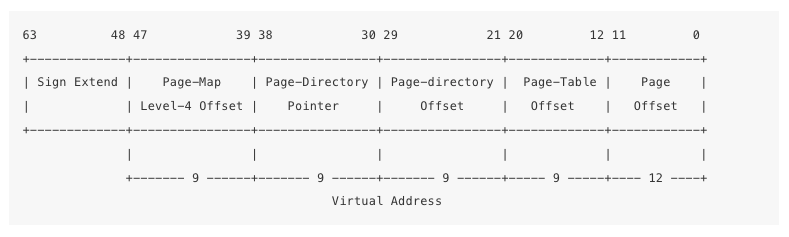

주소 변환 구조 (x86-64)

가상 주소 48비트는 다음과 같이 나뉩니다.

| 비트 범위 | 테이블 | 설명 |

|---|---|---|

| 47–39 | PML4 index | 최상위 테이블 |

| 38–30 | PDPT index | Page Directory Pointer Table |

| 29–21 | PD index | Page Directory |

| 20–12 | PT index | Page Table |

| 11–0 | offset | 페이지 내 오프셋 (보통 4KB 페이지) |

주소 변환은 다음과 같은 순서로 진행됩니다.

- PML4 (최상위 테이블) → 512 엔트리 중 하나 선택

- PDPT (페이지 디렉터리 포인터 테이블) → 엔트리 선택

- PD (페이지 디렉터리) → 엔트리 선택

- PT (페이지 테이블) → 엔트리 선택

- 페이지 내 offset으로 실제 데이터 위치 계산

Pintos에서…

Pintos는 64비트 기반 OS이므로, 4단계 페이지 테이블(PML4 구조)를 사용합니다. 밑에 있는 pintos VA를 보면 Page-Map-Level-4 가 pml4 부분입니다.

다음과 구조체로 구현됩니다.

| 구조체 | 설명 |

|---|---|

struct pml4 *pml4 | 각 프로세스의 페이지 테이블 루트 |

pml4_activate() | 현재 실행 중인 프로세스의 PML4를 MMU에 등록 |

pml4_get_page() | 가상 주소 → 물리 주소 변환 |

pml4_set_page() | 새로운 VA → PA 매핑 등록 |

pml4_clear_page() | 매핑 해제 |

→ 이 함수들은 내부적으로 하드웨어의 CR3 레지스터를 갱신하거나, 4단계 구조를 순회합니다.

매핑 예시 코드

/* 사용자 가상 주소 0x8048000에 물리 프레임 kpage를 매핑 */

pml4_set_page(thread_current()->pml4, (void *)0x8048000, kpage, true);1번째 인자: 현재 프로세스의 pml4

2번째 인자: VA (가상주소)

3번째 인자: 물리 프레임 주소

4번째 인자: 쓰기 가능 여부

Page Fault에도 쓰이는 PML4

page_fault() 함수에서 다음과 같이 pml4 이 쓰입니다.

- faulting address (CR2 레지스터)를 읽습니다.

- PML4를 사용해 페이지 테이블을 검색합니다.

- 없으면

vm_try_handle_fault()로 처리합니다.

요약

| 항목 | 설명 |

|---|---|

| PML4란? | x86-64에서 페이지 테이블의 최상위 단계 |

| 역할 | 가상 주소를 4단계 트리를 통해 물리 주소로 변환 |

| 필요성 | 64비트 주소 공간을 계층적으로 관리하기 위해 |

| Pintos에서 사용처 | pml4_set_page(), pml4_get_page(), page_fault() 등 |

| 주소 변환 구조 | PML4 → PDPT → PD → PT → 실제 페이지 |