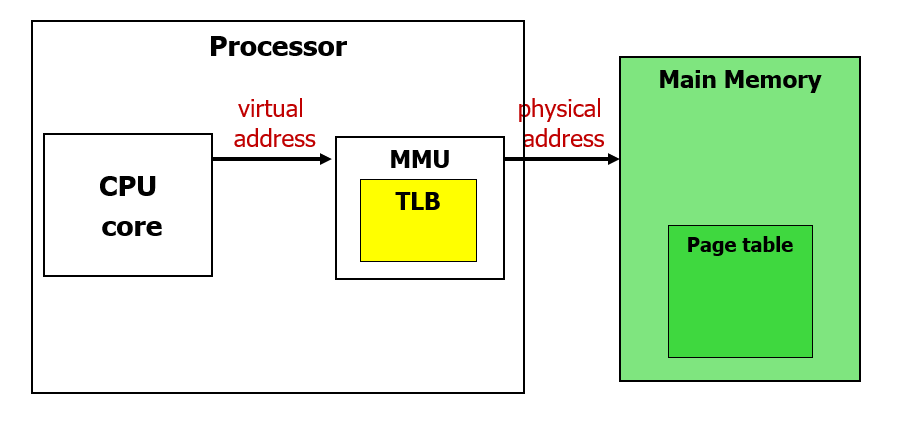

TLB(Translation Lookaside Buffer)

TLB는 가상 주소 → 물리 주소 변환 정보를 캐시해 놓는 하드웨어 캐시입니다.

주소 변환 시 매번 페이지 테이블을 참조하면 느리기 때문에, 자주 접근하는 페이지 매핑 정보를 빠르게 제공하기 위해 존재합니다.

→ [ TLB = 주소 변환 캐시 ] 라고 생각하면 좋습니다.

필요성

페이지 테이블 탐색은 메모리 접근이 여러 번 필요하기 때문에 느릴 수 있습니다. 특히 x86-64에서는 4단계 페이지 테이블 구조를 사용하기 때문에 사용합니다.

하나의 VA 변환 = 최대 4번의 메모리 접근 필요

→ 그래서 자주 쓰는 VA 매핑을 TLB에 저장해두고, 먼저 확인합니다.

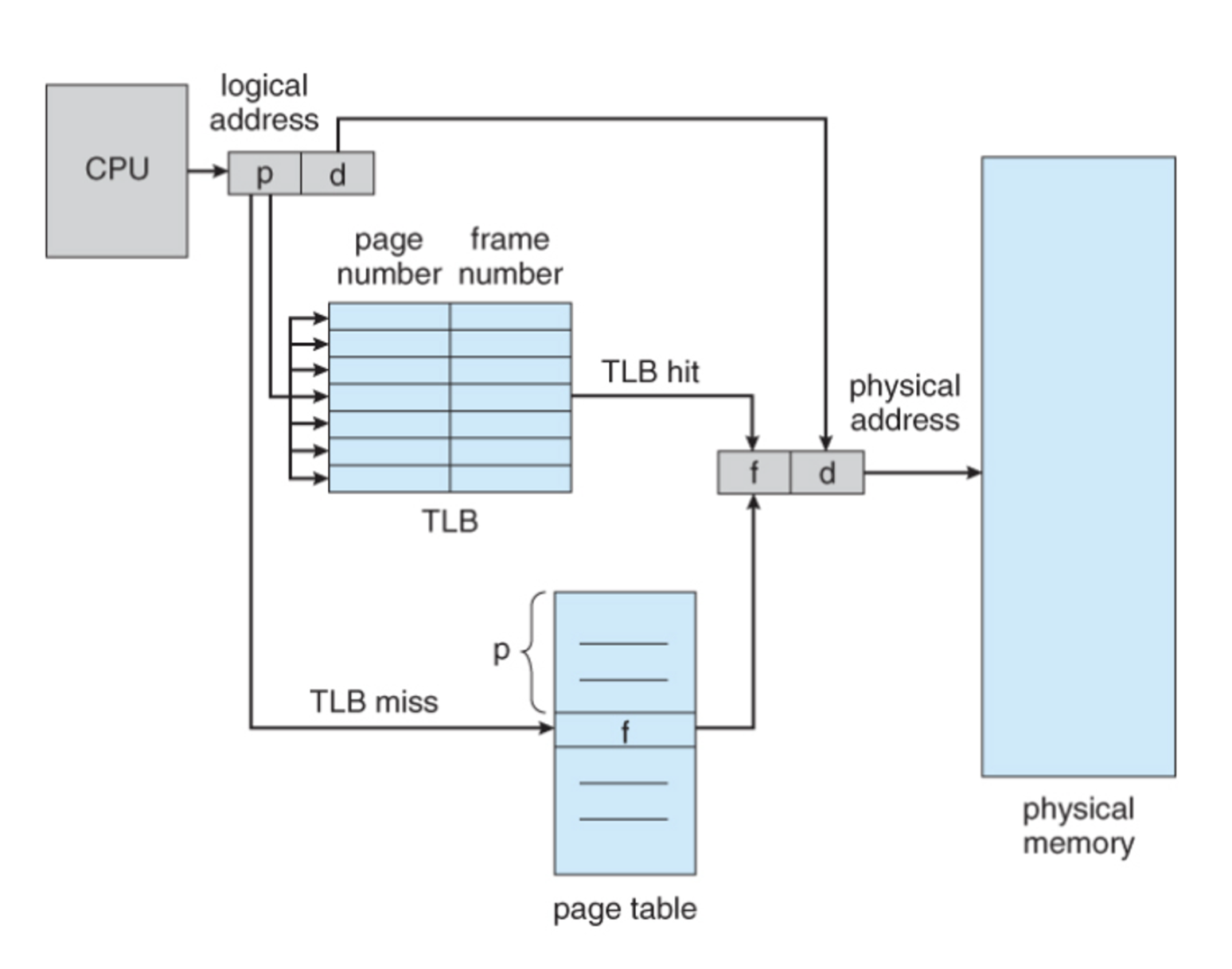

동작 흐름

- CPU가 가상 주소(VA)를 생성

- TLB에서 해당 VA의 페이지 번호(VPN) 매핑을 검색

- 있으면 (TLB hit): 물리 주소(PA)를 즉시 얻음

- 없으면 (TLB miss)

- 페이지 테이블 참조

- VA → PA 변환

- 변환 결과를 TLB에 저장 (캐싱)

- 이후 재사용 가능

구조와 성능

- 작지만 빠른 캐시 (보통 수십 ~ 수백 개 항목)

- Context Switch 시 무효화(invalidate) 필요 → 프로세스마다 주소 공간이 다르기 때문입니다.

- 일부 CPU는 Process ID (PID) 기반 TLB를 지원해서 context switch 시에도 재사용 가능합니다.

Pintos 에서…

Pintos에서는 직접적인 TLB 구현은 없지만 암묵적으로 작동합니다.

- Pintos는 x86-64 하드웨어 기반에서 돌아가는 소형 커널입니다.

- TLB는 하드웨어가 자동으로 처리합니다.

- Pintos에서는 페이지 테이블만 관리하면 됩니다.

/* 페이지 테이블에 가상 주소와 물리 프레임을 매핑 */

pml4_set_page (pml4, upage, kpage, writable);→ 위 호출이 끝나면, 다음 VA 접근 시 TLB가 자동으로 업데이트 됩니다. (단, 현재 실행 중인 PML4와 일치할 경우)

Context Switch 시 고려 사항

Pintos에서는 새로운 프로세스가 실행될 때마다 pml4_activate()가 호출됩니다. 이때 하드웨어는 현재의 CR3 레지스터 (페이지 테이블 루트 주소)를 교체합니다. 즉, 기존 TLB의 내용은 대부분 무효화(invalidate) 됩니다.

/* 새 프로세스의 페이지 테이블 활성화 */

void

pml4_activate (struct pml4 *pml4) {

lcr3(vaddr_to_paddr(pml4));

}→ lcr3()를 호출하면 하드웨어가 TLB를 자동으로 비웁니다.

요약

| 항목 | 설명 |

|---|---|

| TLB란? | 가상 주소 → 물리 주소 매핑 정보를 저장하는 하드웨어 캐시 |

| 장점 | 빠른 주소 변환, 페이지 테이블 접근 횟수 감소 |

| 단점 | 제한된 용량, context switch 시 invalidation 필요 |

| Pintos에서의 처리 | pml4_set_page()로 매핑 생성, pml4_activate()로 context 전환 시 TLB 갱신 유도 |

| 직접 구현? | X. TLB는 하드웨어가 처리, Pintos는 페이지 테이블만 구성하면 자동 적용됨 |