Paging

- 시간적 오버헤드가 크다

- Address translation이 너무 느림

- 목표 : address translation을 빠르게 하는 것

TLB (Translation Lookaside Buffer)

-

CPU -> Logical Address -(TLB Lookup)-> MMU -> TLB Miss시 Page Table, TLB Hit시 Physical Address -> Physical Memory

-

logical address에서 page number은 process마다 있음

TLB Performance

- Effective Access Time With TLB

- TLB Lookup time : e

- Memory Access time : 1

- Hit ratio : a (TLB에서의 Percentage)

- = (1+e)a + (2+3)(1-a)

= 2+e-a

TLB Basic Algorithm

VPN = (VirtualAddress & VPN_MASK ) >> SHIFT

(Success , TlbEntry) = TLB_Lookup(VPN)

if(Success == Ture){ // TLB Hit (TLB에 변환 정보 존재할 시)

if(CanAccess(TlbEntry.ProtectBit) == True ){ // 접근 가능한지 확인 후 TLB 정보로 주소 변환

offset = VirtualAddress & OFFSET_MASK

PhysAddr = (TlbEntry.PFN << SHIFT) | Offset

AccessMemory( PhysAddr )

} else

RaiseExceotion(PROTECTION_ERROR)

else // TLB에 변환 정보 없을 때

PTEAddr = PTBR + (VPN * sizeof(PTE)

PTE = AccessMemory(PTEAddr)

(--)

TLB_Insert( VPN , PTE.PFN , PTE.ProtectBits) //TLB에 변환 정보 저장

RetryInstruction()

}

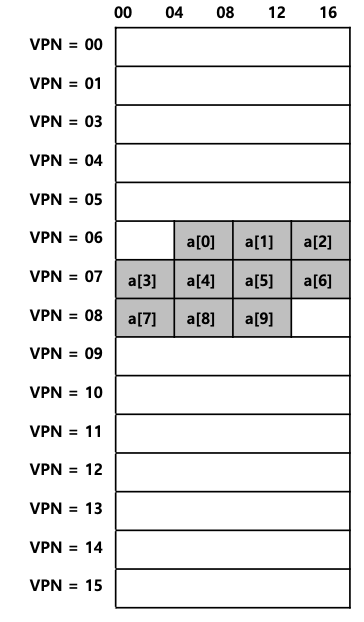

} - Accessing An Array

: 첫번째 array[0]에 접근 시 TLB에 아무런 address가 cache 되어있지 않음. 그런데 a[1]에 접근하면 같은 page가 TLB에 cache 되어있어 빠르게 찾기 가능

-> a[0], a[3], a[7]모두 같은 현상이고 나머지 7번의 접근, 즉 70%에서 TLB Hit 발생 (배열이 연속된 주소공간에 있어 Spatial Locality라 함)

Locality

(program간, program 내에서도 Locality 존재)

- Temporal Locality : 참조했던 걸 다시 참조

- Spatial Locality : 주소 x에 접근 시, x의 근처로 접근

TLB entry

: TLB는 Full Association(결합된) 방법으로 관리됨

- 32 / 64 / 128 entry 가짐

- HW에선 원하는 translation 찾기 위해 전체 TLB를 병렬로 검색

- Typical TLB : VPN & PFN & other bits

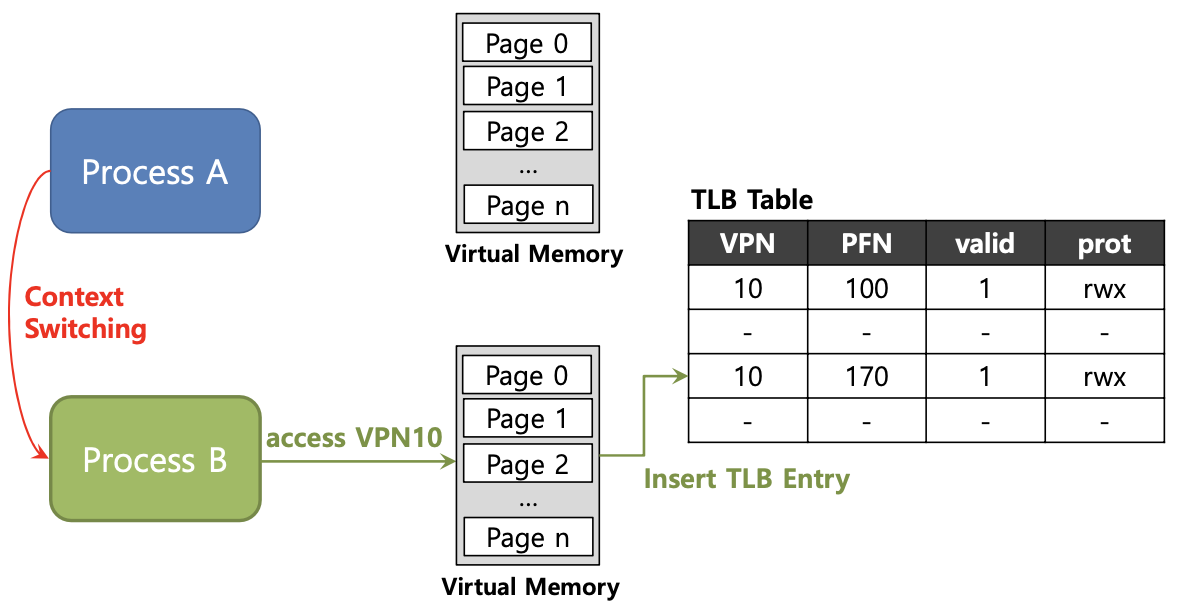

TLB Issue : Context Switching

: process A, B의 VPN가 10으로 동일하지 PFN이 다름 -> TLB에 정보 저장 시 어떤 정보가 어떤 프로세스의 정보인지 알 수 없음

- 해결 방법

- Context Switch 발생 시 기존 process의 주소변환 정보를 flush (모두 지워버림) -> 추가적인 비용 발생

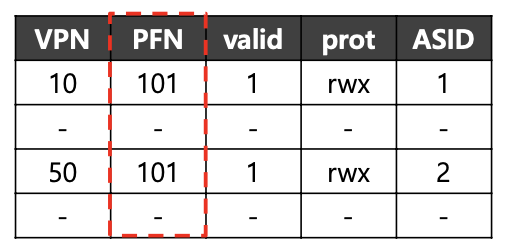

- TLB유지 위해 HW의 도움 받음 (TLB구조에 ASID 정보 추가), ASID는 identifier 역할로 process를 구분짓는다

: PFN이 같은 상황(코드 공유)

-> page 공유는 메모리 사용을 줄이기 때문에 메모리 공간 확보 가능

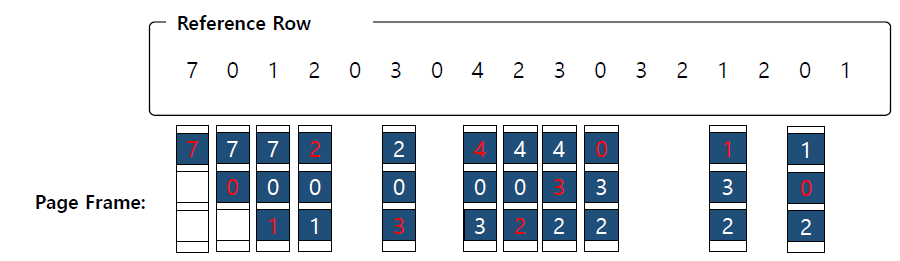

TLB Replacement Policy

: TLB가 꽉차있어서 버려야할때

- LRU : 가장 오랜 시간 사용되지 않은 process의 정보 제거

: Total TLB miss : 11

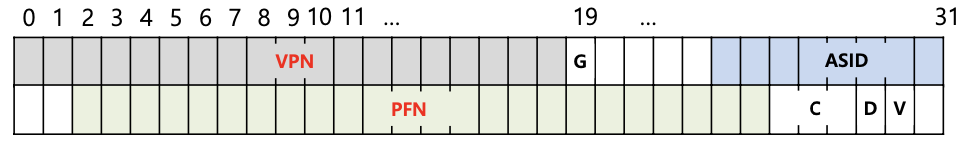

A Real TLB Entry

[MIPS R4000의 예시 - 32비트 주소공간에 4KB페이지 지원]

- 32비트 주소 공간

- 4KB페이지

: VPN 19비트, offset 12비트, 남은 1비트는 사용자인지 커널인지 판단 - PFN 24비트 할당

- PFN(물리 프레임 번호)로 24비트 할당

- G(전역 비트) 설정 되어 있으면 ASID무시, 예시에서는 8비트 길이의 ASID 있음 -> 이 부분 보고 주소 공간 구분

- Dirty bit는 페이지 갱신 시 세팅

- Valid bit는 변환 정보가 존재하는지 나타냄

- 마지막 64번째 비트는 사용하지 않음