MUX

이번 포스트에서는 MUX를 설계해보았다. NAND게이트와 NOT게이트를 이용하여 설계하였는데, 차후에 Swich를 이용하여 다시 재설계할 예정이다.

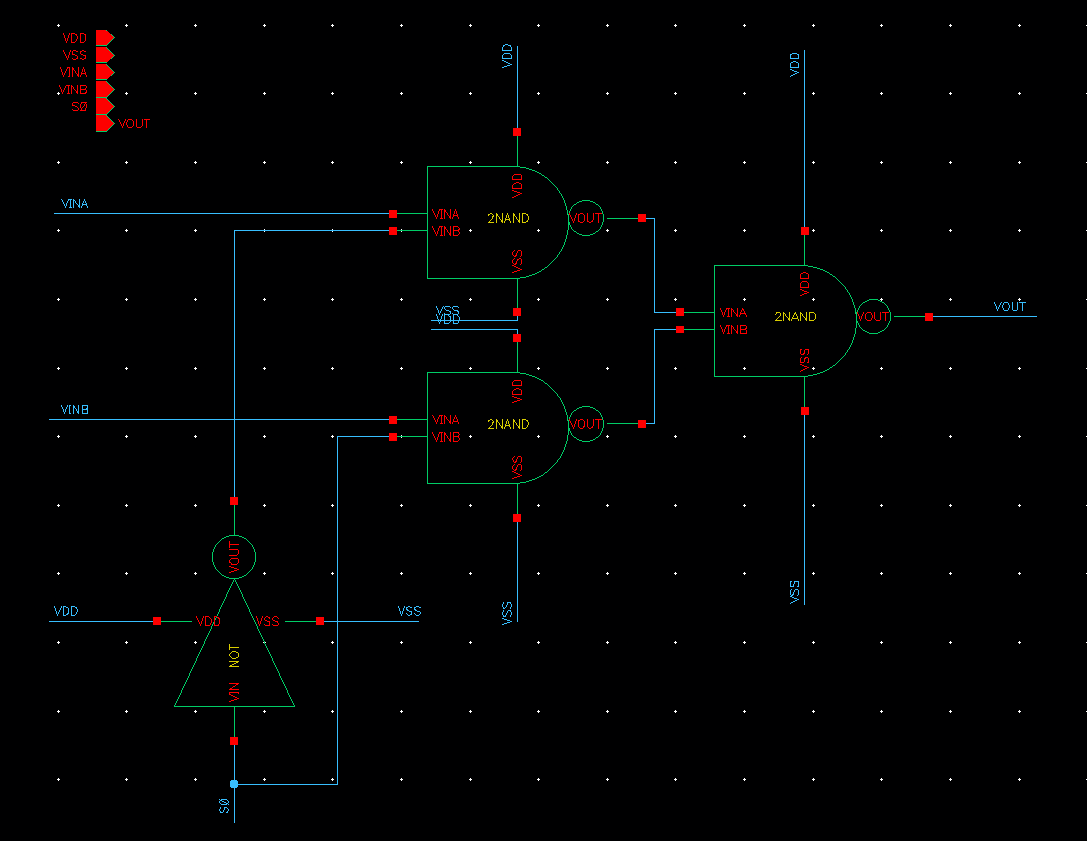

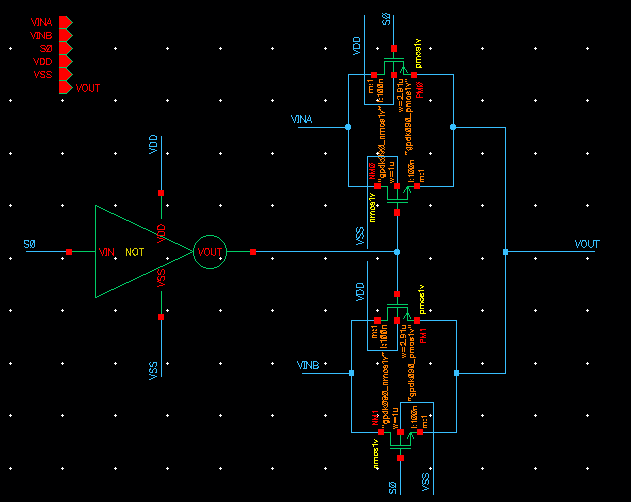

Schematic

Schematic을 먼저 그려보았다. VINA와 VINB를 주목하시라. 입력되는 2X1MUX의 앞쪽 숫자, 2입력을 의미한다. S0은 인코딩 신호이며, 입력 신호는 VINA와 VINB 각각 교류와 직류를 흘려준다. 합성된 신호는 A일 때 교류 파형을, B일때 직류 파형을 보여줄 것이다.

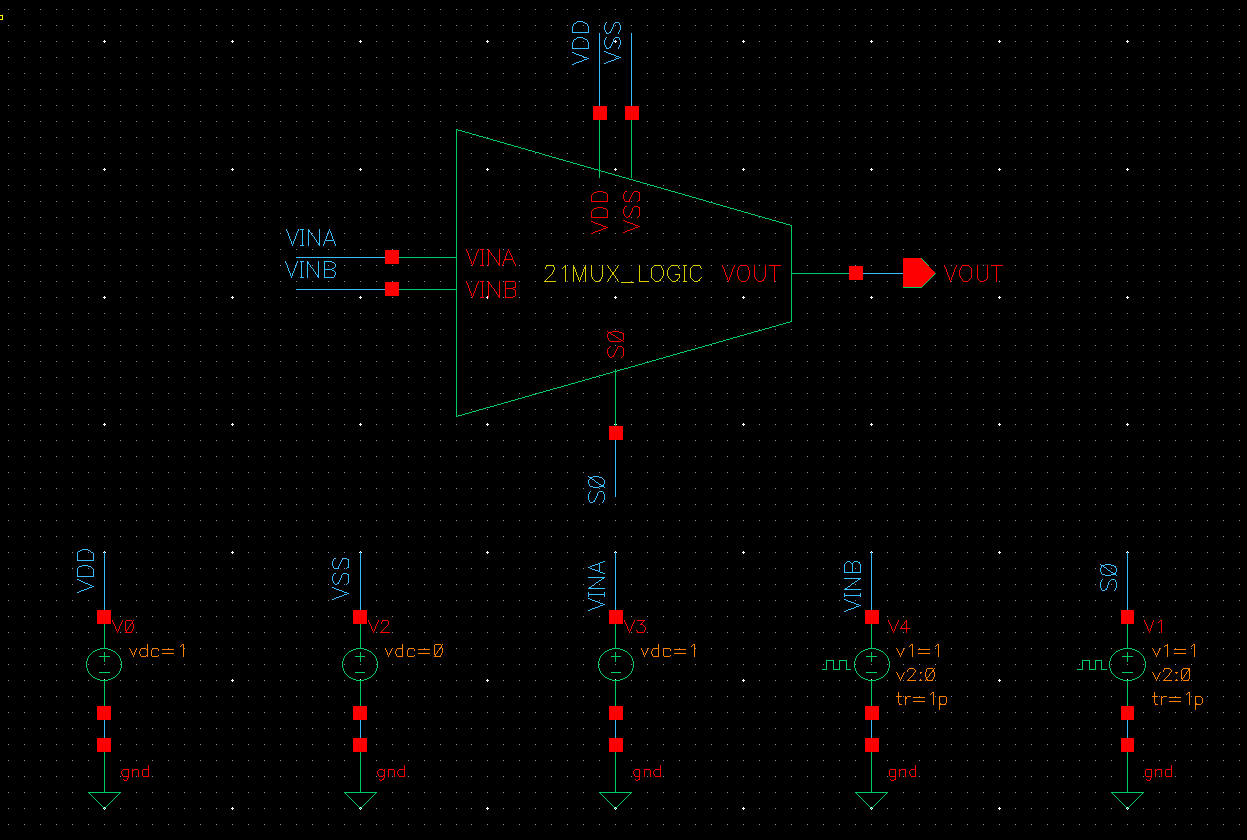

Symbol

심볼을 그려주었다. 이전과 다르게 VDD와 VSS를 모두 top으로 올려주었는데 그 이유는 bottom에 S0 시그널 신호를 추가해주었기 때문이다. VDD와 VSS는 default로 넣어주어야 하기 때문에 모두 top으로 몰아주었다.

TEST

VDD와 VSS는 당연히 1과 0[V]가 들어갔고, VINA와 VINB는 각각 교류와 직류를 넣어주었다. SO은 일정 주기(200ns)마다 0과 1V를 반복하면서 넣어주었다.

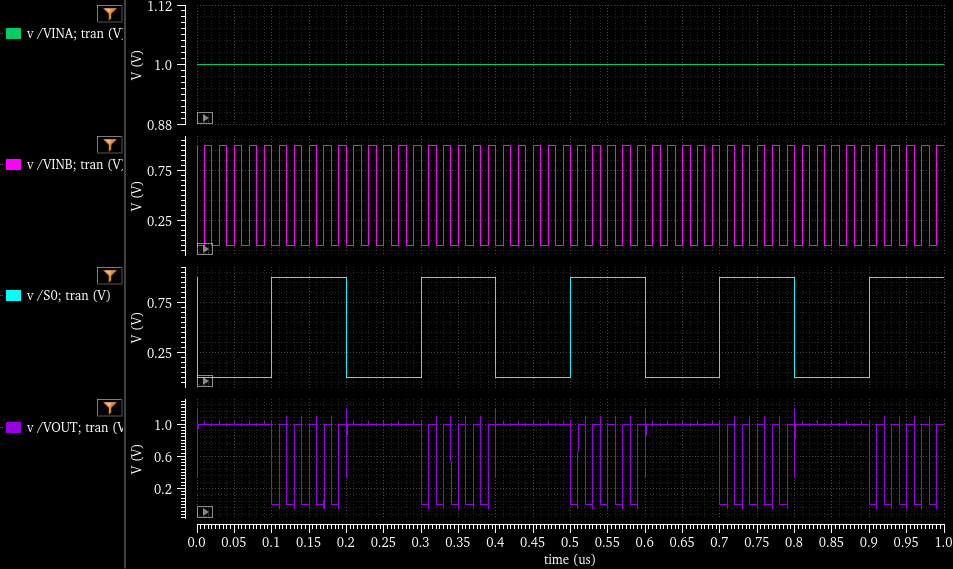

TEST_파형

파형을 분석해보면, SO에 따라서 출력되는 VOUT을 주목해야만 한다. SO이 0일 때 나타는 파형은 직류 파형이다. 즉, VINA가 출력됨을 의미하며 SO이 1일 때는 교류 파형이 출력된다. VINB이 이때는 출력됨을 알 수 있다.

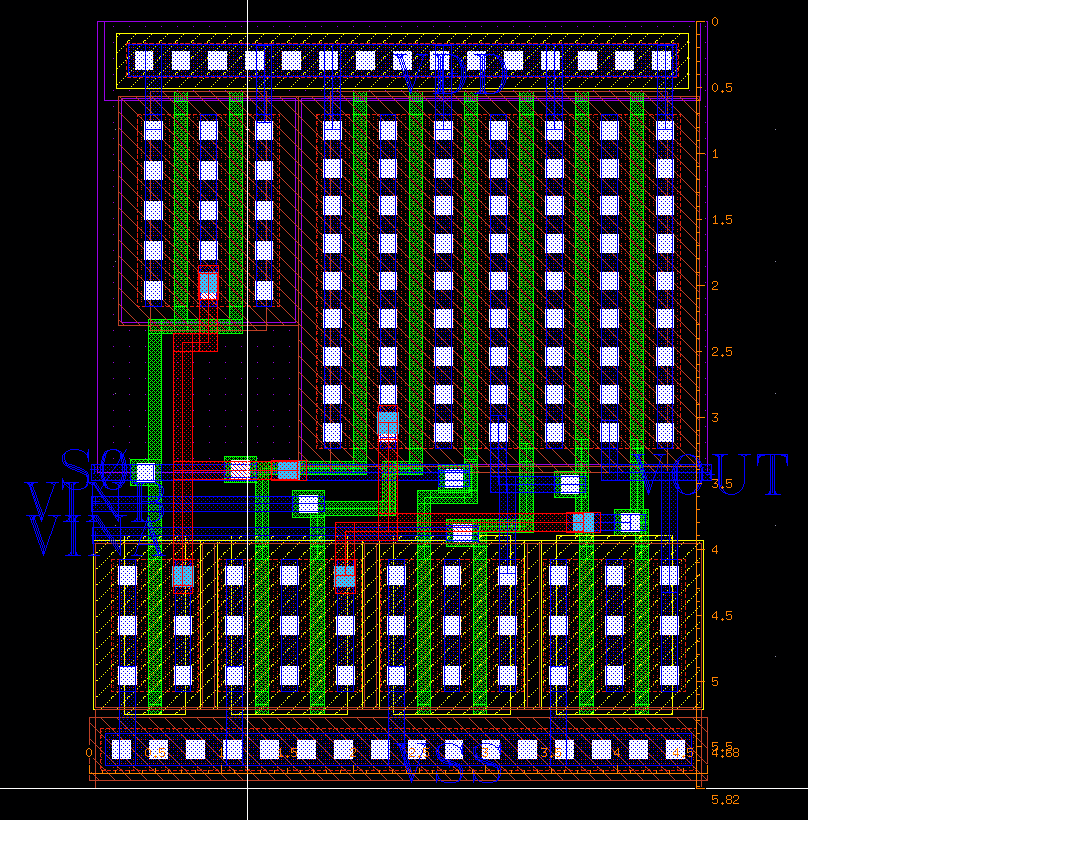

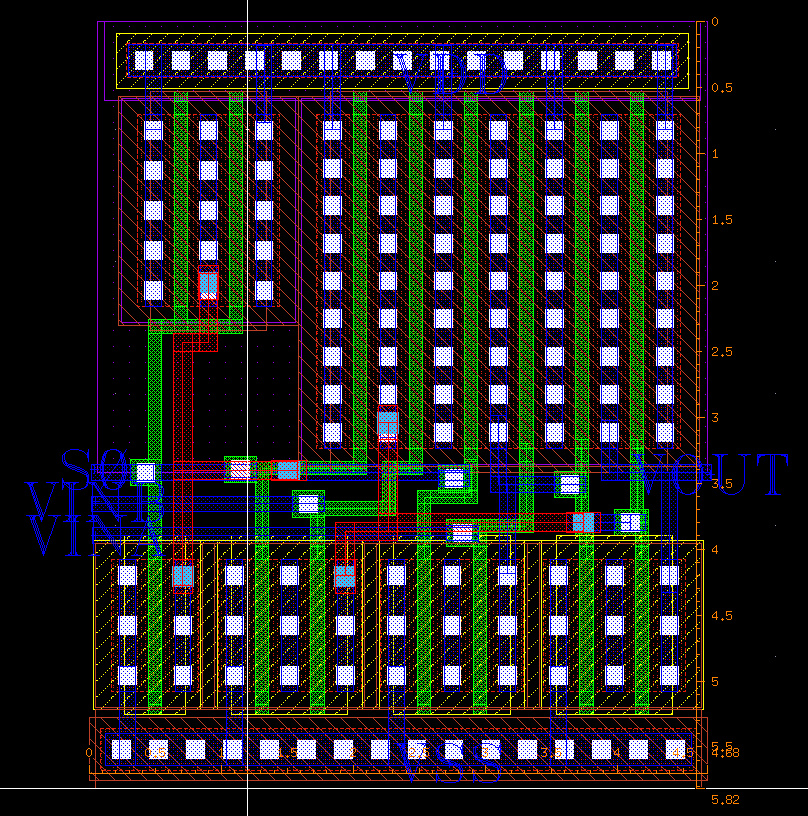

Layout

일단 완성해 본 layout이다. NOT게이트를 한번 접어주어서 finger가 2개가 되었다. 이 경우, 같은 회로이므로 poly를 둘 다 연결해주어야 함을 명심해야 한다. 상단 nMOS를 한번 더 주목해보자. 아래 pMOS와는 다르게 한 덩어리지 않는가? 이는 같은 선로를 사용하기에 합성 가능하기 때문에 덩어리로 합친 형태이다. 또한, 이 덩어리 nMOS의 왼쪽 poly부터 1번이라고 하면 1,2번은 AS0 NAND이고 3,4번은 B(S0b) NAND이다. 마지막 5,6번은 이 AS0, B(S0b) NAND이다. 중앙에 여럿 교차하는 전선로가 보이는가? 1234번에서 합성된 신호가 56번으로 전달되는 것을 관찰할 수 있다.(솔직히 글쓴이도 만들어놓고 잘 안보인다.)

Switch

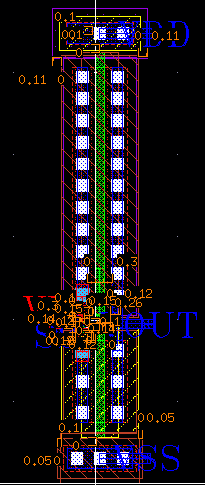

switch를 이용하여 MUX의 효과를 내면서도 크기를 크게 줄일 수 있다. MUX는 신호 S에 따라 입력신호를 통과시키는 기작을 가지는데, 이는 곧 스위치를 조작하여 신호를 취사선택하여 내보내는 것으로 치환할 수 있다. 다음 switch의 schametic과 layout을 보자.

비교하여 보면 switch의 layout 크기가 획기적으로 작은 것을 볼 수 있다. 이를 이용해 21MUX를 만들어보자.

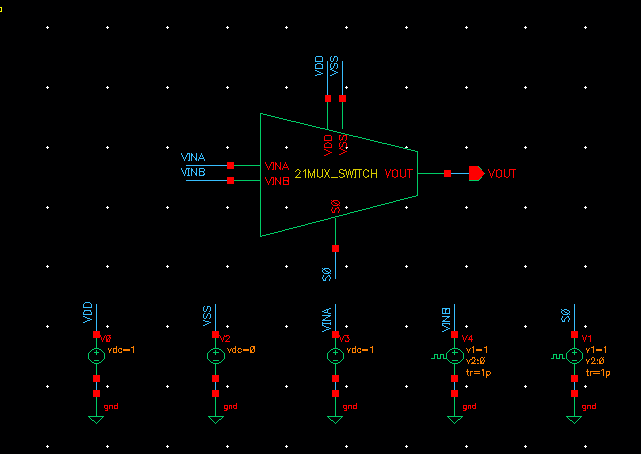

21MUX_SWITCH

1. schametic과 symbol을 만든다.

2. symbol을 이용하여 검증을 실시

3. layout을 만든다

총평

비교하여 보면, 일반 논리 게이트 NAND와 NOT을 이용한 것보다 더 작아진 21MUX_switch의 모습을 관찰할 수 있다. 또한 검증 시, 같은 결과를 도출하는 것을 확인할 수 있다.