zynq-7000

zynq-7000 보드를 이용하여 세탁기를 구현하는 프로젝트이다. xdc 핀 맵을 비롯하여, 기능들을 기획하고 모듈을 구성하여 완성시킬 예정이다.

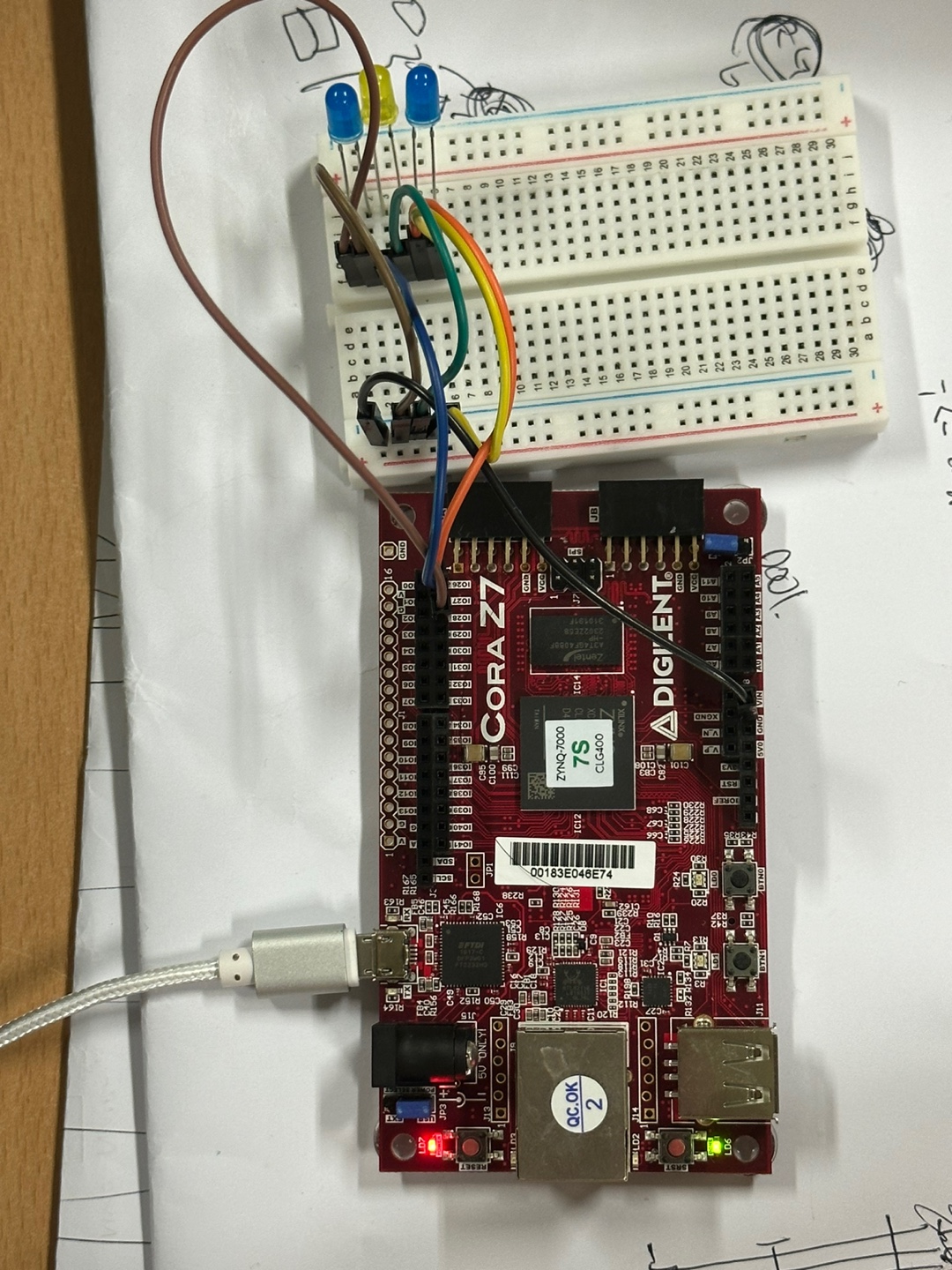

LED_TEST

기기의 전원과 동작상태를 사용자에게 알릴 수 있는 LED의 점멸/on/off 상태를 구현하기 위해 LED로 테스트를 먼저 시행한다.

cnt_1s.v

`timescale 1ns / 1ps

module cnt_1ms

(

input clk, rst, //125MHz = 8ns

output reg clk_s //1s

);

reg [39:0] clk_reg;

always @ (posedge clk or negedge rst)

begin

if (!rst)

begin

clk_s <= 1'b1;

clk_reg <= 40'b0;

end

else

begin

if (clk_reg == 40'd124999999)

begin

clk_s <= ~clk_s;

clk_reg <= 40'd0;

end

else

begin

clk_reg <= clk_reg + 1'b1;

end

end

end

endmoduleLED_TEST.v

`timescale 1ns / 1ps

module WM_LED_TEST

(

input clk, rst,

input led_en,

//input led_clk_cnt,

input clk_cnt_1secEnd,

output reg led_out

);

always @ (posedge clk or negedge rst)

begin

if (!rst)

begin

led_out <= 1'b0;

end

else if (led_en == 1'b0)

begin

led_out <= 1'b0;

end

else

begin

led_out <= clk_cnt_1secEnd;

end

end

endmoduletop.v

`timescale 1ns/1ps

module LED_top

(

input clk, rst,

output red_led_wash,

output red_led_rinse,

output red_led_dry,

output red_led_repeat,

output red_led_water_height,

output red_led_hot_cold,

output green_led_water_high,

output green_led_water_mid,

output green_led_water_low,

output green_led_hot_only,

output green_led_cold_only,

output green_led_hot_cold

);

wire reset = !rst;

cnt_1ms

inst_cnt_1ms

(

clk, reset, //125MHz = 8ns

clk_sec //1ms

);

WM_LED_TEST

wm_led_onoff_wash

(

clk, reset,

1'b1,

//clk_ms,

clk_sec,

red_led_wash

);

WM_LED_TEST

wm_led_onoff_rinse

(

clk, reset,

1'b1,

// clk_ms,

clk_sec,

red_led_rinse

);

WM_LED_TEST

wm_led_onoff_dry

(

clk, reset,

1'b1,

//clk_ms,

clk_sec,

red_led_dry

);

assign red_led_repeat =0;

assign red_led_water_height=0;

assign red_led_hot_cold =0;

assign green_led_water_high=0;

assign green_led_water_mid =0;

assign green_led_water_low =0;

assign green_led_hot_only =0;

assign green_led_cold_only =0;

assign green_led_hot_cold =0;

endmodule

led.xdc

# PL System Clock

set_property -dict {PACKAGE_PIN H16 IOSTANDARD LVCMOS33} [get_ports clk]

create_clock -period 8.000 -name sys_clk_pin -waveform {0.000 4.000} -add [get_ports clk]

# ResetN

set_property -dict {PACKAGE_PIN D20 IOSTANDARD LVCMOS33} [get_ports rst]

## ChipKit Inner Digital Header

set_property -dict {PACKAGE_PIN R16 IOSTANDARD LVCMOS33} [get_ports red_led_wash]

set_property -dict {PACKAGE_PIN U12 IOSTANDARD LVCMOS33} [get_ports red_led_rinse]

set_property -dict {PACKAGE_PIN U13 IOSTANDARD LVCMOS33} [get_ports red_led_dry]

set_property -dict {PACKAGE_PIN V15 IOSTANDARD LVCMOS33} [get_ports red_led_repeat]

set_property -dict {PACKAGE_PIN T16 IOSTANDARD LVCMOS33} [get_ports red_led_water_height]

set_property -dict {PACKAGE_PIN U17 IOSTANDARD LVCMOS33} [get_ports red_led_hot_cold]

set_property -dict {PACKAGE_PIN T17 IOSTANDARD LVCMOS33} [get_ports green_led_water_high]

set_property -dict {PACKAGE_PIN R18 IOSTANDARD LVCMOS33} [get_ports green_led_water_mid]

set_property -dict {PACKAGE_PIN P18 IOSTANDARD LVCMOS33} [get_ports green_led_water_low]

set_property -dict {PACKAGE_PIN N17 IOSTANDARD LVCMOS33} [get_ports green_led_hot_only]

set_property -dict {PACKAGE_PIN M17 IOSTANDARD LVCMOS33} [get_ports green_led_cold_only]

set_property -dict {PACKAGE_PIN L17 IOSTANDARD LVCMOS33} [get_ports green_led_hot_cold]

결과

1초마다 핀 상태를 바꿈으로써 LED를 점멸시켰다. 코드를 작성한 후 합성한 뒤에 bitstream file을 생성하여 FPGA 보드에 삽입하면, 작동을 확인할 수 있다.