시스템 베릴로그

소개

verilog를 사용하여 모듈을 만들고, 그것이 제대로 작동하는지 시험하기 위한 언어이다. cadence사에서 verilog를 개수하여 문법을 계승시키고 발전시켜 만들어졌다.

물론 이 SV(systen verilog)를 이용하여 디자인을 수행할 수는 있지만, testbench를 수행할 수 있도록 목표를 두고 학습할 예정이다.

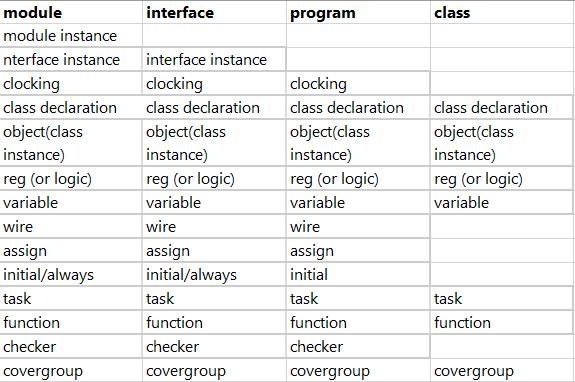

SV에서 사용하는 구조

문법 규칙 및 작명법

SV도 verilog와 같이 작명법은 숫자가 아닌 문자로 시작하며, o, d, b, h와 같은 size 단위를 사용하여 숫자를 표현한다.

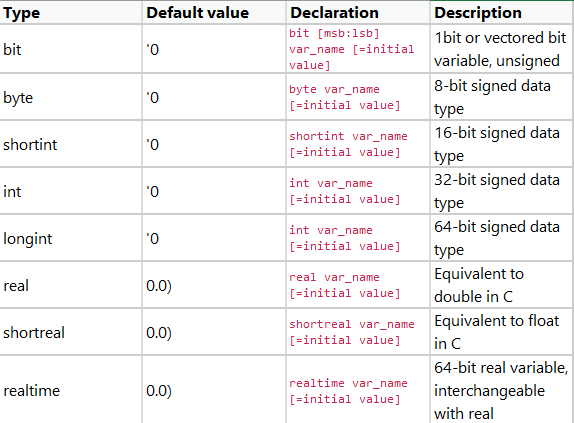

2 state type data

SV에서 추가된 type으로써, 일반 verilog에서느 0, 1, x, z와 같이 4가지 상태로 데이터를 표현하므로 고려할 사항이 많아 속도가 느리다.

그러나 SV에서는 0, 1의 데이터형은 그대로 나타내며, (0100 -> 0100) x, z는 모두 0으로 나타내어 데이터형을 단순화시킨다.(zx01 - > 0001 )

다음은 2state type의 자료형들이다.

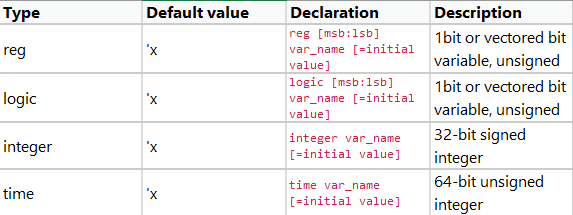

4 state type data

verilog에서 그대로 계승되어 SV에 사용되는 데이터 타입이다. 바뀐 것은 logic 타입인데, 이것은 reg와 같은 방식으로 사용되며 unsign 타입이다.

string type

verilog에서는 문자열을 나타낼 수도, 나타낼 필요도 없었지만 testbench에 특화되어 있는 SV는 문자열을 나타낼 수 있다.

string num1 = $sformatf("%d", i); 등의 구문을 통해 string에 저장하거나,

$display("%s", num2);를 통해 결과값을 낼 수도 있다.

define type

커스텀 자료형 선언

우리가 C++를 사용하며 구조체를 만들어서 타입을 선언하는 것과 같이, 새로운 타입을 선언할 수 있다.

unsigned longint data1;

bit [7:0] data2;와 같이 선언하여야 하는 자료형을 다음과 같이 미리 선언해놓는다면,

typedef unsigned longint tul;

typedef bit [7:0] bi;다음에 같은 자료형을 사용해야 할 때 다음과 같이 선언할 수 있다.

tul data1;

bi data2;구조체 선언 예

typedef str {bit [7:0] opcode;

bit [23:0] addr;}

my_str;

str structure;

structure.addr = 24'hFFFFFF;클래스 선언 예

class rect:

cnt = 0

def rect_h(wid, hei, a):

a.wid = width

a.hei = height

rect_h.a = rect_cnt

def rect_s(a):

area = a.width * a.height

return areaenumeration

code를 더 단순하고 읽기 편하게 만들어주는 기능이다. 변수에 유효한 명칭을 붙여 코드를 작성 가능하다.

enum {red, yellow, green} light1, light2; // anonymous int type

enum {red=1, yellow=4, green} light1, light2; // green will be 5

enum bit [1:0] {IDLE, XX='x, S1=2'b01, S2=2'b10} state, next; // Syntax error: XX=2'bx <ERROR>, bit is 2-State

enum integer {IDLE, XX='x, S1='b01, S2='b10} state, next; // // Correct: integer is 4-State

enum integer {IDLE, XX='x, S1, S2} state, next; // Syntax error: IDLE=0, XX='x, S1=??, S2=??

enum bit [3:0] {bronze=4'h3, silver, gold=4'h5} medal3; // Correct declaration

enum bit [3:0] {bronze=5'h13, silver, gold=3'h5} medal4; // Error in the bronze and gold member declarations

https://3dwarehouse.sketchup.com/by/chinabamboo

https://blog.ulifestyle.com.hk/chinabamboo

https://routinehub.co/user/chinabamboo

https://hub.docker.com/u/chinabamboo

https://pantip.com/profile/9010914#topics

https://tamilculture.com/user/china-bamboo

https://www.passes.com/chinabamboo

https://aiplanet.com/profile/chinabamboo

https://bookmeter.com/users/1612789

https://linkfly.to/70816G7up4g

https://www.papercall.io/speakers/chinabamboo

https://sketchersunited.org/users/273241

https://biomolecula.ru/authors/82748

https://linkr.bio/chinabamboo/store

https://smartprogress.do/user/752262/

https://swaay.com/u/bothbest/

https://2024.hackerspace.govhack.org/profiles/china_bamboo

http://www.ssnote.net/users/chinabamboo

https://www.notebook.ai/@chinabamboo

https://cofacts.tw/user/chinabamboo

https://bio.site/bambooflooring

https://www.myminifactory.com/users/chinabamboo

https://www.upcarta.com/profile/chinabamboo

https://chinabamboo.stck.me/

https://coub.com/chinabamboo

https://portfolium.com/chinabamboo

https://motion-gallery.net/users/817902