참고글 : https://devraphy.tistory.com/297

⭐ Flip-Flop (플립플롭)

- 1bit를 기억할 수 있는 순서회로

- 플립 플롭이 여러개 모여있는 장치가 레지스터

📌 조합회로 vs 순서회로

조합회로

- 게이트로만 이루어진 논리회로

- 외부의 입력에 의해서만 출력이 발생하는 논리회로

순서회로

- Flip-Flop과 게이트를 연결한 논리회로

- 내부의 상태값에 따라 출력이 발생하는 논리회로

⭐ Flip-Flop의 종류

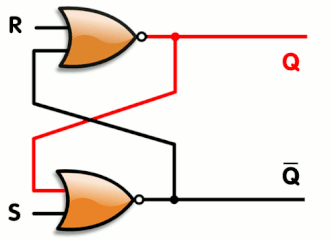

📌 RS(SR) Flip-Flop

- 플립플롭의 가장 기본 구조

- S = Set / R = Reset / Q = output

- R과 S 값에 따라 Q의 상태에 변화한다.

- 변화한 Q의 값에 따라 전기가 켜지고(1) 꺼지는(0) 결과가 정해진다.

- 회로 구조에 따라 S값이 한 번이라도 1이 되면 output은 1이된다.

- 그 이후에 R값이 1이 되면 output은 0이된다.

(이미지출처 : https://en.m.wikipedia.org/wiki/Flip-flop_(electronics)#JK_flip-flop)

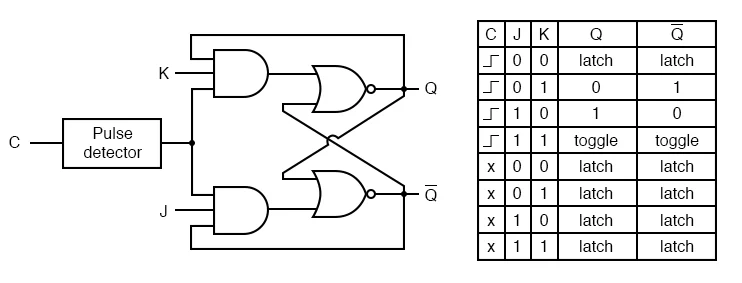

📌 JK Flip-Flop

- RS 플립플롭에서 S=1, R=1인 경우 불능 상태가 되는 것을 해결한 논리회로

- J는 S(set)에, K는 R(reset)에 대응하는 입력

- J와 K의 입력이 동시에 1이 입력되면 플립플롭의 출력은 이전 출력의 보수 상태로 변화하게 된다.

(이미지출처 : https://www.allaboutcircuits.com/textbook/digital/chpt-10/j-k-flip-flop/)

이미지에서 pulse detector의 경우 클럭펄스라고 보면 되는데, 클럭 신호가 있을 때마다 1값이 되고, 그 때만 입력 값 1이 의미가 있게 됨

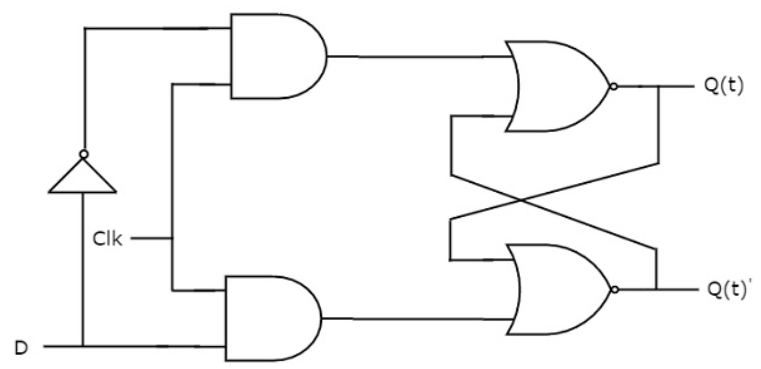

📌 D Flip-Flop

- 입력 단자 R과 S에 동시에 1이 입력되는 것을 회로적으로 차단한다.

(not 게이트로 한쪽이 1이면 다른 한 쪽은 무조건 0이 되도록 설계) - 입력신호 D가 클럭펄스에 의해서 변화 없이 그대로 출력에 전달되는 특성을 가지고 있다.

- 데이터(Data)를 전달하는 것과 지연(Delay)을 의미하는 D 플립플롭이라고 한다.

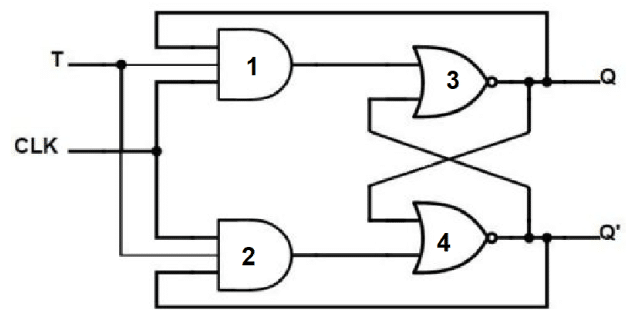

📌 T Flip-Flop

- JK 플립플롭의 J와 K 입력을 묶어서 하나의 입력신호 T로 동작시키는 플립플롭이다.

- 입력이 0이 되면 이전상태(Q)의 값이 그대로 출력된다.

- 입력이 1이 되면 이전상태(Q)의 보수 값이 출력된다.