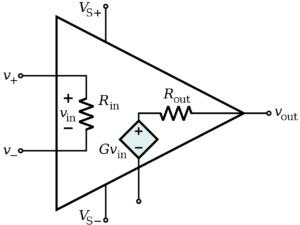

OpAmp(Operational Amplifier)는 매우높은 입력저항, 그리고 0에 가까운 출력저항을 통한 높은 Gain이 특징인 소자입니다.

단독으로는 +입력 단자와 -입력단자간의 전압 차이를 증폭시키는 역할을 합니다. 하지만 이상적인 OpAmp의 특성은 무한대의 입력저항과 0의 값을 가지는 출력저항이기 때문에 이러한 특성을 가지고 여러가지 회로에 응용할 수 있습니다.

이 때 는 위 OpAmp의 Gain()입니다.

이상적인 OpAmp

OpAmp의 내부 등가회로 입니다. 실제로 이렇게 구성이 되어 있는 것이 아닌 등가회로로 알아보기 쉽게 그려놓은 것이기 때문에, 회로가 연결이 안되어있다고 어렵게 생각할 필요가 없습니다.

그림을 잘 살펴본다면, 에 따라 걸리는 전압 에 의하여 출력전압 이 결정된다고 쉽게 이해하실 수 있을 겁니다.

하지만 이상적인 모델의 OpAmp에서는 다음이 성립한다고 가정합니다.

따라서 저항이 무한대이므로 와 에는 전류가 흐르지 않게 되기 때문에, Ideal OpAmp Model에서의 이론적인 문제를 풀 때는 입력단에 흐르는 전류를 0으로 놓고 풀게 되는 것입니다.

위 등가회로 그림에서 는 Ideal OpAmp Model 의 Gain으로서 open loop gain 이라고 부르고 값을 가집니다.

즉 OpAmp를 단독으로 사용하게 된다면 이론상 무한대의 출력전압을 뿜어낼 수 있다는 건데, 실제로는 이렇게 동작하지 않습니다.

이는 나중에 offset에 대한 설명을 통해 알아보겠습니다.

Negative Feedback

의 전압을 으로 부궤환(negative feedback)시킨다면 어떻게 될까요?

위에서 이라고 했죠??

그래서 이 됩니다.

에 의한 이 에 영향을 미치게 되므로 은 더이상 무한대가 아니게 됩니다. 하지만 는 여전히 성립하므로

입력단과 출력단의 전압이 같아지게 됩니다. 이러한 특성들은 우리가 Ideal OpAmp Model 에 대한 회로문제를 풀때 주로 사용하게 됩니다.

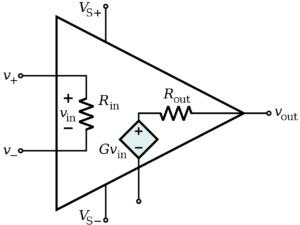

현실적인 OpAmp

위에서 이상적인 OpAmp의 특성에 대하여 알아보았습니다. 이제 실제 연산증폭기가 어떻게 동작하고, 어떤 회로에 응용되는지 알아보도록 하겠습니다.

실제로는 은 정도의 매우 큰 값을 가지고, 은 ~정도의 매우 작은 저항값을 가지게 됩니다. G의 경우 수만~수십만정도의 큰 값을 가진다고 보시면 되겠습니다.

따라서 일 때 이므로 이 0 이 나올 것이라는 것을 그림을 통해 짐작해 볼 수 있습니다. 과연 진짜로 성립하는지 알아보도록 하겠습니다.

offset 전압

실제로는 두 입력단의 미세한 차이 때문에 가 성립하여도 이 성립하지 않습니다. 이 현상을 반영하여 위에서 설명했던 수식을 조금 수정해야 합니다.

즉 가 과 같아졌을때 비로소 출력전압이 0이 됩니다.

을 offset전압이라 부르며 OpAmp소자마다 공정과정에서 고유한 값을 가지게 됩니다.

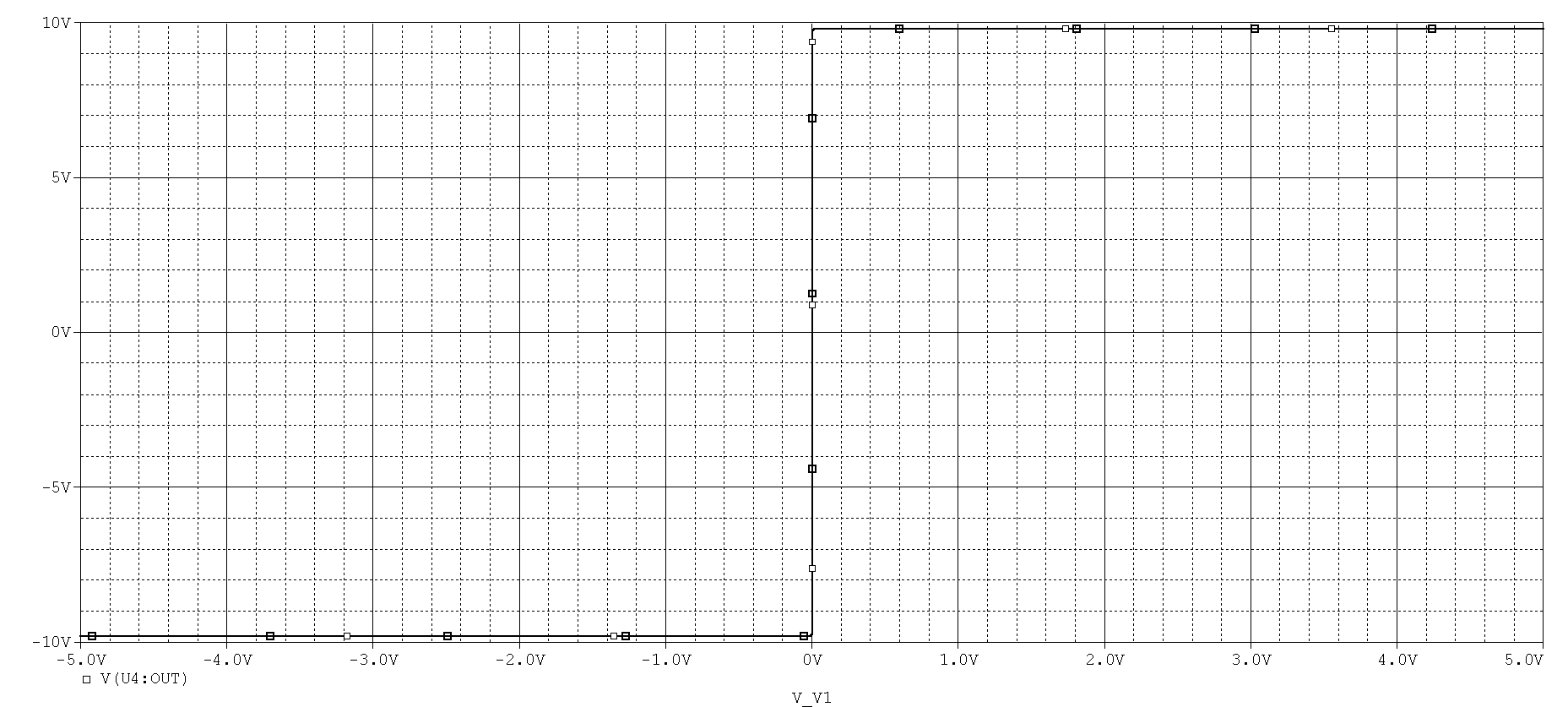

앞서 OpAmp가 단독으로 사용되었을 때, 이론적으로 무한대의 출력전압이득을 가진다고 하였습니다. 실제로도 Gain은 수만~수십만 정도이기 때문에 아주 작은 만 주어져도 굉장히 큰 출력전압이 나올것입니다.

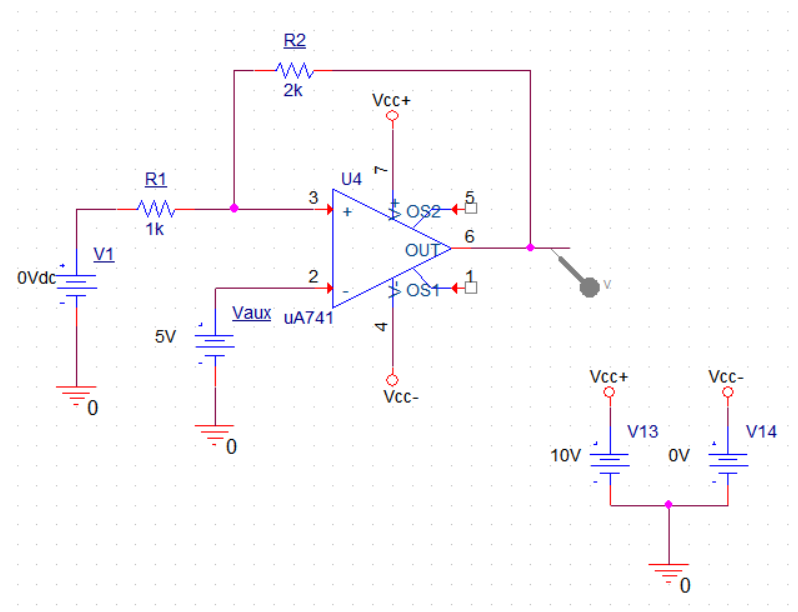

한번 실험을 해보겠습니다.

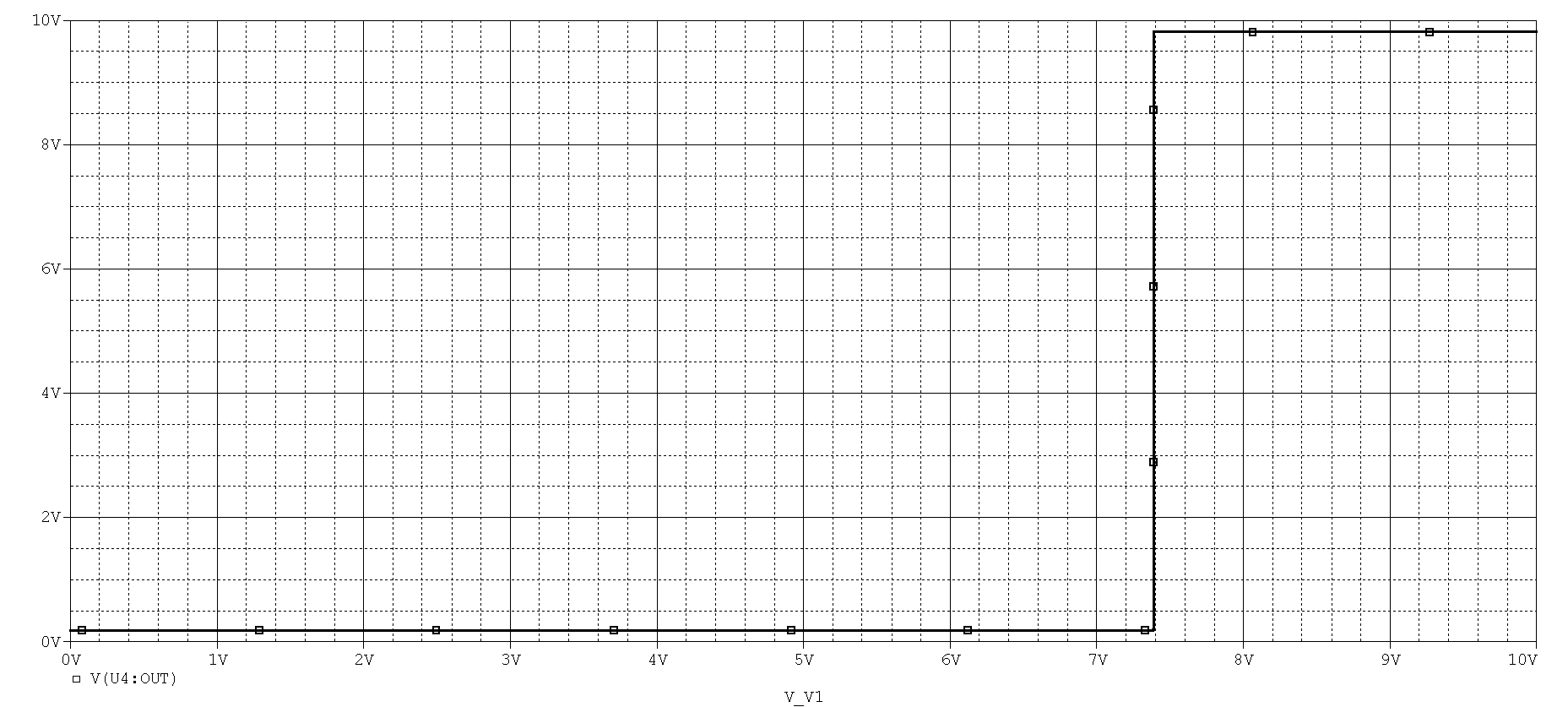

값을 -5V~5V까지 매우 큰 폭으로 변화시키는 동안 0 부근에서 의 아주 미세한 값에 반응하여 출력전압이 증폭되지만, 일정수치이상 높이 올라가지 않은 것을 확인할 수 있습니다.

저희가 연산증폭기에 들어가는 전원을 -10V ~ 10V로 주었기 때문에 이 이상 출력전압이 높게 나오지 않게 되는 것입니다.

offset 전압은 매우 작기 때문에 입력단에 Voltage Devider 회로를 구현하여 미세한 단위의 전압에 대한 DC Sweep 을 진행하면 offset전압을 찾을 수 있을 것입니다.

Schmitt Trigger 회로 (Positive Feedback)

슈미트 트리거 회로에 대해 이해하기 위해서는 먼저 이력현상(Hysterisis)에 대해 알아야 합니다.

- 이력현상(Hysterisis) 이란?

물질이 거쳐온 과거가 현재 상태에 영향을 주는 현상을 의미합니다.

보일러를 예로 하나 들어봅시다. 우리가 실내 온도를 30도정도로 일정하게 맞추고 싶다고 해봅시다. 그래서 30도보다 온도가 높아지면 보일러를 끄고, 30도보다 온도가 낮아지면 보일러가 켜지게 설계를 했다고 합시다.

그러면 30도 부근에서 보일러가 켜졌다 꺼졌다를 반복하면서 불필요한 자원을 너무 많이 사용하게 되겠죠?

그래서 우리는 29도 밑으로 내려가면 보일러가 켜지고, 31도 이상 올라가면 보일러가 꺼지게 설계를 했습니다. 이제는 적정한 온도가 유지되며 자원 소모량도 안정적이게 되었습니다.

이것이 Hysterisis 특성입니다. 단순히 보일러 on/off toggle switch 동작일 뿐이지만, 보일러가 작동중이라면 31도 이상인 지점에서 toggle 동작이 이루어지고 보일러가 작동중이 아니라면 29도 이하인 지점에서 toggle 동작이 이루어집니다.

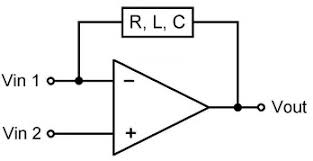

다음은 슈미트 트리거 회로입니다.

-입력단자에 를 걸어주고 +입력단자에 Positive Feedback을 걸어주었습니다. 그 사이에 저항 두개가 들어가 과 출력전압의 차이에 따라 +입력단자에 걸리는 전압이 결정됩니다.

V1이 0V에서 10V로 증가할 때의 출력전압

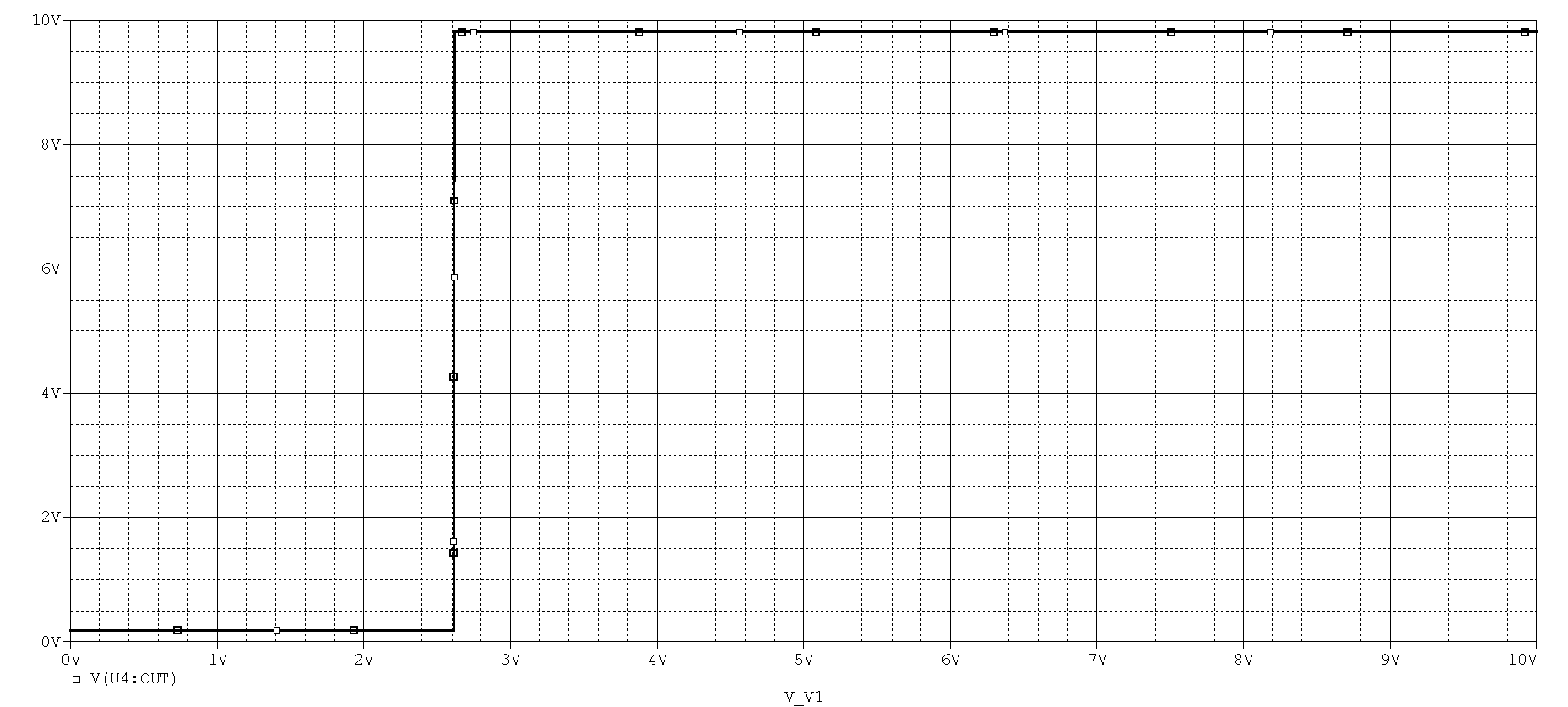

V1이 10V에서 0V로 감소할 때의 출력전압

일정 지점에서 Vcc값에 따라 trigger되는 그래프 모양은 일반적인 OpAmp 작동방식과 똑같습니다.

하지만 trigger되기 전의 출력전압이 0V인지, 10V인지에 따라 Trigger되는 지점이 다릅니다. Hysterisis 특성을 가지는 OpAmp인 것입니다.

전압이 증폭될 때 에 걸리는 값을 , 에 걸리는 값을 이라고 두고 계산을 해봅시다.

위에서 OpAmp 입력단자에 들어가는 전압차 일 때 출력전압이 trigger 된다고 하였습니다.

즉, OpAmp의 +입력단자에 걸리는 전압이 인 5V일 때를 구하면 trigger 작용이 일어나는 지점을 알 수 있습니다.

- V1이 0V에서 10V로 증가할 때

- V1이 10V에서 0V로 감소할 때

임을 생각한다면 위의 수식을 통해 trigger되는 위치가 상황마다 다르다는것을 알 수 있습니다.

Unity-Gain Voltage Follower

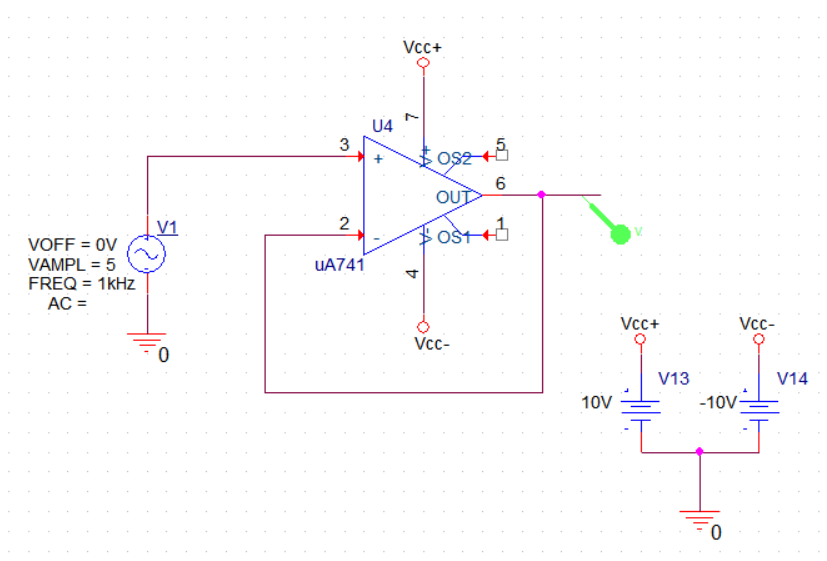

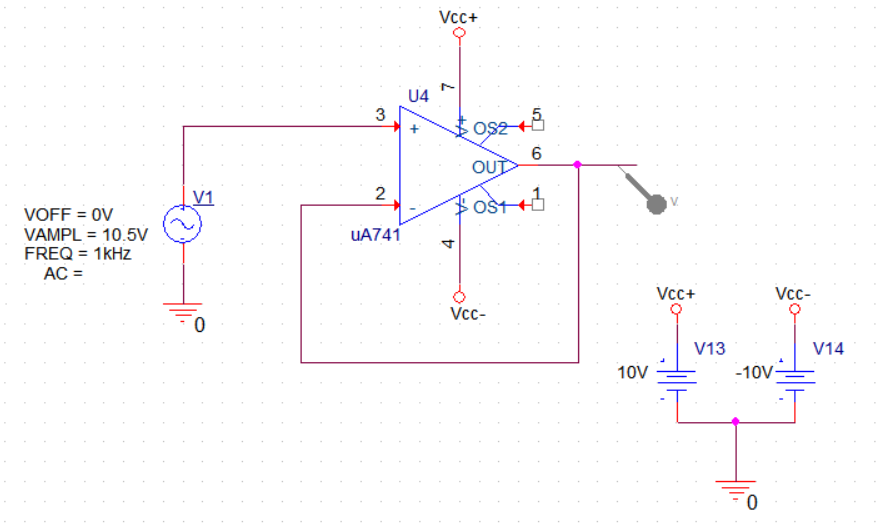

다음은 전압 팔로워 회로입니다.

앞서 이상적인 OpAmp에 대해 설명하면서 Negative Feedback에 대해 설명하였습니다. +입력단자와 -입력단자의 전위차가 항상 0이기 때문에 증폭이 일어나지 않습니다. 그래서 이 회로에서의 OpAmp가 가지는 Gain은 1이 됩니다.

1의 Gain을 가지며 따라서 입력전압이 출력전압에 그대로 출력된다고 하여

Unity-Gain Voltage Follower라고 부릅니다.

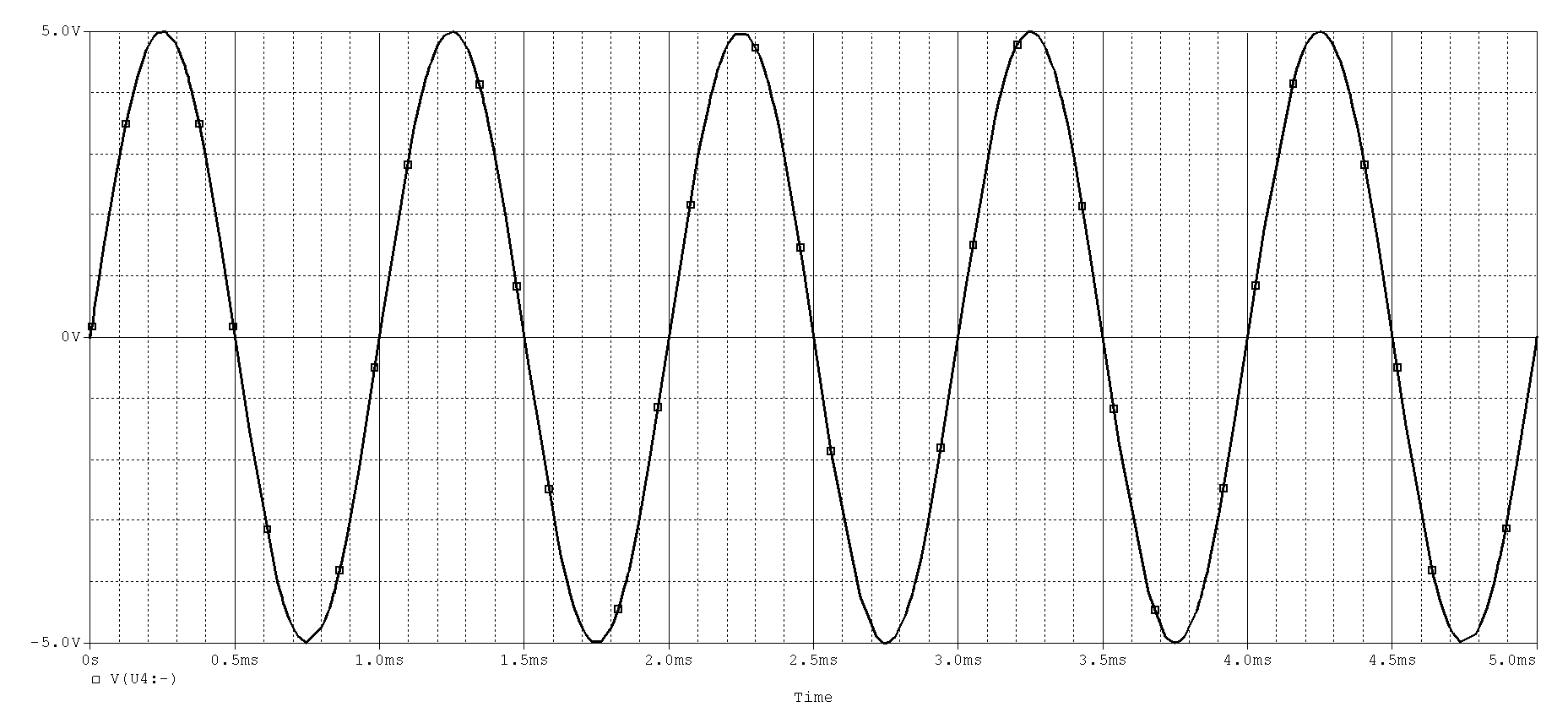

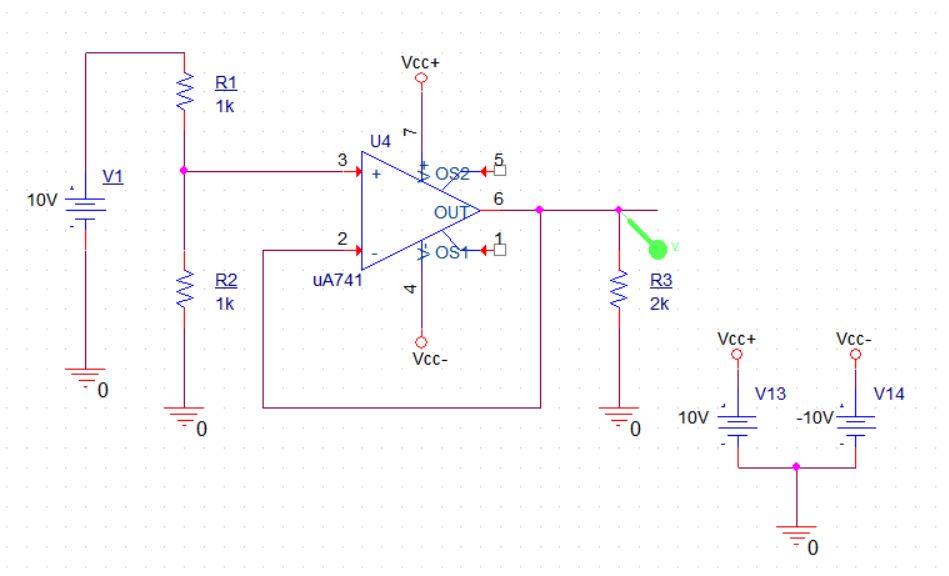

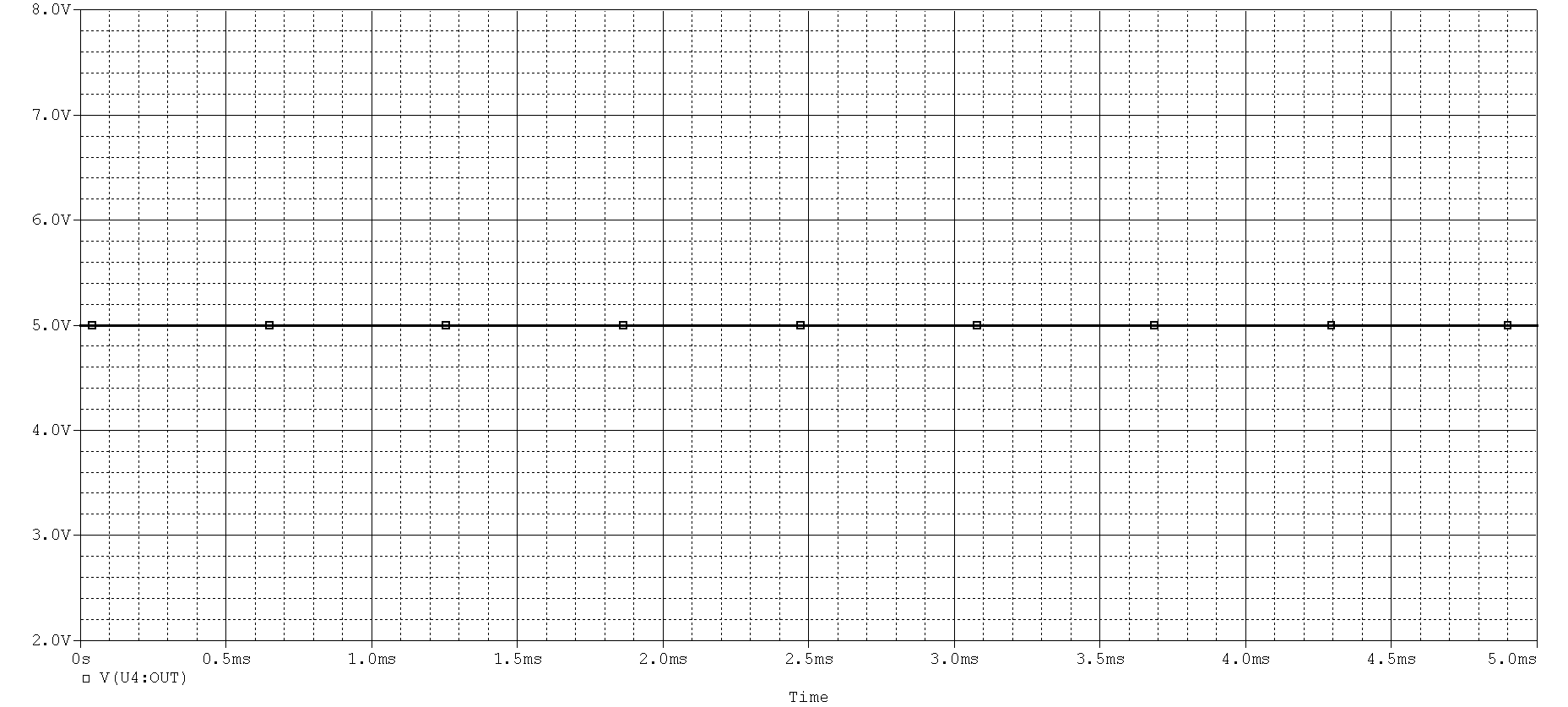

다음은 출력전압의 그래프입니다.

입력전압과 일치한다는 것을 알 수 있습니다.

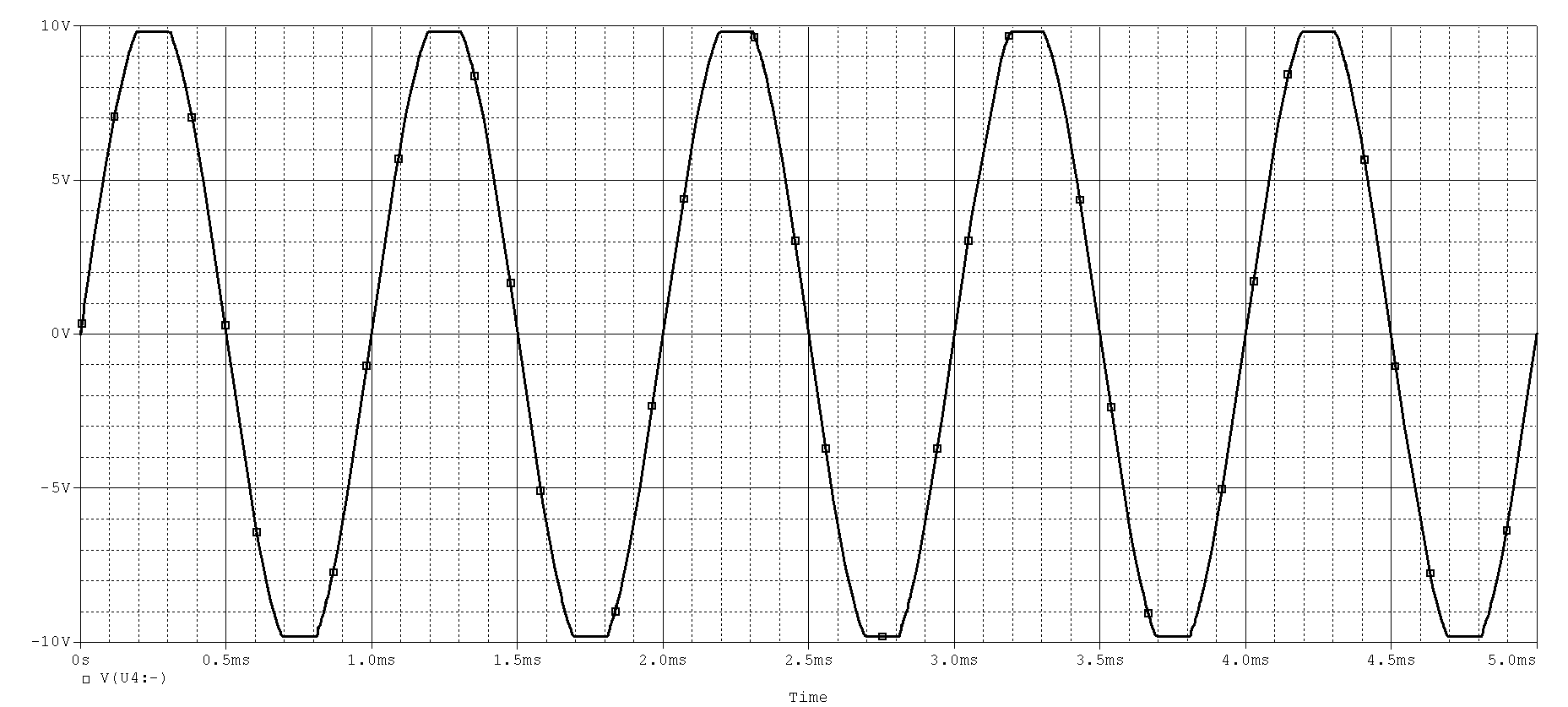

입력전압의 크기를 Vcc값보다 키우면 아래 출력그래프처럼 Vcc값 부근에서 출력전압이 잘리게 됩니다. 이를 포화(saturation) 현상이라고 부릅니다.

OpAmp에서 출력전압은 Vcc값 이상으로 나올 수 없습니다.

그렇다면 아무런 전압이득도 없는 이 회로를 도대체 어디에 사용할까요? 입력전압을 순수하게 출력전압으로 꽂아준다는 것 자체에서 의미가 있습니다.

바로 Loading Effect를 제거하는데 사용합니다.

- Looading Effect(부하효과)란?

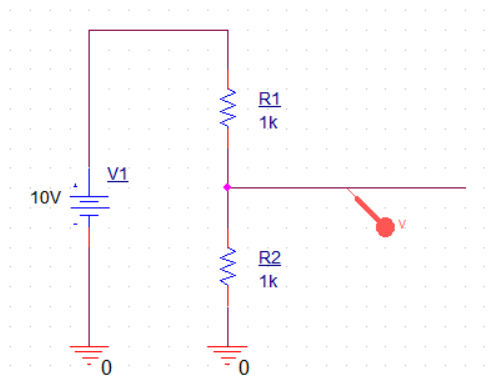

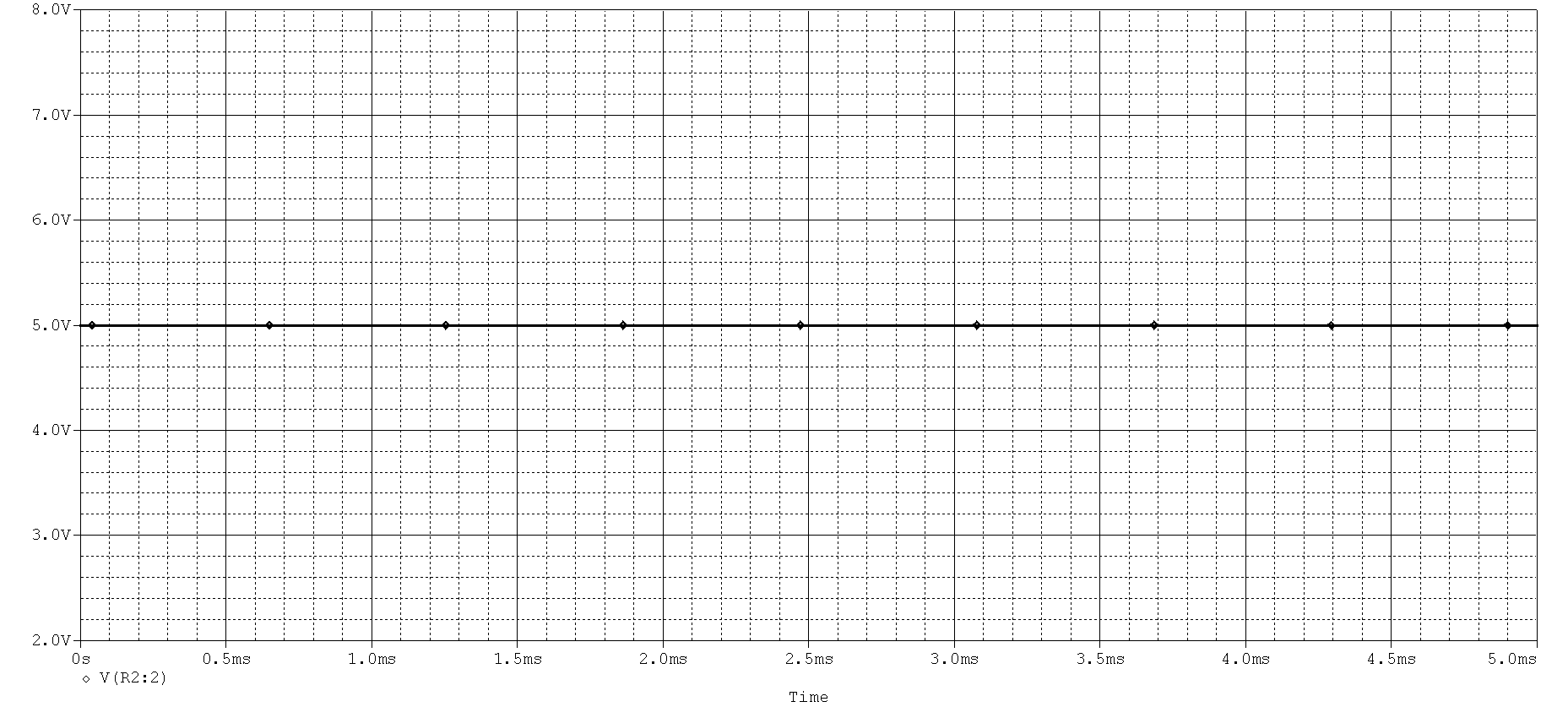

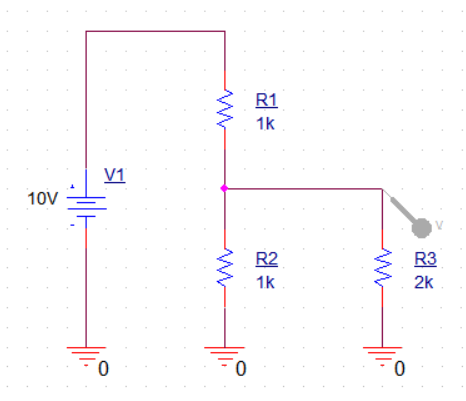

상황을 하나 가정해봅시다. 고정적으로 5V를 공급해주어야 하는 어떤 장치가 있습니다. 하지만 우리가 5V를 직접 생산할 수는 없기 때문에 주어진 10V를 가지고 간단한 Voltage Devider 회로를 구현하여 다음과같이 5V를 공급하는 회로를 만들었습니다.

자 이제 입력전원을 만들었고, 장치를 연결해주기만 하면 끝입니다. 우리가 사용할 장치는 의 부하를 가지고 있다고 가정합니다.

따라서 다음과 같이 Voltage Devider회로에 을 가지는 R3를 연결해 등가회로를 만들었습니다.

그런데 우리의 예상과는 달리 연결된 장치에 4V밖에 걸리지 않습니다.

이유는 단순합니다. R3가 R2에 병렬로 연결되면서 10V에 걸리는 총 부하가 달라져버렸기 때문입니다.

이처럼 부하(R3)가 회로(R1, R2, V1)에 영향을 미치는 현상을 Loading Effect라고 부릅니다.

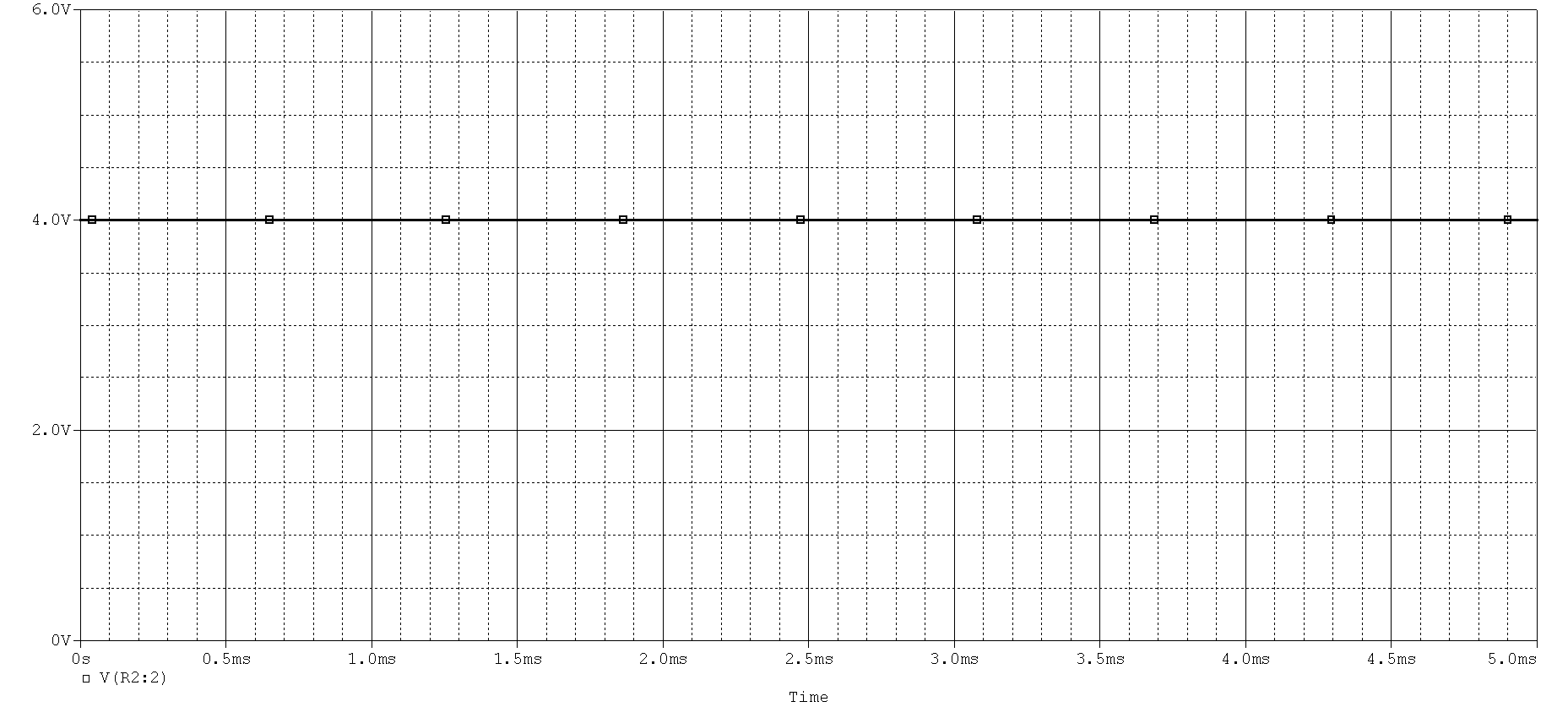

따라서 부하를 회로에 물리적으로 연결시키면서 Loading Effect를 제거할 때 Voltage Follower를 사용합니다.

아까와 같은 조건이지만 중간에 Voltage Follower를 거쳐서 부하를 달아주었습니다.

자 이제는 5V가 그대로 부하에 걸리게 되었습니다!

해석해보자면 OpAmp의 +입력단자와 -입력단자 사이의 저항 라고 하였습니다. 물론 실제로는 매우큰 값의 저항이지만 편의상 이상적인 OpAmp모델로 해석하겠습니다. 따라서 +입력단자와 -입력단자 사이는 Open상태로 전류가 흐르지 않는다고 볼 수 있습니다.

그래서 출력단에 어떤 부하가 걸리던, +입력단자와 -입력단자는 open상태에 있어 왼쪽의 Voltage Devider회로에 영향을 미치지 않으므로 순수하게 5V가 OpAmp의 입력단에 들어가게 됩니다. 따라서 Unity-Gain Voltage Follower 특성에 의해 그대로 출력단에도 5V가 출력되어 그곳에 부하를 걸어줌으로써 온전한 5V를 사용할 수 있게 되는 것입니다.

내용정리

OpAmp자체는 단독으로 사용될 때 두 입력단자 와 사이의 전위차를 증폭시켜주는 소자이며, 와 의 값에서 saturation 되는 특징이 있습니다. 따라서 와 중 어느 전압이 더 큰지 판별할 수 있는 비교기로써의 역할을 하게됩니다. (가 더 크면 값이, 가 더 크면 값이 출력되겠죠?)

또한 출력단을 +입력단자나 -입력단자로 궤환시켜주는 Feedback 방식에 따라 Schmitt Trigger나 Voltage Follower와 같은 각각 다른 특징을 가진 회로로 구성할 수 있습니다.