https://xilinx.github.io/Vitis-AI/3.5/html/index.html

Xilinx 사의 vitis AI 문서에 대한 내용을 정리해 보았다.

1. Vitis AI

AMD Vitis AI is an integrated development enviroment that can be leveraged to accelerate AI inference on AMD platforms.

It consists of three primary components:

[] 1.DPU

[] 2. Model Development tools

[] 3. libraries and APIs.

Where to Download?

[] AMD open download: pre built target images

[] Vitis AI docker containers: model development tools

[] Vitis AI github repository: libraries, set up scripts, examples and reference design.

2.DPU

And here, I became curious about DPU. What is DPU? Is it a FPGA or something? So I searched on internet about it.

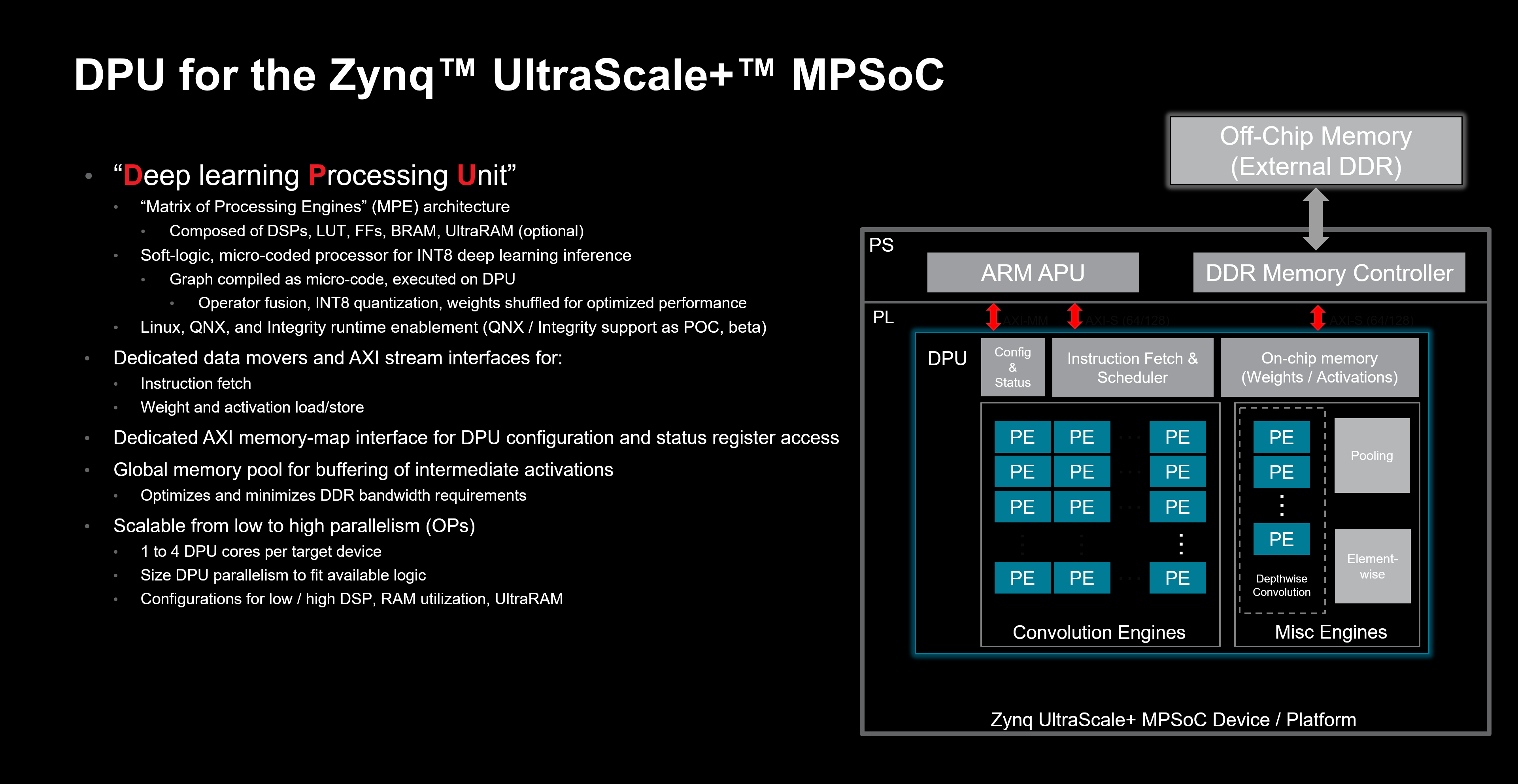

Dpu compries of DSP, BlockRAM, UltraRAM, LUTs, Flip Flops.

And it can be developed as a set of microcoded functions that are deployed on the AMD AI Engine. or "AI Engine" architecture.

Figure above is from Xilinx.

DPU is a "Matrix of Processing Engines" architecture.

You can see a lot PEs in the picture above.

soft-logic, micro-coded processor for INT8 deep learning inference.

So, what is soft-logic processor?

I googled it and wikipedia said like this

A soft microprocessor (also called softcore microprocessor or a soft processor) is a microprocessor core that can be wholly implemented using logic synthesis. It can be implemented via different semiconductor devices containing programmable logic (e.g., ASIC, FPGA, CPLD), including both high-end and commodity variations.

It seems like processors that can be impolemeted by using logic synthesis.

It didn't feel obvious to me. So I googled about the difference between hard processor and soft processor.

https://www.edaboard.com/threads/whats-the-difference-among-soft-processor-and-hard-processor.44943/

hard processors are the one which are already fabricated onto the chip.whereas softcore processors are in the HDL form called as IP's

I found this reply. And What is IP???

IP means Intellectual property.

It's like a predetermined block which is implemented into devices.

As examples of "IP Cores", there are UART,CPU,Ethernet controller, PCI interface, and so on.

And microcode means machine code, which serves as an intermediary layer situated between the CPU and the ISA.

AXI is for Advanced eXtensible Interface.

The difference between AXI bus and AHB is the channel.

Read Address Channel

Read Data Channel

Write Address Channel

Write Data Channel

Write Response Channel

In case of AHB, channels above are consists of bus, and it can not operated independently.

AXI can run those independently due to the channel.

So I think DPU can be either FPGA or ASIC.

DPU implements an efficient tensor-level instruction set designed to support and accelerate various popular CNNs like VGG,ResNet, GoogLeNet, YOLO, SSD, and MobileNet, among others.

The DPU supports on AMD Zynq™ UltraScale+™ MPSoCs, the Kria™ KV260, Versal™ and Alveo cards.

3.Model Development

-

Vitis AI Model Zoo

It uncludes oprimized deep learning models covering different applications including ADAS/AD, video surveillance, robotics and data center. -

Vitis AI Model Inspector

This is used to perform initial sanity checks to confrim the operators and wequence of operators in the graph is compatible with Vitis AI. -

Vitis ai Optimizer

Used for pruning.

Pruning is removing some relatively unnecessary parameters to optimize the model with minimal accuracy degradation.

4.Vitis AI Quantizer

Quantization is a method improving performance by reducing bits of the parameters. When Vitis AI Quantizer converts FP32 weights and activations to fixed-point integers like INT8, the memory usage becomes 1/4.

5.Vitis AI Compiler

Vitis AI Compiler maps the AI quantized model to a instruction set and dataflow model.

4. Model Deployment

1.Vitis AI Runtime(VART)

Following paragraph is from Xilinx official document.

The Vitis AI Runtime (VART) is a set of low-level API functions that support the integration of the DPU into software applications. VART is built on top of the Xilinx Runtime (XRT) amd provides a unified high-level runtime for both Data Center and Embedded targets. Key features of the Vitis AI Runtime API include:

Runtime is the environment program operated on the OS or in the OS itself.

But in this paragraph above, it says "built on top of the Xilinx Runtime".

2.Vitis AI library

Following paragraph is from Xilinx official document.

The Vitis AI Library is a set of high-level libraries and APIs built on top of the Vitis AI Runtime (VART). The higher-level APIs included in the Vitis AI Library give developers a head-start on model deployment. While it is possible for developers to directly leverage the Vitis AI Runtime APIs to deploy a model on AMD platforms, it is often more beneficial to start with a ready-made example that incorporates the various elements of a typical application, including:

Acutually I'm not quite sure what the Vitis AI Library is exactly

3.Vitis AI Profiler

Following paragraph is from Xilinx official document.

The Vitis AI Profiler profiles and visualizes AI applications to find bottlenecks and allocates computing resources among different devices. It is easy to use and requires no code changes. It can trace function calls and run time, and also collect hardware information, including CPU, DPU, and memory utilization.