TLB(변환 후방 버퍼) 는 가상 주소를 물리 주소로 변환하는 데 사용되는 페이지 테이블의 일부를 캐싱하는 고속 메모리입니다.

위치: 보통 MMU(Memory Management Unit)에 내장

역할: 자주 참조되는 가상 페이지 번호 ↔ 물리 프레임 번호 매핑 정보를 저장

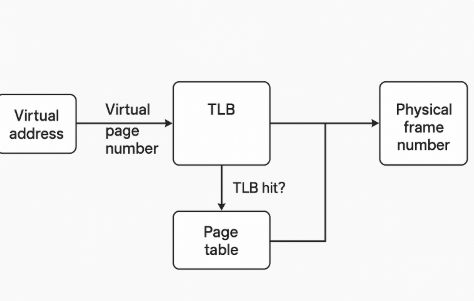

✅ 기본 흐름도

CPU가 가상 주소(Virtual Address) 생성

가상 페이지 번호를 추출

→ 가상 주소 = [가상 페이지 번호 | 페이지 오프셋]

TLB 조회

🔍 TLB에서 해당 가상 페이지 번호의 매핑 정보를 찾음

▶ TLB Hit

물리 프레임 번호를 즉시 얻음

최종 물리 주소 = 프레임 번호 + 오프셋

❌ TLB Miss

페이지 테이블(Page Table)에서 매핑 정보를 가져옴

가져온 정보를 TLB에 갱신

이후 물리 주소 계산

[CPU]

│

▼

[가상 주소 생성: (VPN, Offset)]

│

▼

[TLB 조회]

├── Hit → 물리 프레임 바로 사용

│

└── Miss

│

▼

[페이지 테이블에서 매핑 조회]

│

▼

[TLB 업데이트 + 물리 주소 계산]

✅ 성능 향상 포인트

페이지 테이블 접근은 메모리 접근 1회 이상 소모

TLB Hit 시에는 CPU → 메모리 접근 없이 곧바로 주소 변환

📈 → 메모리 접근 성능 극대화

✅ TLB 교체 정책 (TLB가 가득 찼을 때)

LRU : 가장 오랫동안 사용되지 않은 항목 제거

FIFO : 가장 먼저 들어온 항목 제거

Random : 임의의 항목 제거