Addition & Subtraciton

Overflow

결과값이 범위를 넘어가면, overflow가 발생한다

- 부호가 다른 피연산자를 더하면, no overflow.

- 두 + 피연산자를 더했는데 result sign이 1이면 overflow

- 두 - 피연산자를 더했는데 result sign이 0이면 overflow

- 부호가 같은 피연산자를 빼면, no overflow

- 피연산자에서 - 피연산자를 뺐는데 result sign이 1이면 overflow

- 피연산자에서 + 피연산자를 뺐는데 result sign이 0이면 overflow

Dealing with Overflow

- addu(add unsigned), addiu(add immediate unsigned), subu(subtract unsigned) 명령어들은 오버플로우가 발생해도 예외를 발생시키지 않는다.

- add(add), addi(add immediate), subtract(sub) 명령어들은 오버플로우가 발생하면 예외(exception)을 발생시킨다.

- 예외(exception)은 본질적으로 계획되지 않은 프로시저 호출이다.

- overflow가 발생한 명령어의 주소는 레지스터에 저장되고,

컴퓨터가 적절한 처리를 하기 위해 해당 루틴으로 jump한다. - 예외가 걸린 주소를 저장해서 해당 처리란 한 다음에 프로그램 실행을 계속할 수 있게 한다.

- EPC(exception program counter)

: 예외가 걸린 명령어의 주소를 기억하는 데 이용된다.

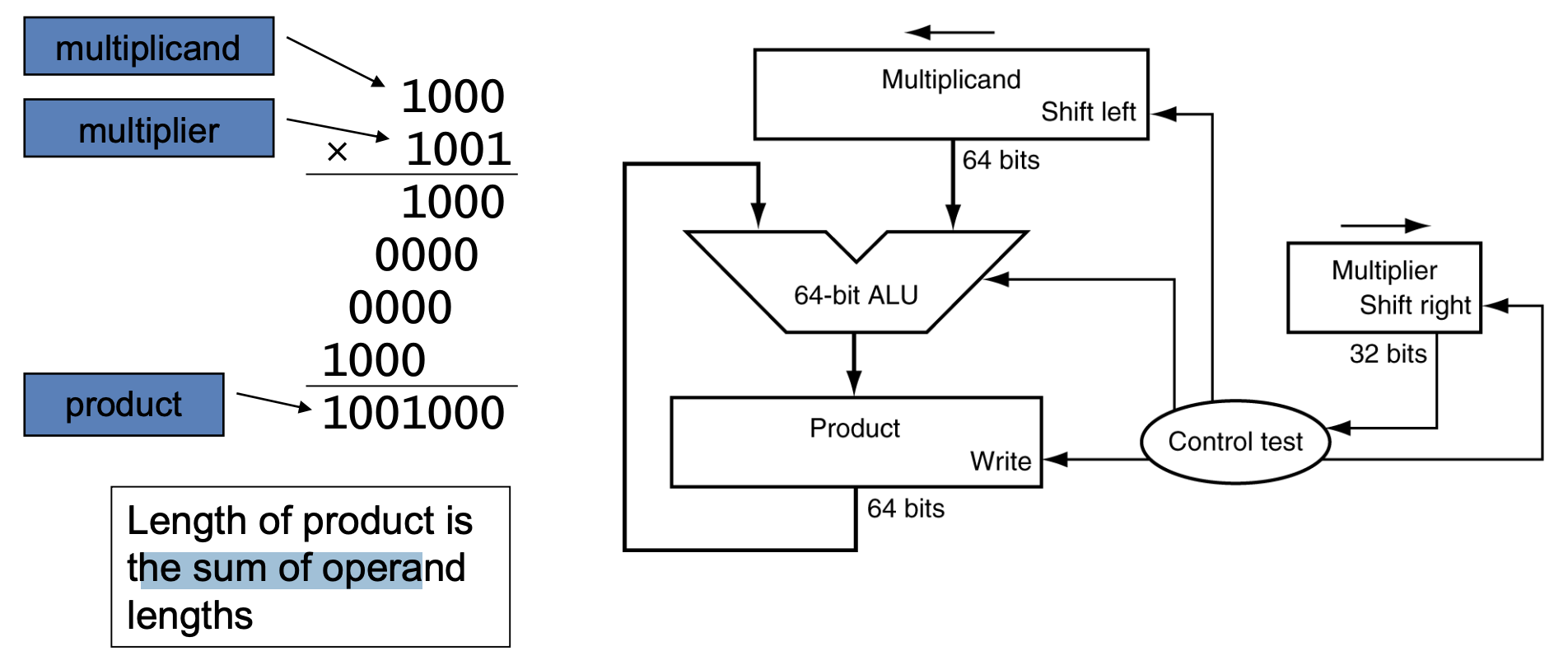

Multiplication

Basic

- 차근차근 해보자

레지스터 그림

-

우선, multiplicand, product는 64 bit register이고,

multiplier register는 32 bit register이다. -

multiplicand register

처음에는 오른쪽 32bit에 multiplicand가 위치해있다.

매 단계마다 왼쪽으로 shift되고,

32번 이동 후에는 왼쪽 32bit에 multiplicand가 위치하게 된다. -

multiplier register

매 단계마다 오른쪽으로 shift된다.

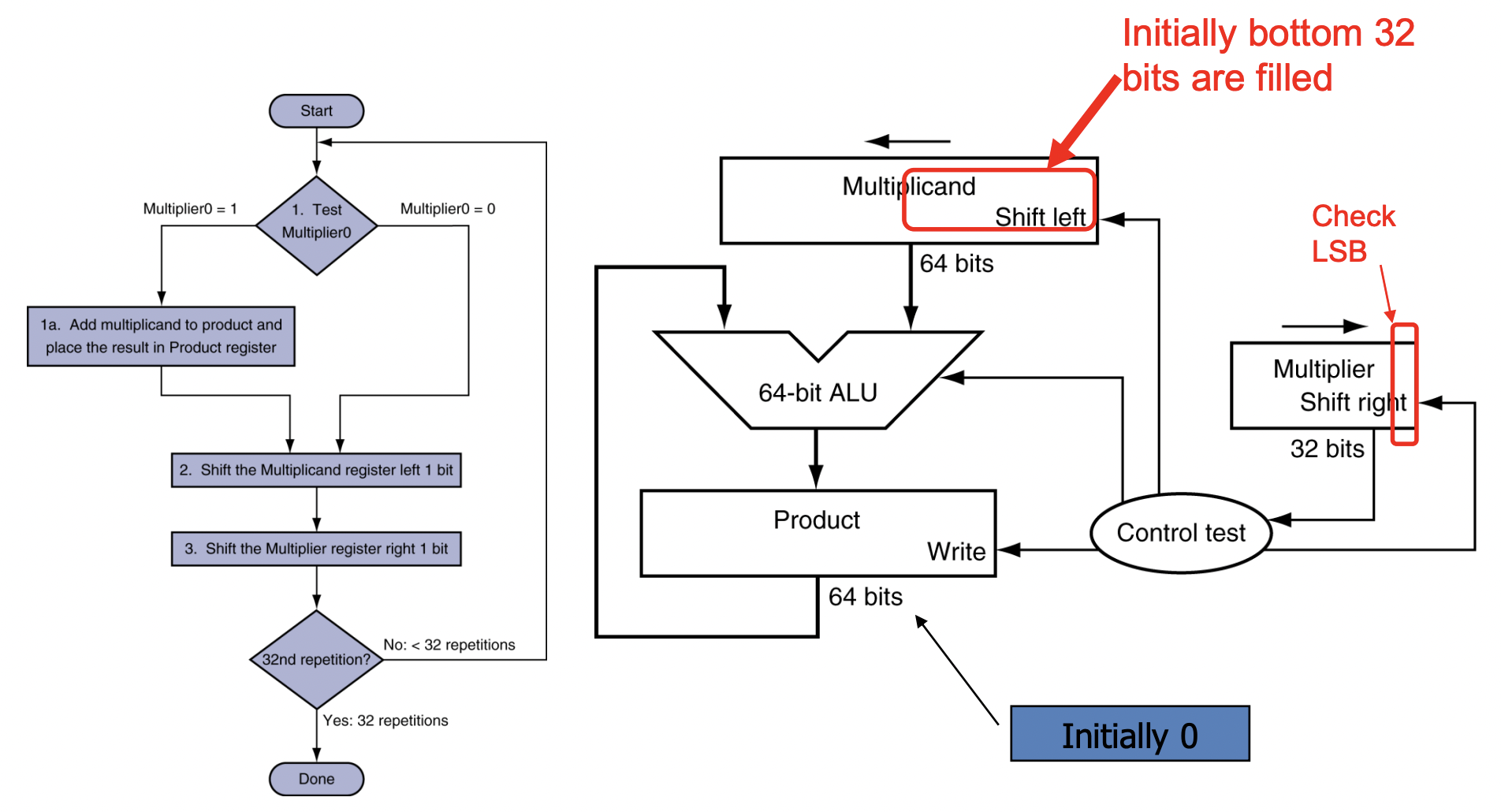

단계 다이어그램

-

Test multiplier()

: multiplicand를 product에 더할지 말지 결정한다

: (LSB가) 1이면 더해야 하고, 0이면 더할 필요가 없다 -

Shift the multiplicand registr left 1 bit

-

Shift the multiplier register right 1 bit

: multiplier의 다음 비트를 검사하기 위해 이동시킨다.

각 단계에 한 clock cycle이 필요하다면,

숫자 두 개 곱하는데 거의 100개의 clock cycle이 필요하게 된다.

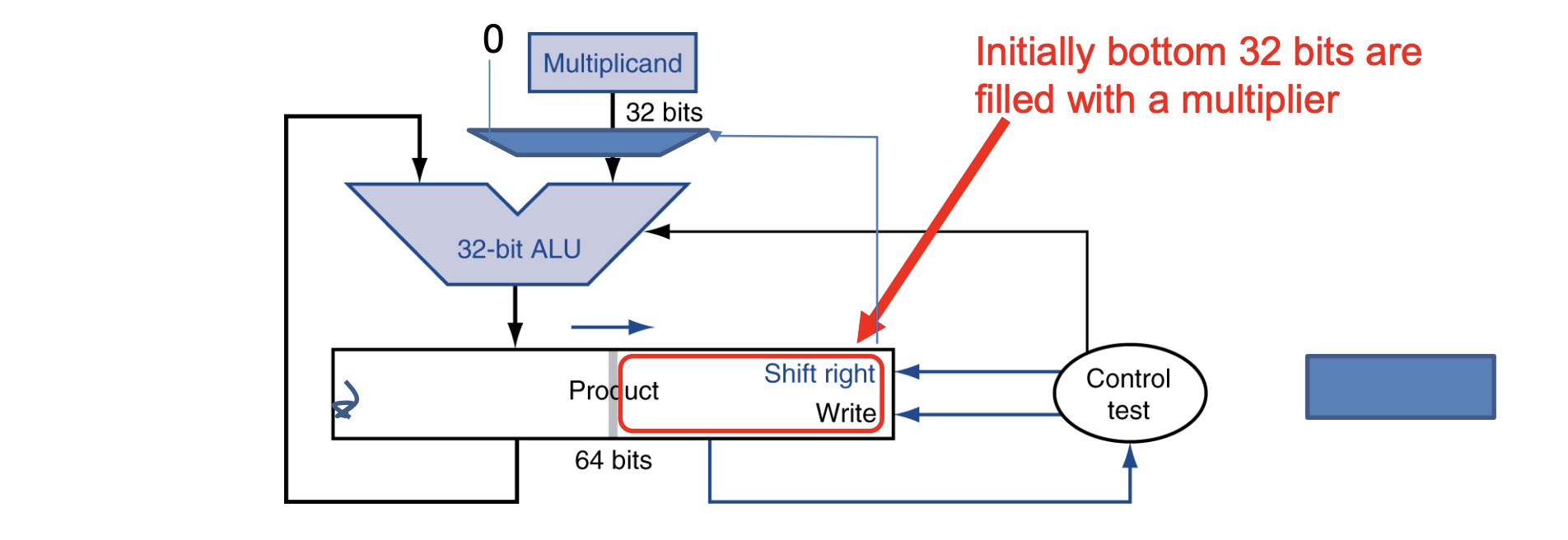

Optimized

-

multiplicand가 32bit로 바뀌었다.

multiplier register가 따로 없고, product 에 저장되어 있다. -

multiplicand가 left shift하지 않고,

product가 right shift하는 것으로 대체한다. -

multiplier의 LSB가 1일 때 product에 multiplicand를 더하는 동안

multiplicand와 multiplier의 자리이동을 같이 한다.

example

Q. 6 x 4 for optimized multiplier

6 (multiplicand) = 0110

4 (multiplier) = 0010

in product register

- 1). 0000 0010

LSB가 0이니까 위에 4bit에 multiplicand 더하지 않는다.

0000 0010

right shift

=> 0000 0001

- 2). 0000 0001

LSB가 1이니까 위에 4bit에 multiplicand를 더한다.

0110 0001

right shift

=> 0011 0000

-

3). 0011 0000

LSB가 0이니까 더하지 않는다.

right shift

0001 1000 -

4). 0001 1000

LSB가 0이니까 더하지 않는다.

right shift

0000 1100 -

ans = 0000 1100 = 24.

Q. -5 * 8 for optimized multiplier

-5(multiplicand) : 1011

8(multiplier) : 1000

in product register

- 1). 0000 1000

=> 0000 0100

- 2). 0000 0100

=> 0000 0010

- 3). 0000 0010

=> 0000 0001

-

4). 0000 0001

1011 0001

=> 1101 1000 -

1101 1000 -> 0010 0111 -> 0010 1000 = 40

ans = -40.

MIPS Multiplication

mult rs, rt

multu rs, rt

mult와 multu는 둘다 overflow를 무시한다.

mfhi rd

mflo rd

overflow를 탐지하기 위해 사용된다(?)

mul rd, rs, rt