1. 조합회로와 순차회로의 차이에 대한 이해

중요하다. 24년 시험에 이것에 대한 용어 맞추기 문제를 냈었음.

조합회로

조합회로는 입력이 출력을 결정하는 회로이다.

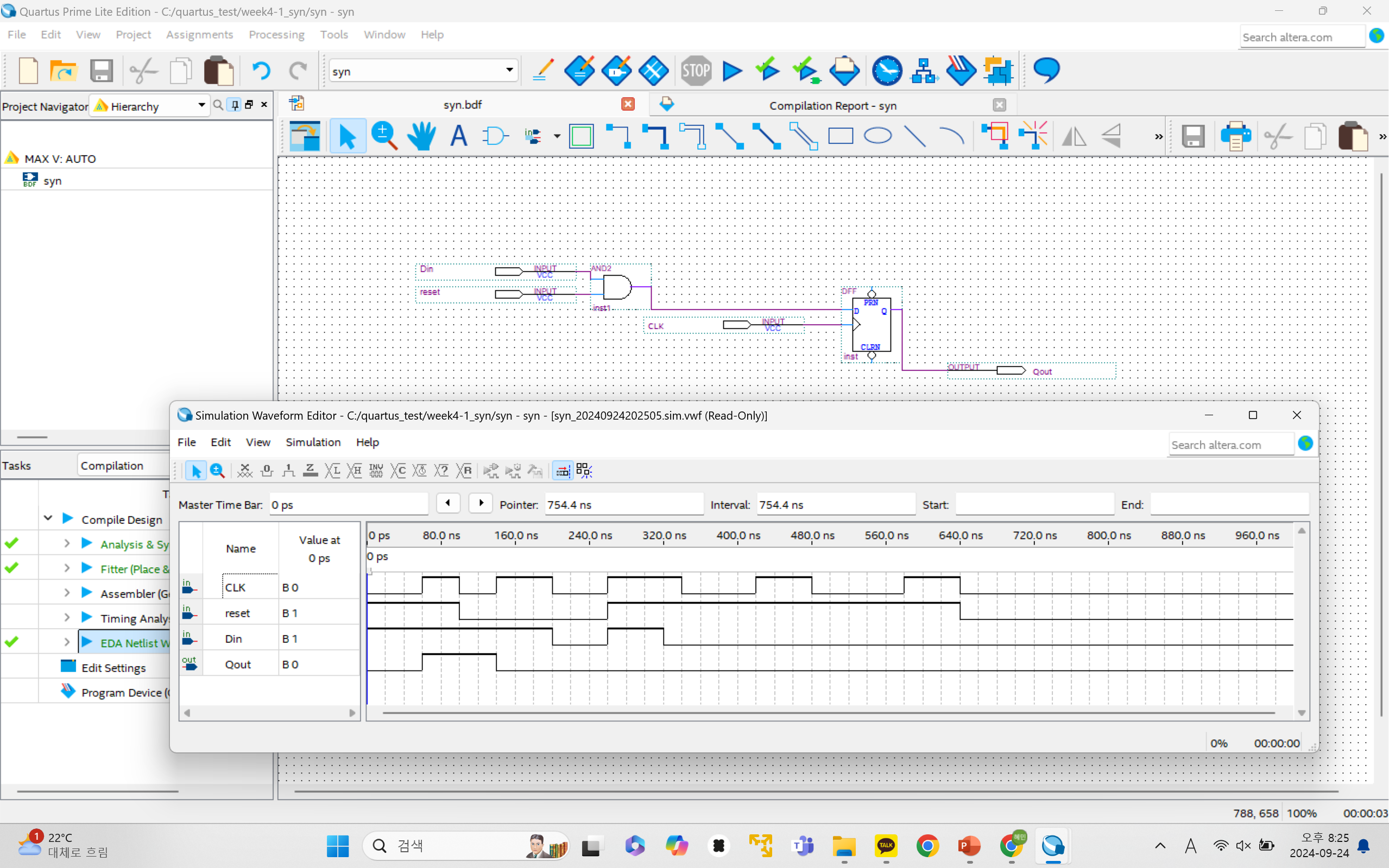

버튼 A를 누르고 있는 동안 전구에 불이 들어오게 되는 회로랑 같고 우리가 흔히 아는 and, or gate를 이용한 회로들이 다 조합회로에 속한다.

즉, 입력이 그대로 출력에 반영되는 회로라고 할 수 있다.

순차회로

순차회로는 현재 입력과 이전 상태의 조합으로 출력이 결정되는 회로이다.

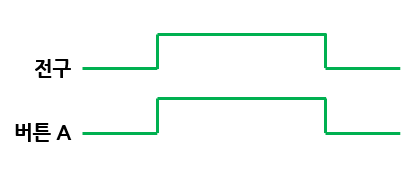

전구가 꺼진/켜진 상태에서 버튼 A를 누르면 전구가 켜짐/꺼짐 된다는 예를 살펴보자.

이전 상태 + 현재 입력(버튼 누름) + 현재 상태(출력인 셈)인 셈이다.

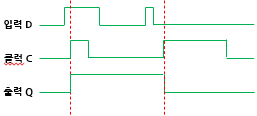

저 그림을 보면 버튼을 눌렀을 때 신호가 rising된다. 이런 빨간색 부분을 rising edge라고 할것이다. 버튼 a가 rising 되었을 때 전구는 0->1로 전환이 되고, 그다음은 1->0으로 전환이 된다.

일단 순차회로라는 녀석이 다분히 복잡한 녀석이구나... 만 알고 그다음으로 넘어가자.

2. Flip-flop의 동작과 상태에 대한 이해

Flip-flop

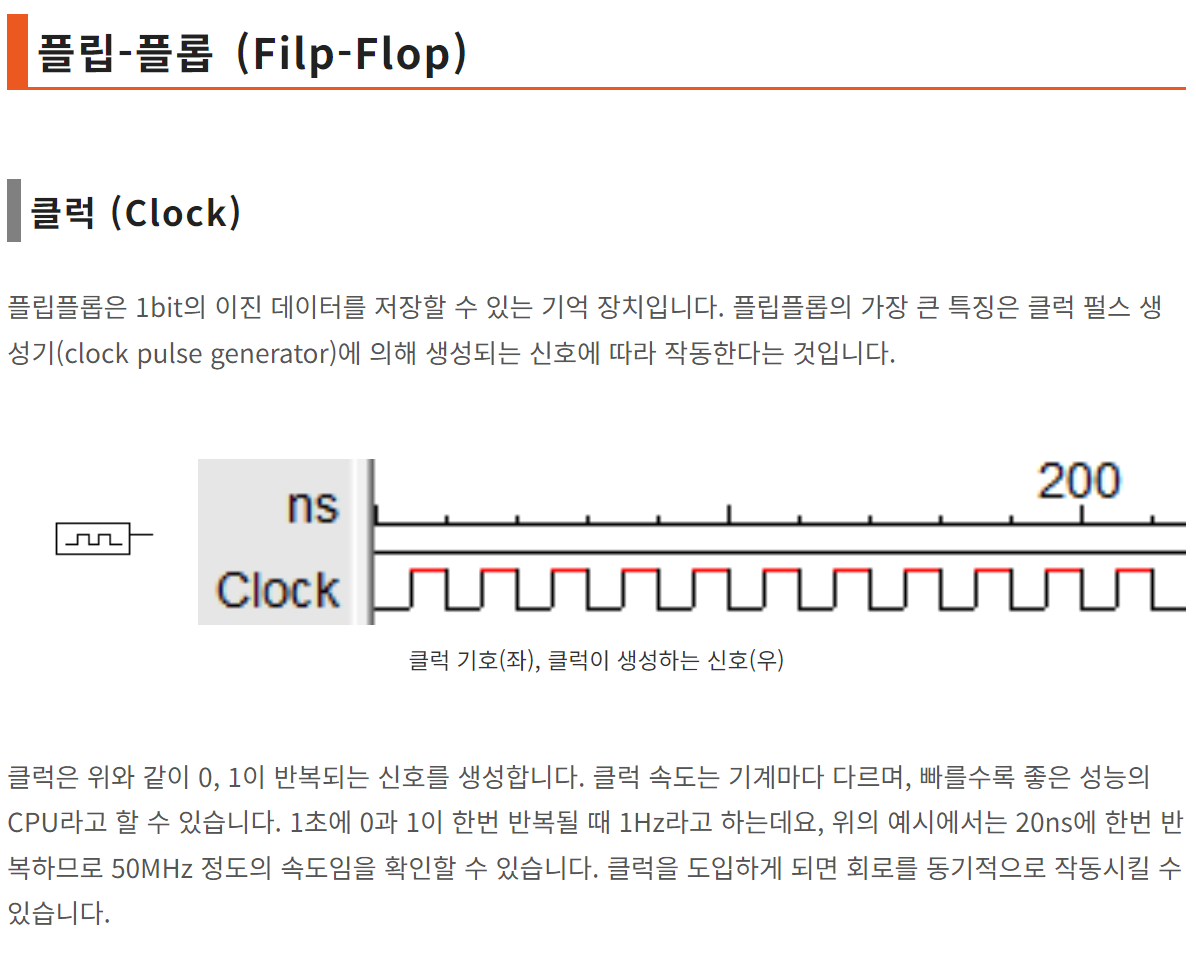

1bit의 정보를 저장할 수 있는 회로이다.

위의 출처 티스토리에서 이해할 수 있듯, flip flop은 clock이란 신호에 따라 작동하는 소자이다. clock=clk과 동일

뒤에 나오지만 flip-flop이 여러개 모여서 레지스터가 되면 이제 n bit의 정보 저장이 가능하다.

flip-flop은 대표적인 순차회로이다.

이전 상태를 반영해 현재 상태가 된다는 것은 이전을 기억한다는 뜻인데, 특히 d flip-flop은 캡쳐를 해서 이전 상태를 끌고 가므로 기억한다고 봐도 무방하다. 캡쳐에 대한 것은 조금 있다가 나온다.

d flip flop

d flip-flop은 data 혹은 delay flip-flop의 약자이다. 다음 말을 잘 이해했다면 부가설명은 안 봐도 좋다.

d flip flop은 클럭의 rising edge가 발생한 순간의 Din값을 캡쳐하여 다음 클럭의 rising edge가 발생할 때까지 저장함

저 말에 부가 설명을 하자면, d flip-flop은 플립플롭이기 때문에 클럭 동기식이다. 영어로 하면(Clock) Synchronous D flip-flop. 클럭 동기식은 clock의 edge에서 flip-flop의 Qout이 동일하게 움직인다는 뜻이다.

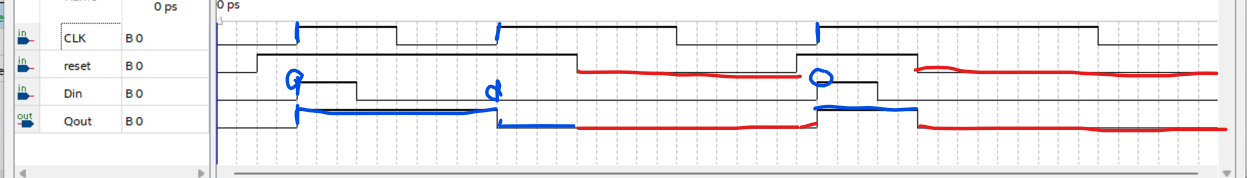

사진을 보면 클락이 라이징될 때 din의 1을 캡처해서 다음 클락이 rising 될 때까지 끌고간다. 그리고 다음 클락이 rising 되면 din의 0을 캡쳐해서 끌고간다.

회로 그릴 때

-

clock은 하나의 input 소자로 다 연결하면 된다.

-

d는 data 입력값이고 Q는 출력값이다. reset은 다음 사진에서 설명할거지만 하나의 reset으로 연결한다.

-

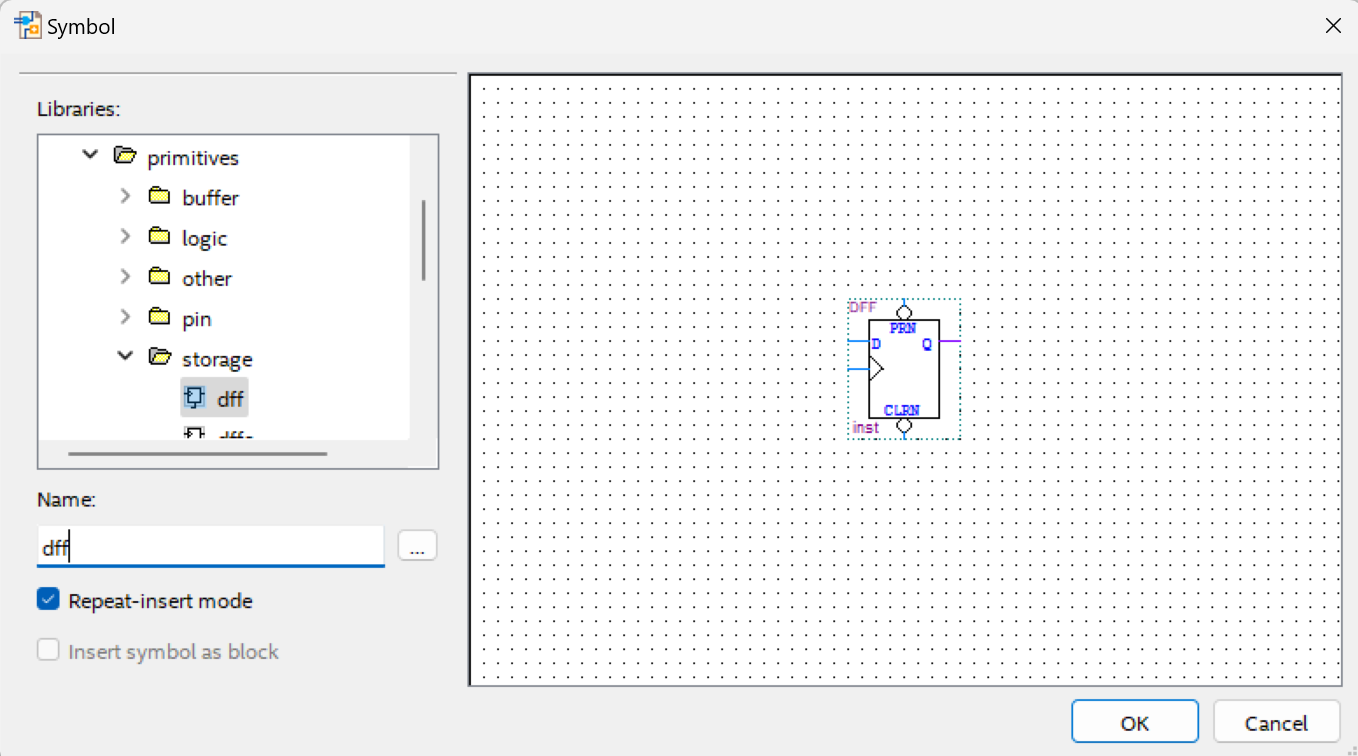

quartus에서 symbol 입력하는 빈 창에 dff치면 d flip flop이 나온다.

-

일반적인 d flip flop을 보면 reset에 not(동그라미)이 붙어있다. 이것을 reset not 줄여서 rstn이라고 한다.

reset이라는 건 0으로 초기화되는 것인데, 일반적인 소자에서는 reset에 not이 붙여져 있으므로 reset이 1일 때 Qout이 0이 된다는 점 조심해야 한다!!

계속 헷갈리는 부분인데 꼭 숙지하도록~

dff가 있는 회로에서는 rst에 not이 필수적으로 붙어있기 때문에 1일때 reset이 비활성화, rst이 0일때 reset이 활성화이다. 그런데 나중 가서는 보드에서 실습할 때는 reset을 아무데도 안쓰이는 핀에다가 연결시키기 때문에 0일 때 비활성화로 만들어야 한다. 따라서 보드에서 실습할 때는 input인 rst에다가 not 기호를 붙여서 실습해야 한다.

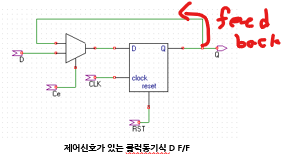

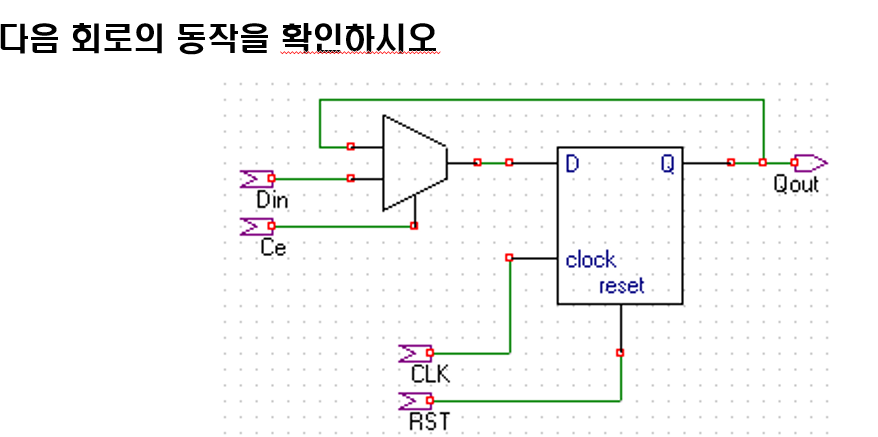

제어신호를 이용한 값의 저장도 가능

앞에 사진에서 ce와 mux가 추가된 그림이다.

제목을 뜻풀이 하자면 제어신호를 이용한다는 게 mux의 입력신호 ce를 활용한다는 뜻이다.

멀티플렉서(multiplexer) 또는 mux는 여러 아날로그 또는 디지털 입력 신호 중 하나를 선택하여 선택된 입력을 하나의 라인에 전달하는 장치이다 = ce에 따라 둘중 하나 선택

ce는 clock enable의 약자로 dff에 들어가는 clock을 enable 해줄지 아닐지 고려한다.

ce가 0이면 현재 상태를 유지한다.

ce가 1이면 D의 값으로 초기화한다.

왜냐면

ce가 0이면

dff이 아무리 clock rising해도 반응을 안한다

= feedback 신호(이전신호)가 그대로 다음신호로 들어간다

반면, ce가 1이면

이전 상태와 상관없이 clk에 따라 d값이 1이면 Qout이 1이된다.

d값이 0이 되면 Qout이 0이 된다.

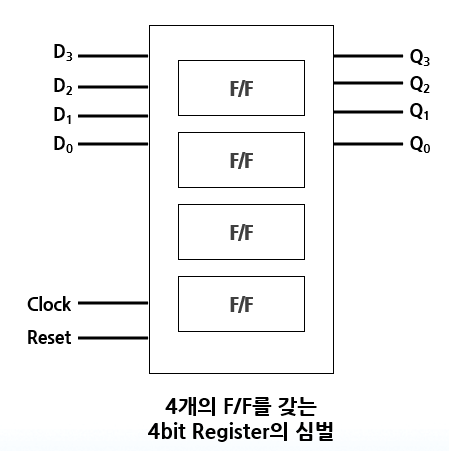

3. Register의 이해와 구현

드디어 register다.

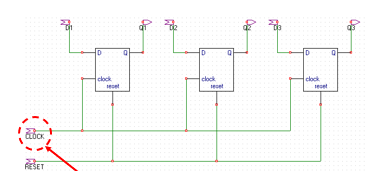

register

- n개의 flip-flop가 병렬로 이루어짐

- 각 ff은 동일 clock, 동일 reset으로 연결됨

- 레지스터로 데이터의 이동을 할 수 있는데 일반적으로는 register의 데이터는 동시에 전달된다.

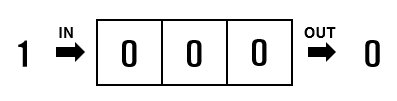

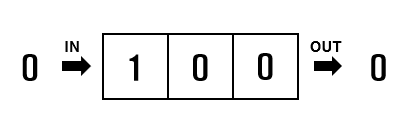

shift register

- 그러나 shift register는 데이터가 동시가 아니라 그다음 clock을 만났을 때 전달되는 레지스터이다.

뭐 쭉쭉 오른쪽으로 넘겨지면? 결과값으로 1이 나오게 되는데 이건 생략. 쭉쭉 단계별로 넘어가는 것 = 이건 clock을 만났을 때 = clock이 rising일 때를 의미한다.

ppt에는 input이 계속 1이라고 잘못 기재되어 있었음

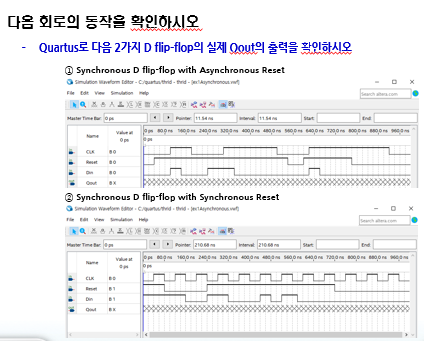

4. 실습

실습1

실습 1번은 두가지 구현이다.

- synchronus dff with asynchronous reset

dff는 clk에 대해 동기인데 reset과 clk은 비동기인 경우이고 a-싱크로너스는 비동기라는 뜻

reset이 켜져도 clk과 아~무 상관없이 qout이 바로 reset된다고 생각하면 됨. - synchronous dff with synchronous reset

clk에 대해 동기인데 reset이 0이 된다 하더라도? clk이 1이 되어야 reset이 된다.

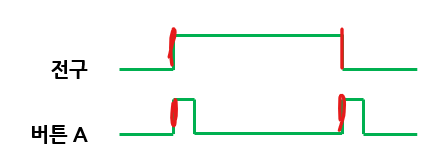

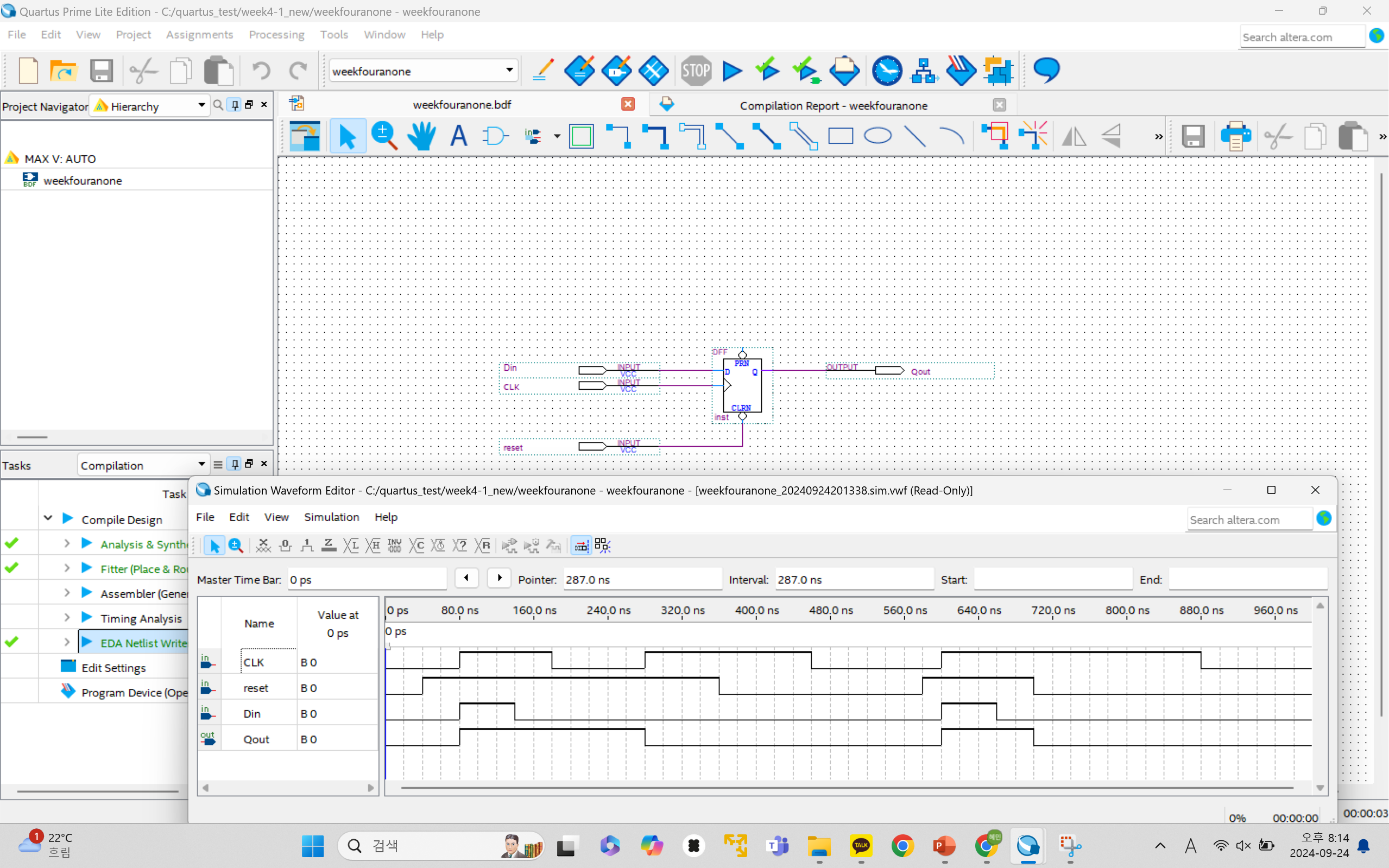

위 사진은 synchronus dff with asynchronous reset 구현한 것.

일반적으로 연결할 곳 다 연결하면 비동기 리셋 dff이다.

결과를 볼 때 조심해야하는 건 아까 말했듯 reset값이 0이 되어야 q도 0이 되는 점이다. not이 붙어있으니까.

reset=0이면 clk과 상관없이 qout도 0이 됨(빨강)

reset=1이면 clk이 rising일 때 Din의 값을 캡처해서 다음 clk이 rising일 때까지 끌고감. 근데 reset=1 되어도 clk이 rising 안되면 이전 값 끌고감.

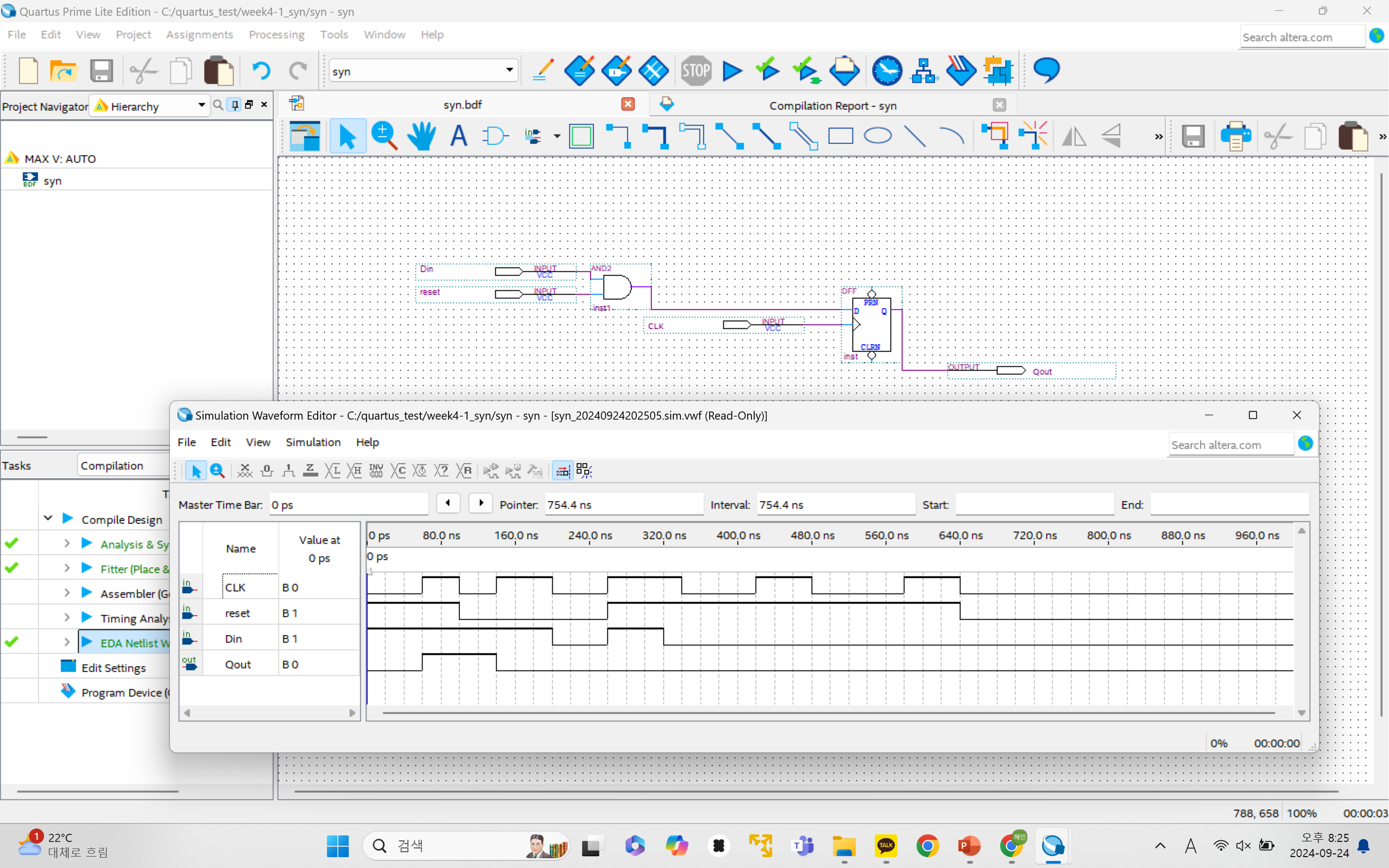

위사진은 동기 리셋이다.

아까랑 다른 점은

Din이랑 reset이 and gate로 묶여서 dff의 d로 들어간다는 점이 있다. (나머지는 맞는 자리에 clk, qout 연결)

and gate로 묶이는 것의 의미는

reset이 0이면= reset이 활성화되면, Din이 어떻든 0이고,

reset이 1이면= reset이 비활성화되면, Din 값대로 Din이 들어가게 하는 것인데,

근데 이것은 다 clock의 영향 아래에 놓여있다는 것이다.

따라서 결과를 보면

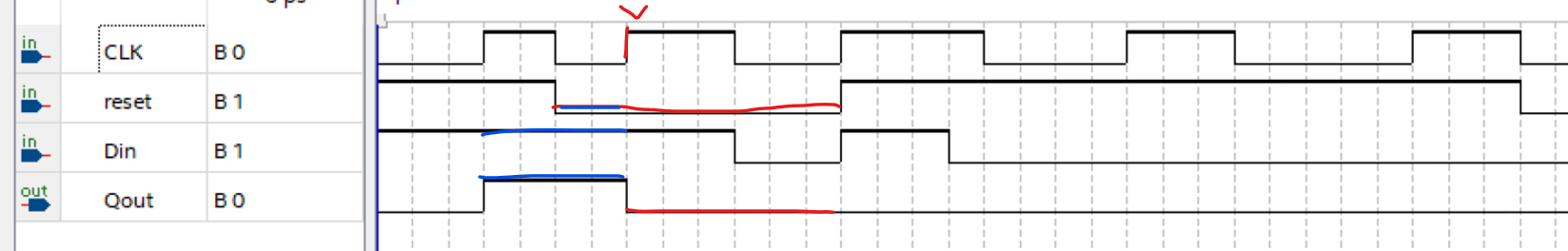

reset이 0이어도=활성화되어도 clk이 1이지 않으면 qout은 1이고=Din의 값을 반영하고(파란색),

clk이 비로소 rising이면(빨간색) reset을 반영해 qout이 0이 되는 것을 확인할 수 있다.

clk, reset, din이 한꺼번에 1이 되는 상황에서는 qout이 0이 되는데, 이것은 delay 때문일 것이라고 추측하고 있다. 이유를 아시는 분은 댓글 달아주세요 ㅠㅠ

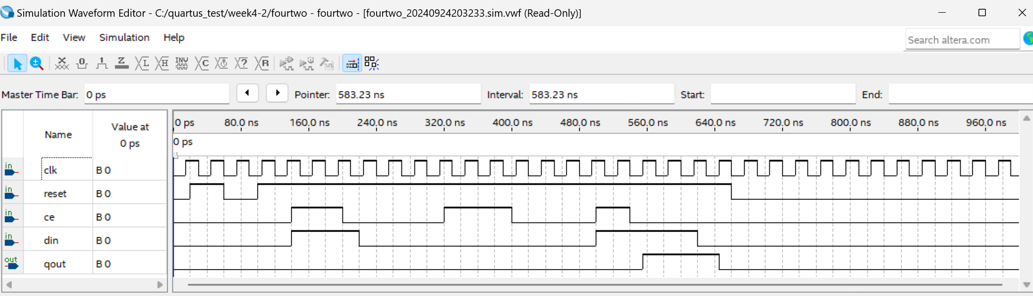

실습2

FDRE: Dff with Sync Reset and Clock Enable(A-sync)

앞의 제어신호를 이용한 dff를 그대로 실험해보는 예시이다.

ce와 clk는 무관하게 연결되어 있어서 a-sync이고,

이것은 ce의 의미를 생각해보면 왜 무관하게 연결되어야 하는지 알 것

ce가 0이면 현재 상태를 유지한다.

ce가 1이면 D의 값으로 초기화한다.

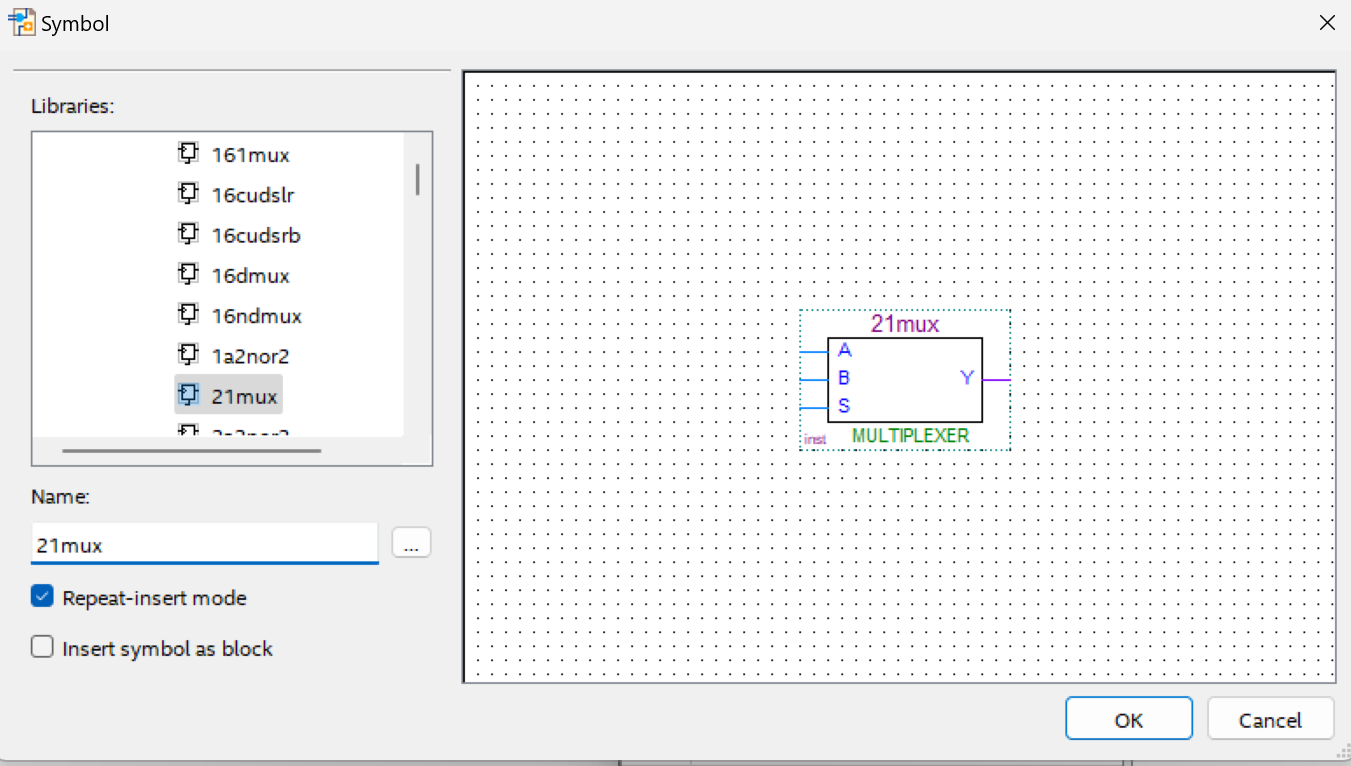

2:1 mux는 21mux라고 quartus에 검색하면 나온다.

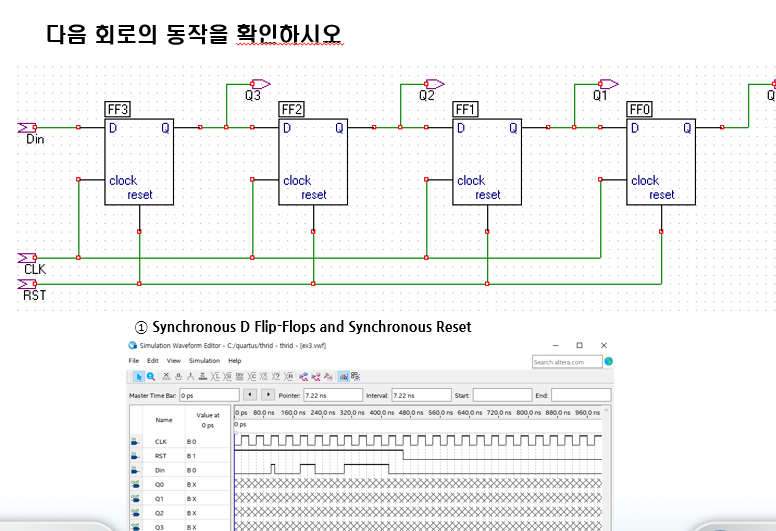

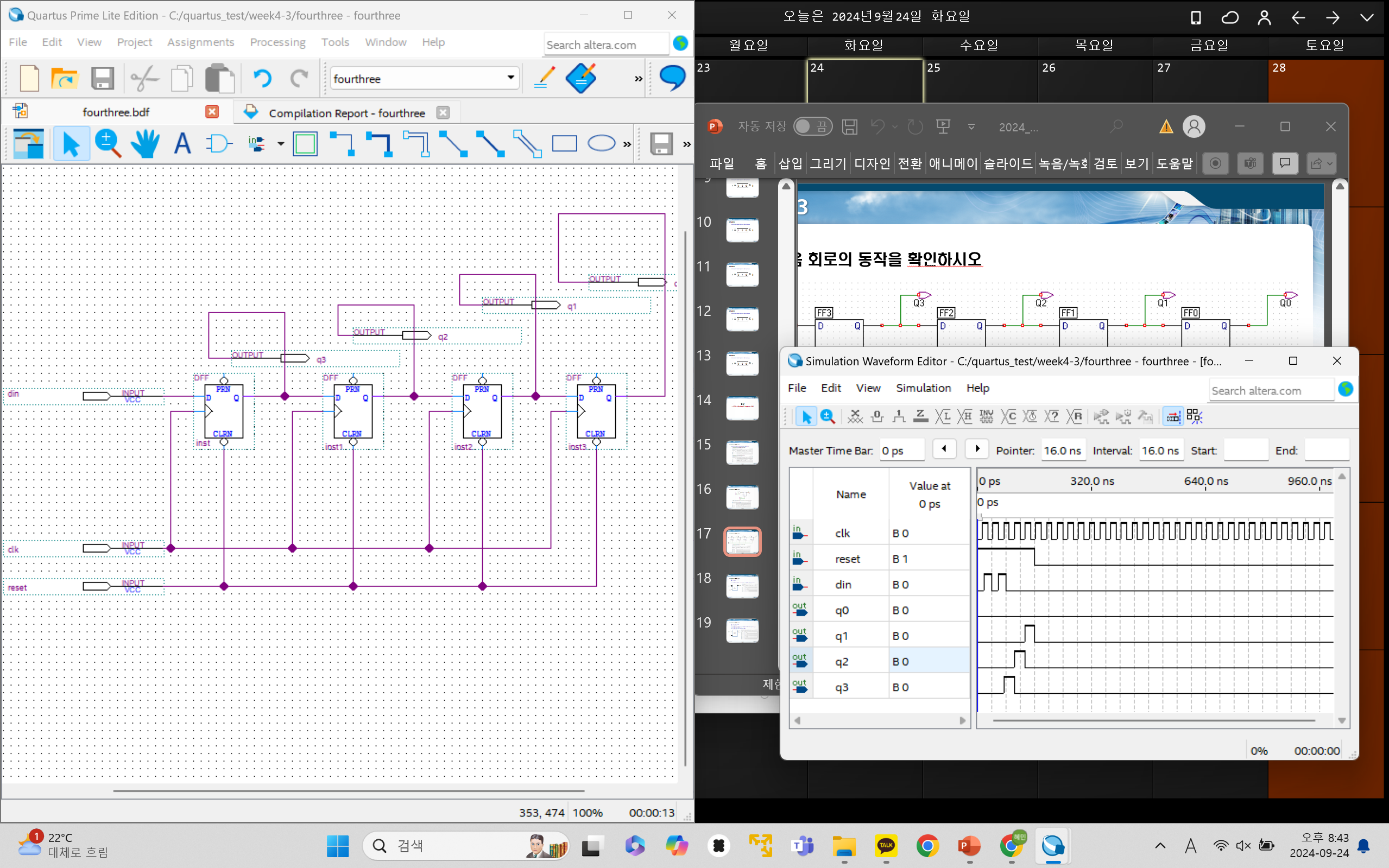

실습3

실습3 == shift register 만들기

shift인 이유는 flip-flop이 직렬로 연결되어있고

이전 결과가 다음의 입력이 되기 때문. (= flip된다고 한다)

clock이 rising edge가 되면 이전게 다음으로 넘어가는 거기 때문에

즉, 딜레이가 있기 때문에 다음과 같이 움직인다...

1번째 : 1 0 0 0

2번째 : 0 1 0 0

3번째 : 0 0 1 0

아래처럼 동시에 가는게 아니다.

틀린예 ↓

1번째 : 1 0 0 0

2번째 : 1 1 0 0

3번째 : 1 1 1 0

clk에 맞춰 din이 들어갔고

그다음 1이 q3 -> q2 -> q1 -> q0 순으로 들어가는 모양새.

실수로 reset 비활성화되는 부분을 짧게 잡아서 q0까지는 전달이 안되는 모습을 볼 수 있다.

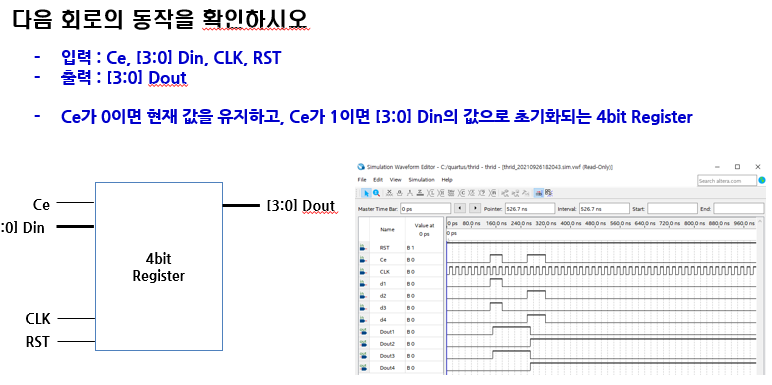

실습4

4bit register는 4개의 dff를 병렬로 놓는 것이다

din[3:0]에 들어있는 1010값이 그대로 캡쳐되어서

Q[3:0]으로 동시에 값이 나온다.

그다음 0101로 지정하면 0101 값이 그대로 값이 나온다.

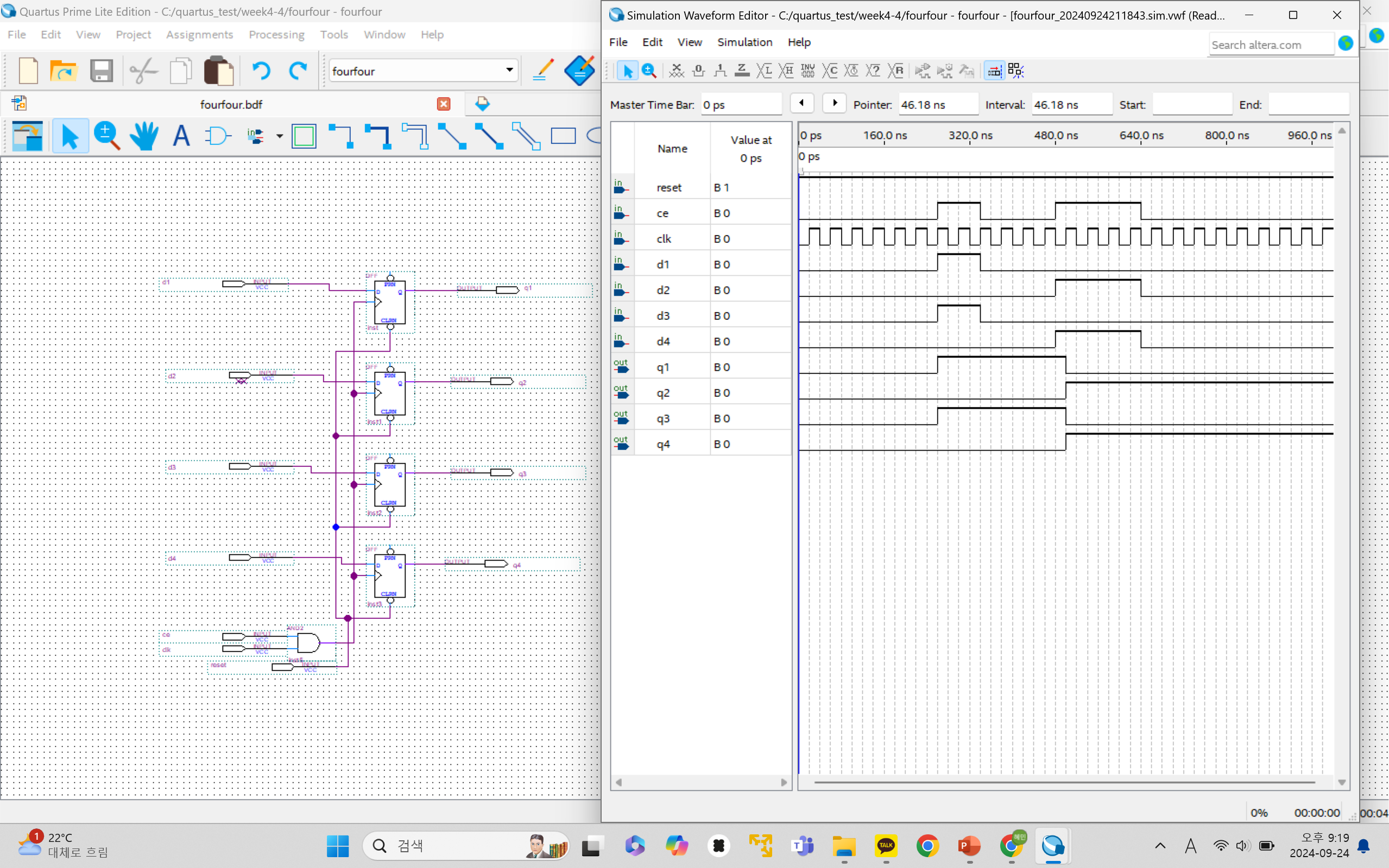

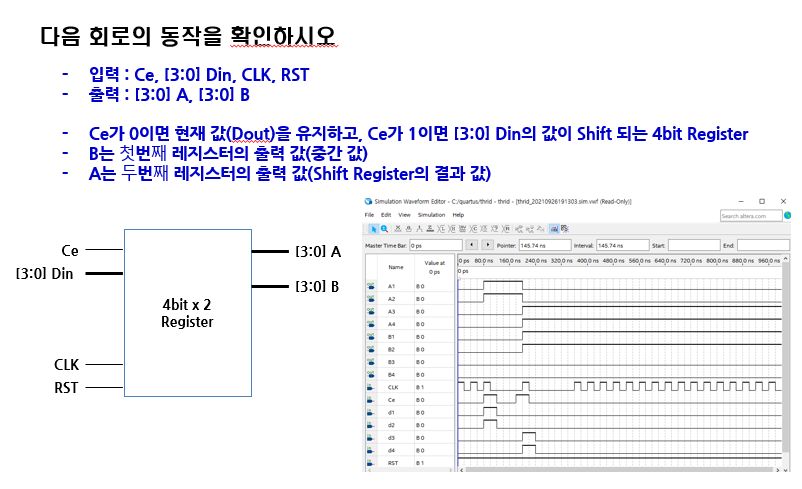

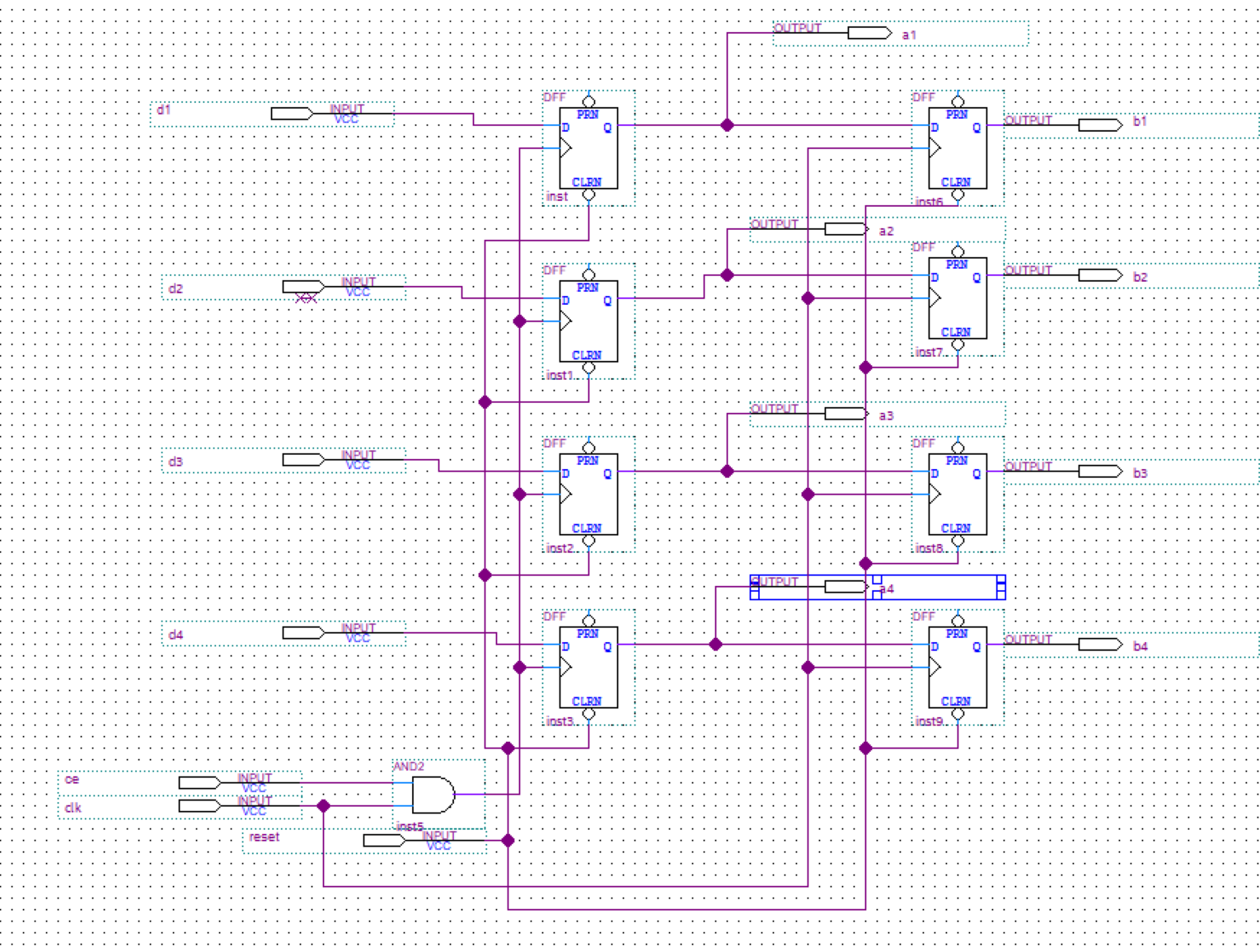

실습5

저기 오타가 있는데 A가 첫번째 레지스터의 출력값이자 중간값,

B가 결과값이다. 조심!

실습4의 4비트 레지스터를 직렬로 나두면 된다. =3주차의 심볼화로 하면 더 간단함

d에 1 1 0 0을 넣어서 A값이 1 1 0 0 일때

B값은 0 0 0 0 이다.

그다음 clk이 되면

d에 0 0 1 1을 넣었기에 A가 0 0 1 1이 되고

B값은 이전의 d에서 넘어와서 1 1 0 0이 된다.

즉 shift 되는 4bit 레지스터 완성.

회로를 보면 두개의 레지스터를 심볼화해서 나타내면 더 간단한 걸 알 수 있다.

그리고 ce에 따라서 shift 되어야 하는데,

기존에는 clk에 맞춰서 shift되었기 때문에

clk과 ce를 and gate로 묶으면 이젠 clk이 있어도 ce가 없으면 작동을 안하게 되므로,

원하던 대로 ce에 맞춰서 shift되게 할 수 있다.