Device Driver & Device Controller

Device controller is responsible for moving the data between the peripheral devices that it controls and its local buffer storage.

Device driver understands the device controller and provides the rest of the operating system with a uniform interface to the device.

OS have a device driver

Interrupts

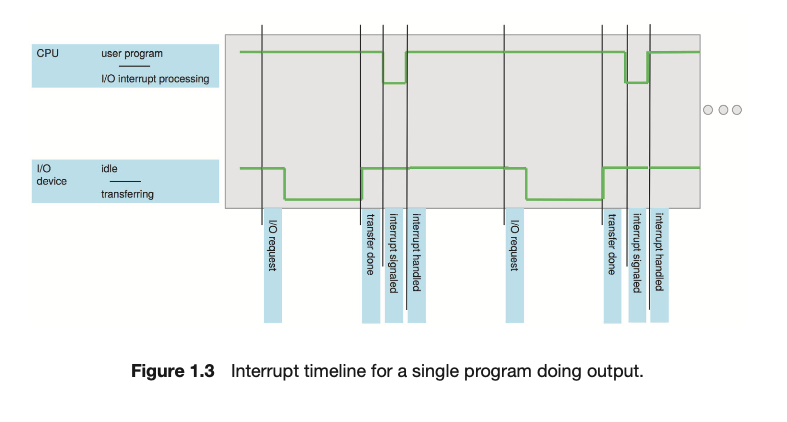

A program performing I/O.

-

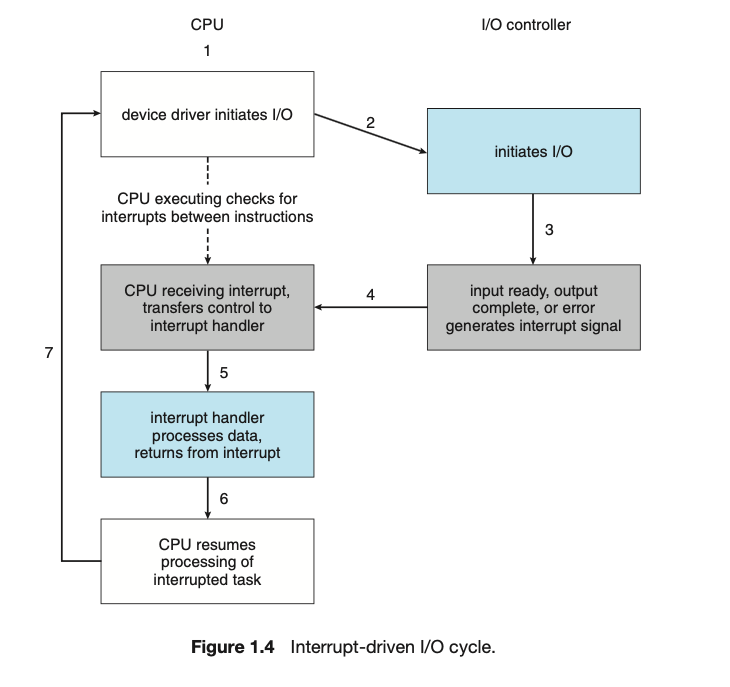

To Start an I/O operation, the

Device driverloads the appropriate registers in theDevice controller. -

The

Device controller, in turn, examins the contents of these registers to determine what action to take(such as "read a character from the keyboard")

TheDevice controllerstarts the transfer of data from the device to its local buffer. -

Once the transfer of data is complete, the

Device controllerinforms theDevice driverthat it has finished its operation. -

Device driverthen gives control to other parts of the operating system, possibly returning the data or a pointer to the data if the operation was a read. -

For other operations, the Device driver returns status information such as "write completed successfully" or "device busy".

But how does the controller inform the Device driver that it has finished its operation?

This is accomplished via in Interrupt.

-

Hardware may trigger an interrupt at any time by sending a signal to the CPU, usually by way of the system bus : System bus is the main communications path between the major components.

-

Interrupts are used for many other purposes as well and are a key part of how operating systems and hardware interact.

-

When the CPU is interrupted, it stops what it is doing and immediately transfers execution to a fixed location.

-

The fixed location usually contains the starting address where the service routein for the interrupt is located.

-

The interrupt service routine executes; on completion, the CPU resumes the interrupted computation.

-

Interrupts are an important part of a computer architecture

-

Each computer design has its own interrupt mechanism, but several functions are common.

-

The interrupt must transfer control to the appropriate interrupt service routine.

-

The straightforward method for managing theis transfer would be to invoke a generic routine to examine the interrupt information.

-

Interrupts must be handled quickly, as they occur very frequently.

Interrupt Vector

Generally, the table of pointers is stored in low memory (the first hundred or so locations). This array of addresses is called Interrupt vector.

- Operating systems as different as Windows and UNIX dispatch interrupts in this manner.

- The interrupt architecture must also save the state information of whatever was interrupted, so that it can restore the information after servicing the instance, by modifying register values.

Implementation

[Basic Interrupt Mechanism]

-

The CPU hardware has a wire called the interrupt-request line that the CPU senses after executing every instruction.

-

When the CPU detects that a controller has asserted a signal on the interrupt-request line, it reads the interrupt number and jumps to the interrupt-handler routine by using that interrupt number as an index into the interrupt-handler routine by using that interrupt number as an index into the interrupt vector.

-

It then starts execution at the address associated with that index. The interrupt handler saves any state it will be changing during its opertaion, determines the cause of the interrupt, performs the necessary processing, performs a state restore, and executes a

return_from_interruptinstructtion to return the CPU to the exectuion state prior to the interrupt.We say that,

-

Device controller raises an interrupt by asserting a singal on the interrupt request line, the CPU catches the interrupt and dispatches it to the interrupt handler, and the handler clears the interrupt by servicing the device.

The basic interrupt mechanism just described the CPU to respond to an asynchronous event, as when a device controller becomes ready for service.

Sophiscated Features

- We need the ability to defer interrupt handling during critical processing.

- We need an efficient way to dispatch to the proper interrupt handler for a device

- We need multilvel interrupts, so that the operating system can distinguish between high and low-priority interrupts and can respond with the appropriate degree of uergency.

In modern computer hardware, these features are provided by the CPU and the interrupt-controller hardware.

Most CPUs have two interrupt request lines.

- Nonmaskable interrupt : reserved for events such as unrecoverable memory errors

- Maskable interrupt : it can be turned off by the CPU before the execution of critical instruction sequences that must not be interrupted. It is used by device controllers to request service.

Through interrupt chaining in which each element in the interrupt vector points to the head of a list of interrupt handlers we can solve this problem.

When an interrupt is raised, the handlers on the corresponding list are called one by one, until one is found that can service the request. this structure is compromise between the overhead of a huge interrupt table and the inefficiency of dispatching to a single interrupt handler.

Summary

Interrupts are used throughout modern operating systems to handle synchronous events (and for other purposes). Device controllers and hardware faults raise interrupts. To enable the most urgent work to be done first, modern computers use a system of interrupt priorities. Because interrupts are used so heavily for time-sensitive processing, efficient interrupt handling is required for good system performance.