운영체제(다중 단계 페이징 시스템)

다중 단계 페이징 시스템

-

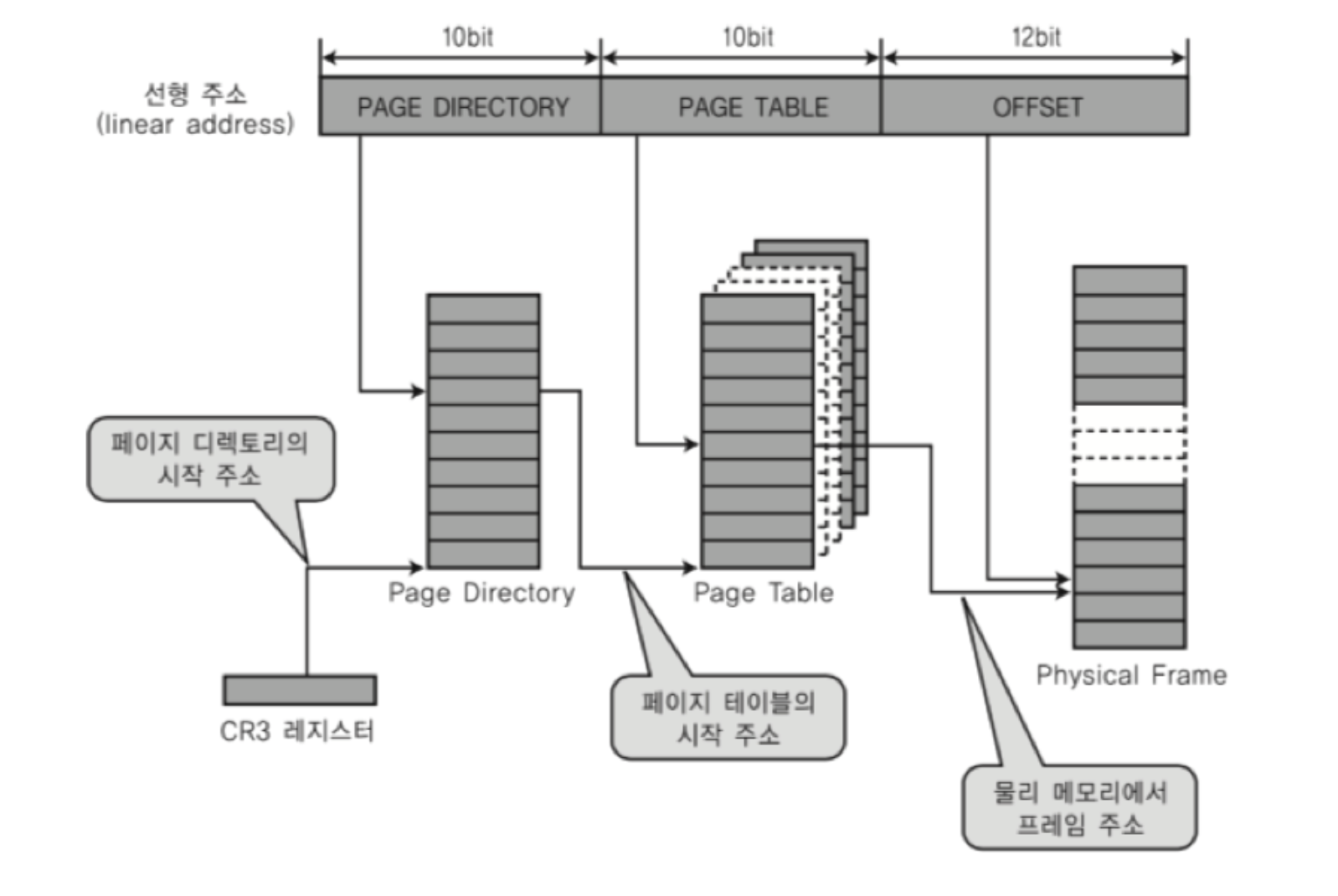

32bit시스템에서 4KB 페이지를 위한 페이징 시스템의 구성은 다음과 같다.

- 하위 12bit는 오프셋

- 상위 20bit는 페이징 번호이므로, 2의 20승(1048576)개의 페이지 정보가 필요함 (쓰는 코드양에 비해서 정보가 너무 많음)

-

그래서 페이징 정보를 단계를 나누어 생성 한다.

- 필요없는 페이지는 생성하지 않으면, 공간 절약이 가능하다.

- 페이지 번호를 나타내는 bit를 구분해서, 단계를 나눈다.(리눅스 3단계, 최근 4단계)

MMU와 TLB(컴퓨터 구조)

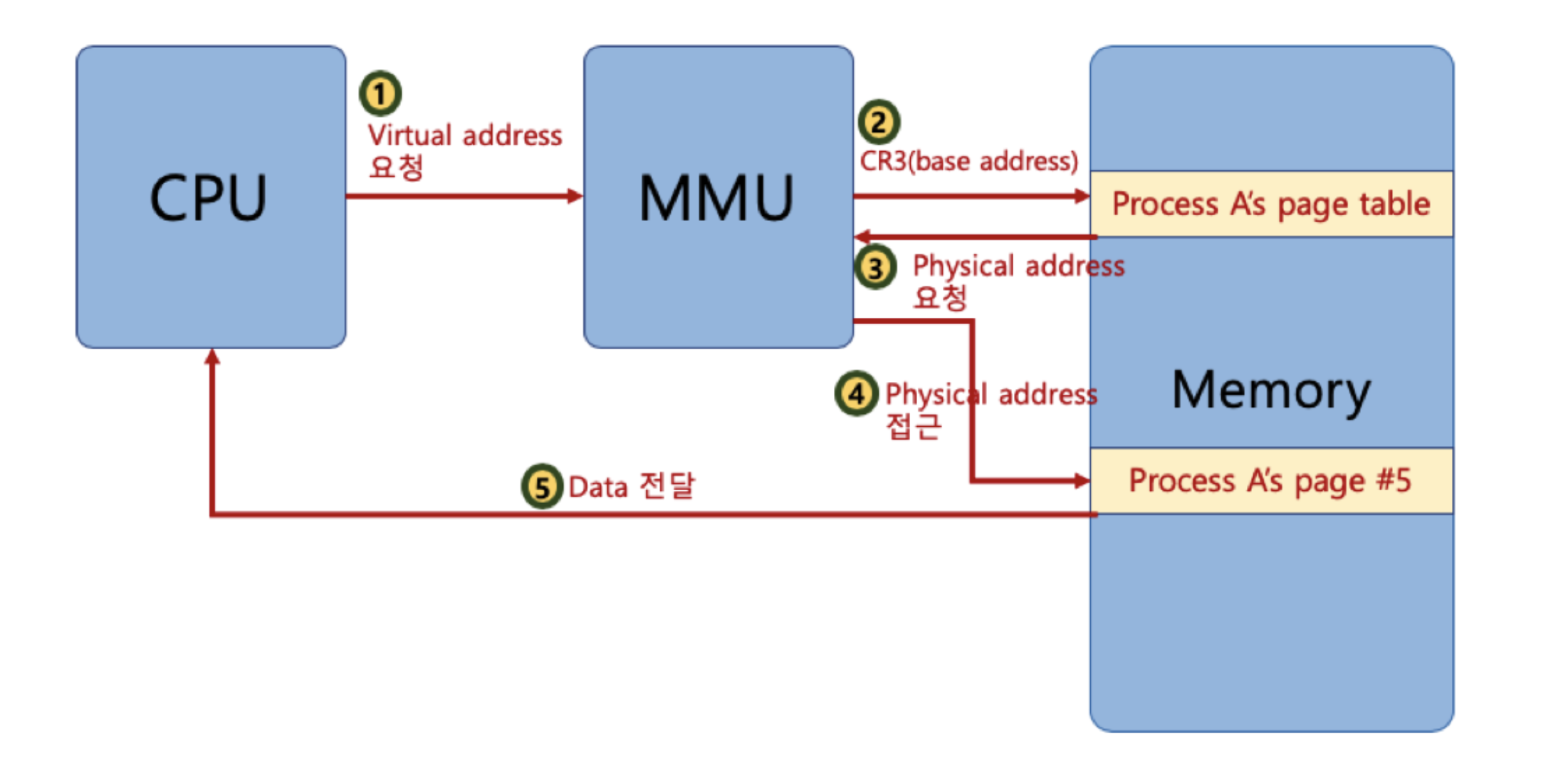

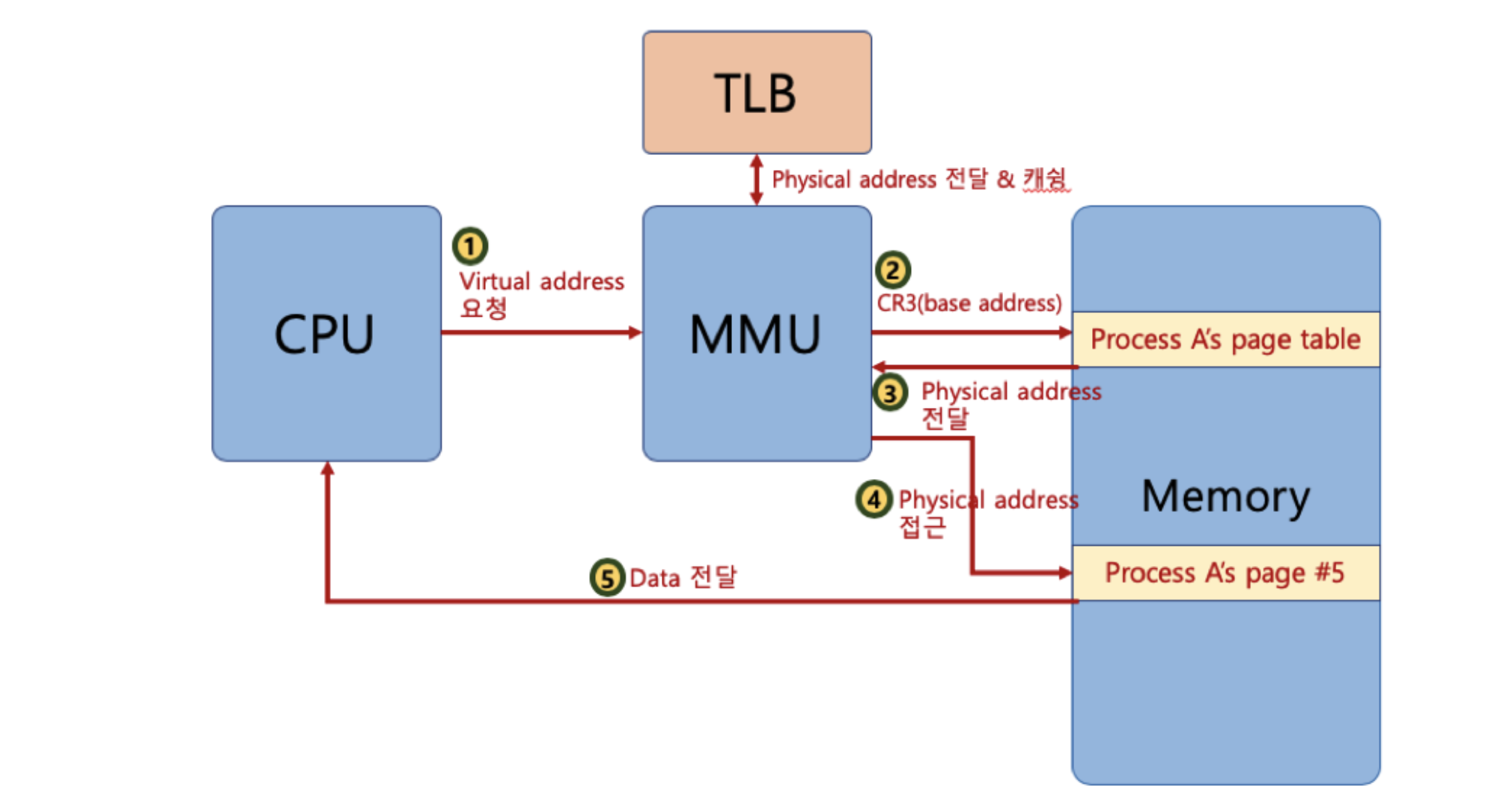

- MMU가 물리 주소를 확인하기 위해 메모리를 갔다와야 한다. 그래서어!

- TLB(Translation Lookaside Buffer): 페이지 정보 캐쉬

- 3번 4번 과정이 생략되서 메모리에 왔다갔다 하는 시간을 줄인다.

x0x