▋ 개요

프로젝트명 : DC 모터 컨트롤러

기획 및 제작 : 박순창

분류 : 메인 프로젝트 (개인)

시작/제작 기간 : 23.10.00 ~ 23.10.00 (1일)

진행상태: 스펙 정의 - 기능 검증 - RTL 생성 - 시뮬레이션 - 합성 및 배선진행중

사용 툴:Vivado,Xcelium,Genus,Innovus

사용 도구:FPGA

▋ 설명

▶ 개발 동기

DC모터 2개를 컨트롤 하는 드라이버 설계

▶ Spec

ㅇDA 모터

- 내부 구조

1) MODE Selector

2) Wheel PWM Controller

- 핀 구조

1) PWM

2) INA, INB, INC

3)

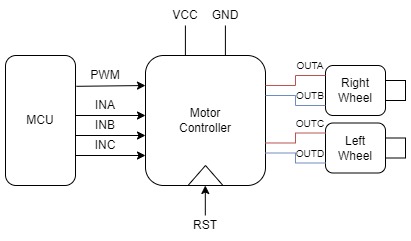

▶ Diagram

-

System Diagram

-

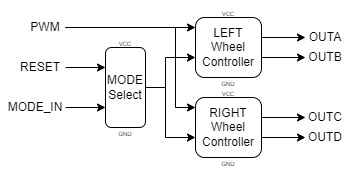

Block Diagram

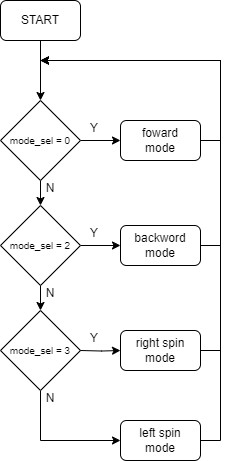

▶ 알고리즘

▋Code

- DC_Motor_Controller.v

`timescale 1ns/1ps

module DC_Motor1 (pwm_in, rst, mode_Sel, pwm_Ra, pwm_Rb, pwm_La, pwm_Lb);

input pwm_in;

input rst;

input [2:0] mode_Sel;

output reg pwm_Ra;

output reg pwm_Rb;

output reg pwm_La;

output reg pwm_Lb;

parameter STANDBY = 0;

parameter FORWORD = 1;

parameter BACKWORD = 2;

parameter RIGHT_TURN = 3;

parameter LEFT_TURN = 4;

parameter BRAKE = 5;

reg [2:0] mode;

always @(*) begin

if(rst) mode <= STANDBY;

else begin

case (mode_Sel)

3'b000: mode <= STANDBY;

3'b001: mode <= FORWORD;

3'b010: mode <= BACKWORD;

3'b011: mode <= RIGHT_TURN;

3'b100: mode <= LEFT_TURN;

3'b101: mode <= BRAKE;

default: mode <= STANDBY;

endcase

end

end

always @(*) begin

case(mode)

STANDBY: begin

pwm_Ra <= 1'b0;

pwm_La <= 1'b0;

pwm_Rb <= 1'b0;

pwm_Lb <= 1'b0;

end

FORWORD: begin

pwm_Ra <= pwm_in;

pwm_La <= pwm_in;

pwm_Rb <= 1'b0;

pwm_Lb <= 1'b0;

end

BACKWORD: begin

pwm_Ra <= 1'b0;

pwm_La <= 1'b0;

pwm_Rb <= pwm_in;

pwm_Lb <= pwm_in;

end

RIGHT_TURN: begin

pwm_Ra <= 1'b0;

pwm_La <= pwm_in;

pwm_Rb <= pwm_in;

pwm_Lb <= 1'b0;

end

LEFT_TURN: begin

pwm_Ra <= pwm_in;

pwm_La <= 1'b0;

pwm_Rb <= 1'b0;

pwm_Lb <= pwm_in;

end

BRAKE: begin

pwm_Ra <= pwm_in;

pwm_La <= pwm_in;

pwm_Rb <= pwm_in;

pwm_Lb <= pwm_in;

end

endcase

end

endmodule- DC_Motor_Controller_tb.v

`timescale 1ns/1ps

module DC_Motor1_tb;

reg pwm_in, rst;

reg [2:0] mode_Sel;

wire pwm_Ra, pwm_Rb, pwm_La, pwm_Lb;

DC_Motor1 dc1 (pwm_in, rst, mode_Sel, pwm_Ra, pwm_Rb, pwm_La, pwm_Lb);

task expect;

input [2:0] mode;

if(rst) begin

if(pwm_Ra || pwm_Rb || pwm_La || pwm_Lb) begin

$display("rst TEST OK");

end

else begin

$display("rst TEST FAILED");

$display("At time %0d rst=%b Ra=%b Rb=%b La=%b Lb=%b",

$time, rst, pwm_Ra, pwm_Rb, pwm_La, pwm_Lb);

$finish;

end

end

endtask

initial forever begin

#3 pwm_in <= ~pwm_in;

#7 pwm_in <= ~pwm_in;

#1 pwm_in <= ~pwm_in;

#9 pwm_in <= ~pwm_in;

#5 pwm_in <= ~pwm_in;

#5 pwm_in <= ~pwm_in;

end

initial begin

$display("test start");

pwm_in <= 1'b0; rst <= 1'b0;

#10 mode_Sel <= 3'd0; $display("STANDBY TEST OK");

#10 mode_Sel <= 3'd1; $display("FORWORD TEST OK");

#10 mode_Sel <= 3'd2; $display("BACKWORD TEST OK");

#10 mode_Sel <= 3'd3; $display("RIGHT_TURN TEST OK");

#10 mode_Sel <= 3'd4; $display("LEFT_TURN TEST OK");

#10 mode_Sel <= 3'd5; $display("BRAKE TEST OK");

#10 rst <= 1'b1; expect (mode_Sel);

#10 $display("test fisnish");

$finish;

end

endmodule▋Test

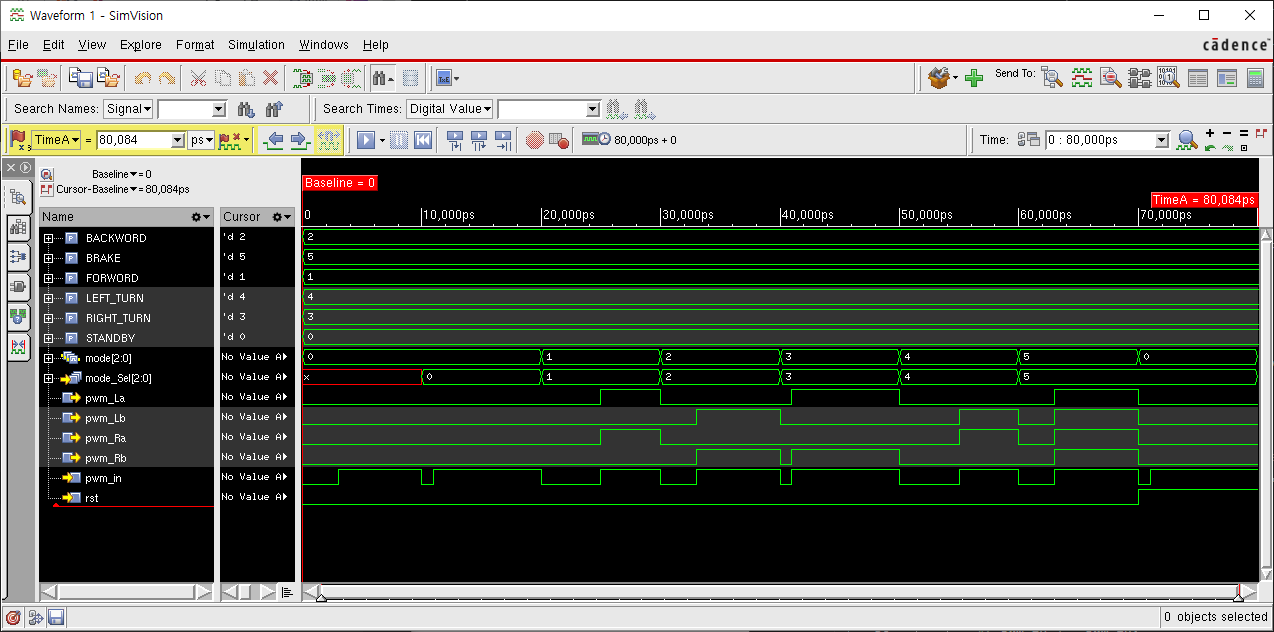

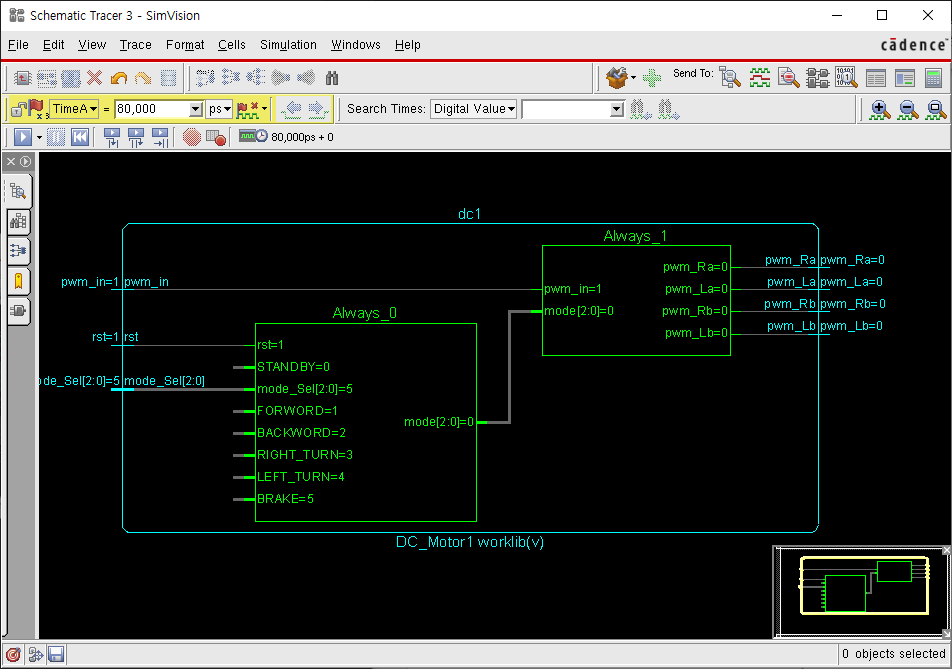

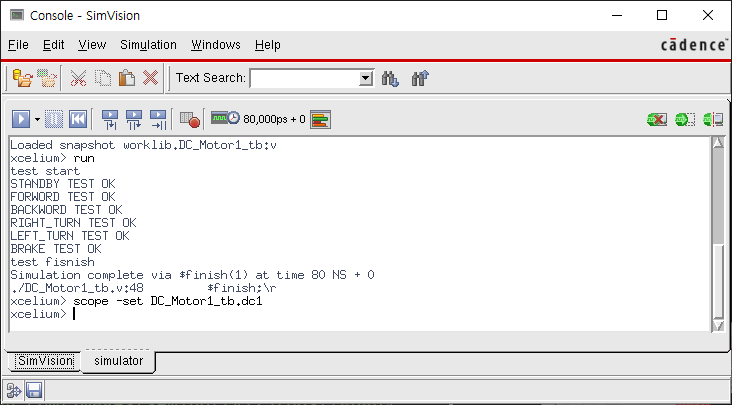

▶ Simulation

- Waveform

- Block Diagram

- Log

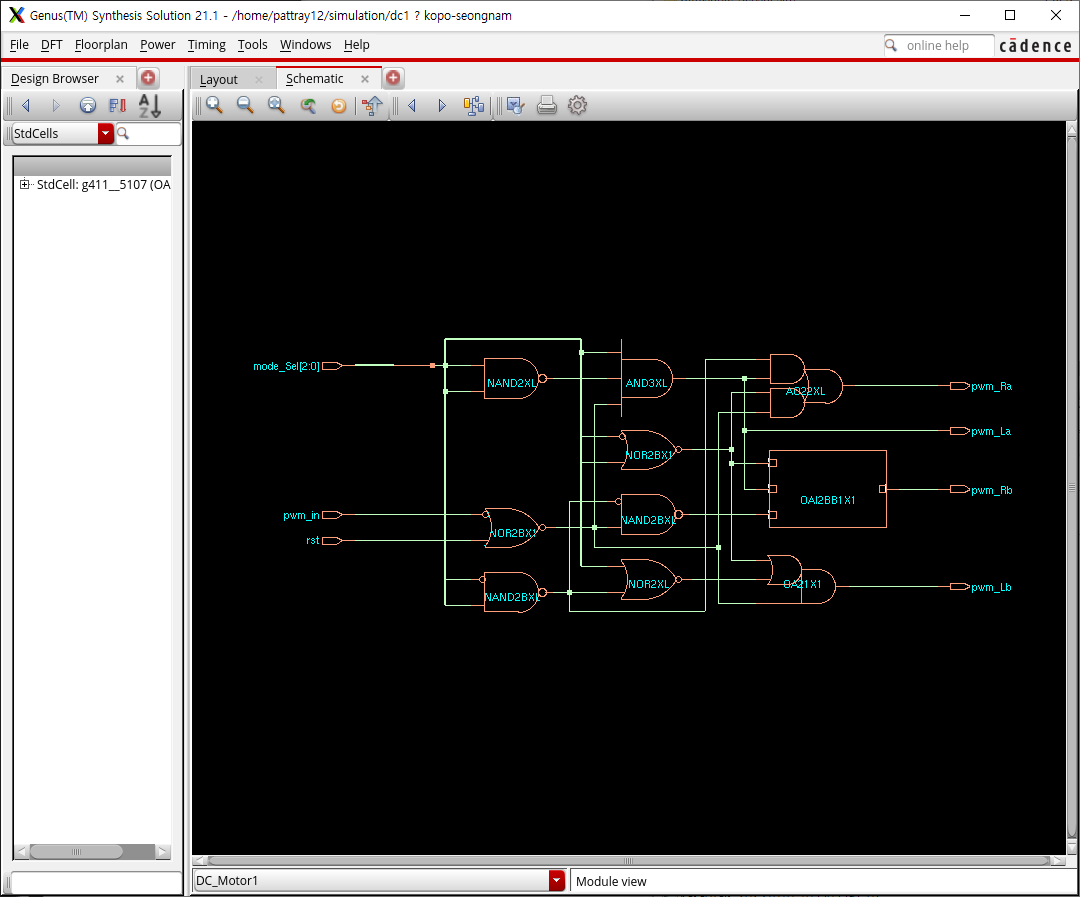

▶ Synthesis

- 교육용으로 제공된 cell library 사용

- Schematic

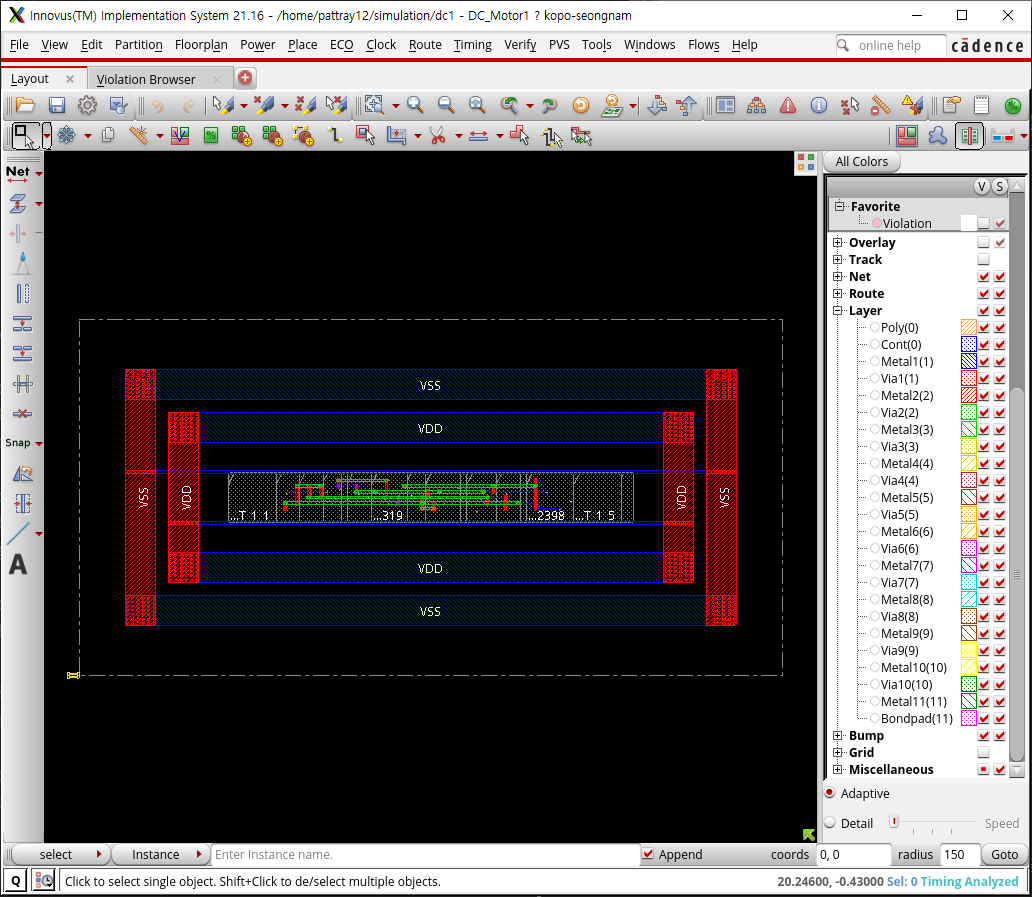

▶ PnR

- Layout

▋결론

- ㅇ

▋link

- Youtube:

- github: