Computer

CPU - memory - SSD

이런 식으로, CPU 연산에 필요한 데이터를 다양한 계층에 나누어 둔다.

Flash memory

- SSD에 쓰이는 대표적인 소자이고, 고밀도로 집적도를 높이는 것이 가능하지만 동작 속도가 매우 느리다.

- 정보 저장과 제어를 동시에 한다

DRAM

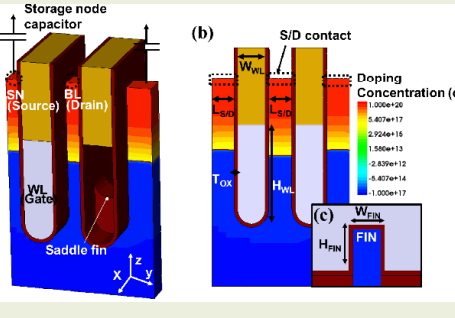

- 이름에서 알 수 있듯이 memory에 사용되며, 정보를 저장(Capacitor)하고 제어(Transistor)하는 부분이 따로 있다.

Logic Transisotr

Oncurrent를 높여서 잘 켜지도록 하는 것이 중요

: on current가 대략 1mA가 되는게 목표인데 현재까지는 불가능

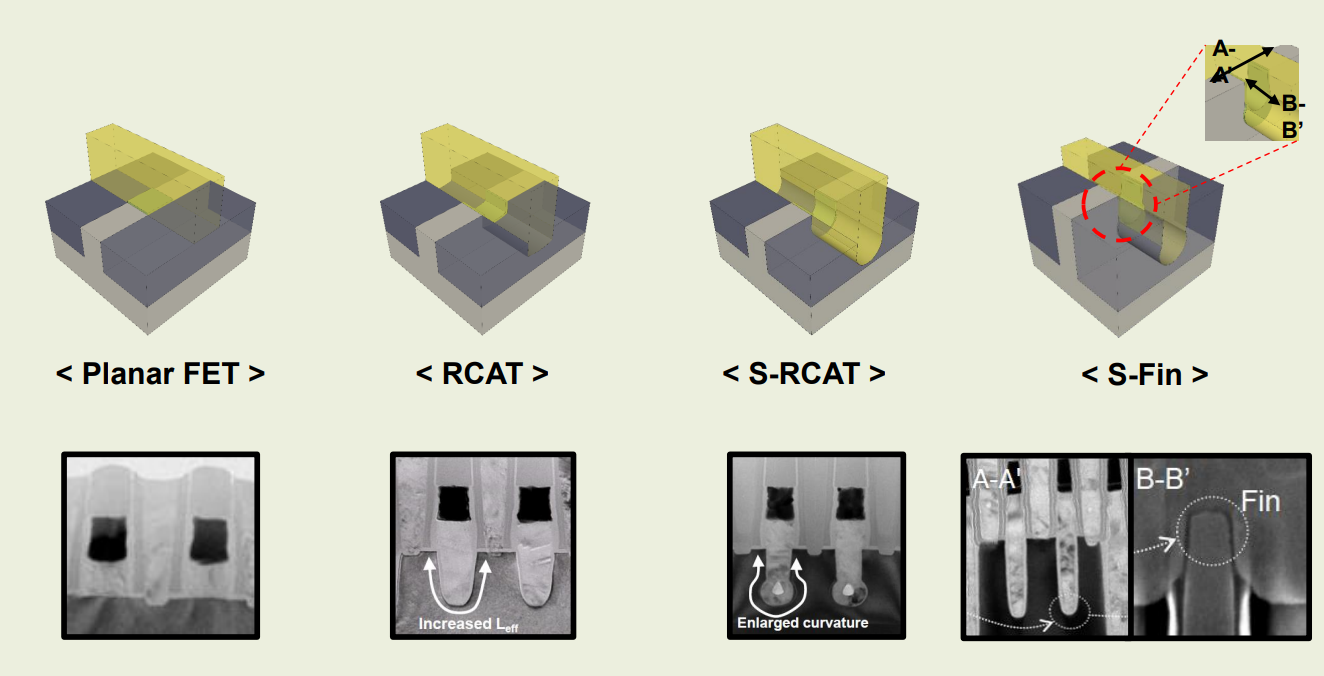

가장 기본적인 형태인 Planar FET에서 channel의 width를 늘려서 oncurrent를 늘리는 방향으로 바꾼 것이 FinFET

하나의 게이트로 여러개의 cell을 컨트롤 하는 것을 볼 수 있다. 이러한 FinFET을 여러개 배치한 Multi-FinFET이 있고, 이제 FinFET에서 측벽을 아예 감싸버려서 네면을 모두 사용할 수 있게해서 단면적을 넓힌 구조가 Nanosheet

DRAM Cell Transistor

Off current 줄여서 정보를 잘 저장하는 것이 목적

전하가 지나가는 통로, 즉 channel의 l을 늘리면 좋겠지만 집적도를 위해서 위에서 보았을 때 l의 길이는 같아 보여야 한다. 따라서 RCAT과 같이 아래로 파서 우회적으로 l을 늘려준다. S-RCAT은 더 둥글게 파고, S-Fin의 경우에는 w도 같이 증가시켜서 l의 증가로 감소한 on current를 어느정도 회복하는 효과를 준다.

Dielectric Thin Film technology for DRAM

DRAM을 위해서는 Capacitor가 큰게 좋음 대략 um의 단위

Cell capacitor는 육각벌집 모양으로 배치하는 게 좋은데, 이 구조가 가장 셀 간의 간섭도 적고, 공간 활용도도 좋으면 access time이 짧다.

Dielectric Thin Film technology for Flash memory

2D Plana Devices

여기서는 평면으로 Transistor들을 쭉 늘어놓는데 어느순간부터 이 간격을 줄이는게 한계에 다다름 그래서 구조적인 혁신이 필요했고,

3D Vertical Device에 대한 고려

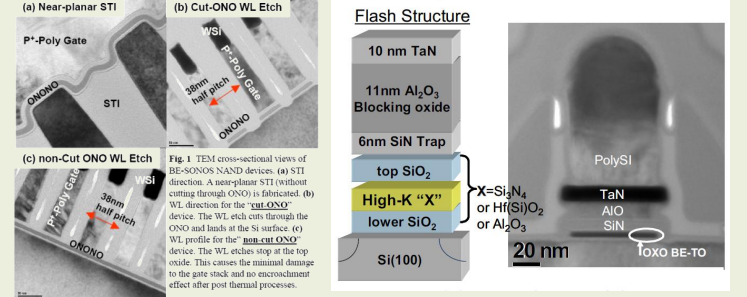

Charge trap memory

도체가 아닌 부도체 SiN에 전하를 가두는 방법. TaN으로 된 게이트가 Al2O3를 조절해서 SiN에 전하를 저장함

Random access memories

: Random access라는 말은 말그대로, 임의의 셀에 접근하여 읽고 쓰기가 가능하다는 뜻

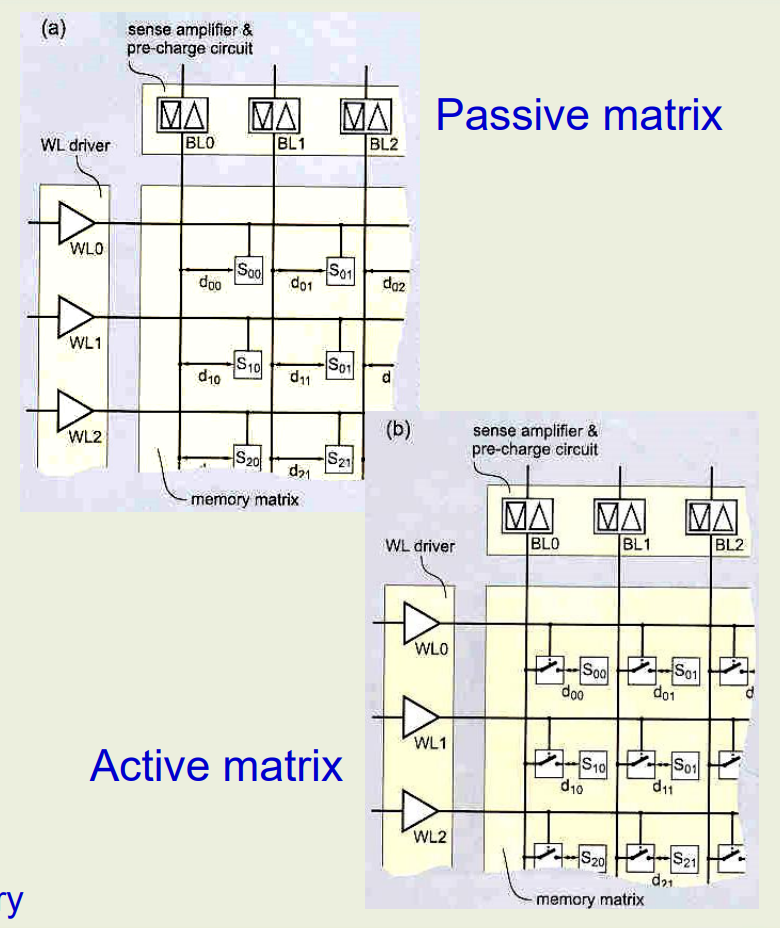

Passive matrix vs Active matrix

- Passive matrix

얘는 그냥 Bl과 WL이 동시에 켜지면 해당하는 선이 교차하는 셀이 켜진다 - Active matrix

얘는 BL(신호)가 들어오고, WL이 Transistor를 켜줘야 BL이 셀에 전달된다.

셀과 BL사이에 스위치가 존재해서 이걸 Active라고 부름 (스위치가 active하다)

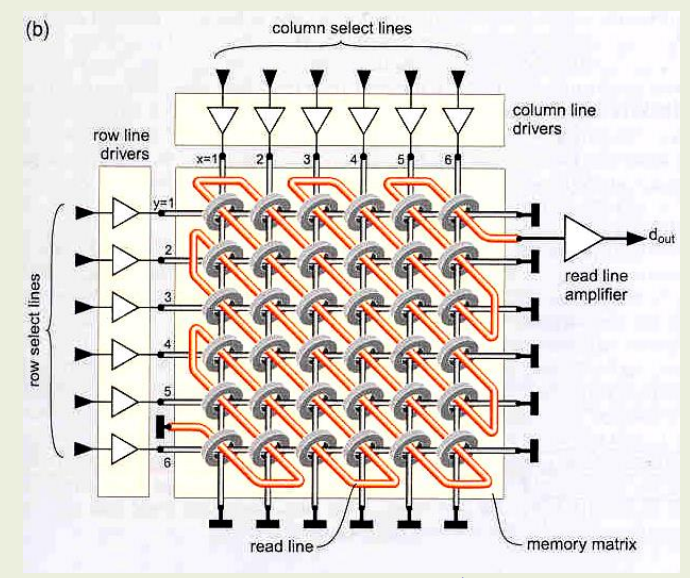

Magnetic core memory: 1세대

맨처음 모든 column & row select line에 대해서 오른쪽, 아래 방향으로 전류를 흘러서 고리 자석을 같은 방향으로 자화시킨다.

row와 column 동시에 반대 방향으로 전류를 흘러주면 1을 쓸 수 있게 됨

이때 row만 혹은 column만 선택된 자석에 대해서는 자석을 통과하는 두개의 전선 중에서 하나의 전선에만 전류가 흐르기 때문에 critical 전류 합을 못 넘어서 방향이 바뀌지 않는다.

저장된 정보를 읽을때는 맨처음(오른쪽, 아래) 방향으로 전류를 흘려보내고 만약 이때 자석의 자화 방향이 반대였다면 주황색 선에 유도 전류가 흐르게될 것이고 이를 감지하여 1이 써졌구나를 판별하면 된다. 그런데 이때 !!! 1이 써져있는 거지만읽는 과정에서 0으로 바뀌면서 파괴적 읽기를 수행하게 된다. 따라서 읽고 나서 다시 wirte back을 하는 과정이 필요하며, 이는 DRAM에서도 매우 중요한 요소다.

(그런데 사실 DRAM에서는 읽는 동시에 write back이 되도록 설계했기 때문에 큰 문제는 아님)

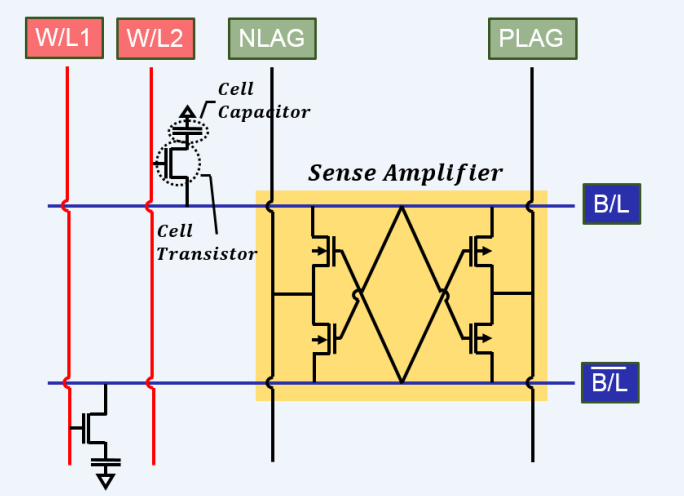

DRAM: Typcial active matrix based memory

DRAM에서도 각 셀들이 BL에서 들어오는 신호를 W/L이 조절하는 트랜지스터에 의해 전달 받는다. B/L과 B/L바를 비교해서 읽었을 때 reference line인 B/L_Bar와 B/L을 비교해서 전압이 얼마나 바뀌었는지를 관찰한다.

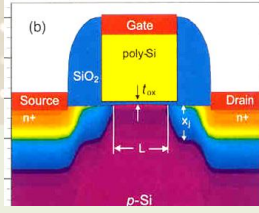

MISFETS(Metal-Insulator-Semiconductor-FET)

대부분의 메모리에서는 NPN 트랜지스터를 사용한다. Majority carrier인 전자가 이동속도가 더 빠르기 때문

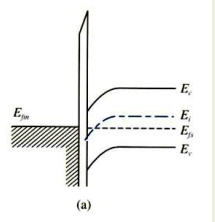

이 그림에서는 NPN 트랜지스터가 어떻게 켜지고 꺼지는지를 볼 수 있다.

(b)

일단 여기서 봐야할 것은

E - Fermi level

: 개념적으로 전자가 50퍼센트 차있는 에너지 준위라는 표현을 쓰던데 전공자의 말(?)에 의하면 전자들의 평균 에너지라고 생각하면 된다고 한다.

Ei - intrinsic Fermi Level

: 불순물 없는 진성 반도체의 Fermi Level

이 경우는 양공과 전자가 딱 절반이기 때문에 Ec와 Ev사이에 위치하게 된다.

(양공은 Ev에, 자유 전자는 Ec에 위치한다.)

이러한 개념들로부터 P타입의 경우 양공이 더 많기 때문에 Fermi level이 Ei보다 낮고 (Ev에 가깝다), N타입의 경우 전자가 더 많기 때문에 Ei보다 높다. 따라서 (b)처럼 E밴드가 굽어진다고 생각하면 된다.

어쨌든 전류는 S->D으로 가야하는데, 보면 potential이 P에서 더 높기 때문에 전류가 가기 어렵다. 따라서 (c) 에서처럼 P에 양의 전압을 가해서 포텐셜을 아래로 눌러주면 n+에서 P쪽으로 전자가 이동하기 수월해진다. 이때의 경우 s->D, d->s의 확률이 동일하기 때문에 net current는 0이다.

(d)

여기서는 Drain 쪽에 양의 전압을 가해줘서 전자의 potential을 아래로 더 눌러주게 되고 source에서 drain 쪽으로 오는 전자의 양이 더 많을 것이기 때문에 net current가 발생하게 된다.

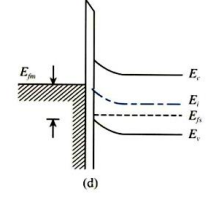

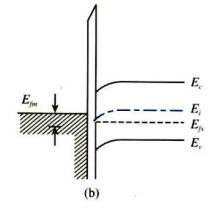

Flat band

여기서보면 이상한게 양쪽의 Ef의 위치가 다르다. 이는 인위적으로 전압을 주고 있다는 뜻. 왼쪽의 gate는 metal로 이루어진 물질이기 때문에 Ef까지 전자가 모두 차있는 것이며 semiconductor에서 Efs를 기준전압 (=0)으로 본다면 Efm이 더 높다. 이 말은 전자가 더 많이 있다는 뜻이고, 음의 전압을 가했다는 뜻이다. (Gate에)

Accumulation

이제 (c)에서 gate에 더 큰 음의 전압을 가해주면 Efs에 비해 Efm이 더 위로 올라가게 되고, 반도체 쪽의 hole들이 gate insulator 쪽으로 끌려온다. 따라서 Energy band가 저렇게 휘게 됨

P타입 반도체에서 보는 단면이기 때문에 majority carrier인 hole이 계면에 축적된다는 표현을 사용한다.

더 잘꺼진 상태

Depletion

(c)에서 Gate에 양의 전압을 주었다고 생각해보자

그렇다면 Efm이 Efs 쪽으로 내려오게 된다. (전자 뺏김)

반도체 쪽에서 보면 Ei 여전히 Ef 위에 있지만(P타입) 더 가까워졌고 (= less P타입, 즉 hole이 줄어들었다.)

strong inversion

조금 더 큰 양의 전압을 준다면 Ef보다 Ei가 더 내려옴, 즉 n타입이 됨 inversion이 되었고, Transistor On

여기서 strong의 기준은 Ec의 밴드가 Ei-Ef의 두배일 때

무슨 말이냐, 충분한 전자가 P타입에 모였다는 뜻이라서 전류가 흐를 수 있게 됨 ! (S->D가 연결되는 것)

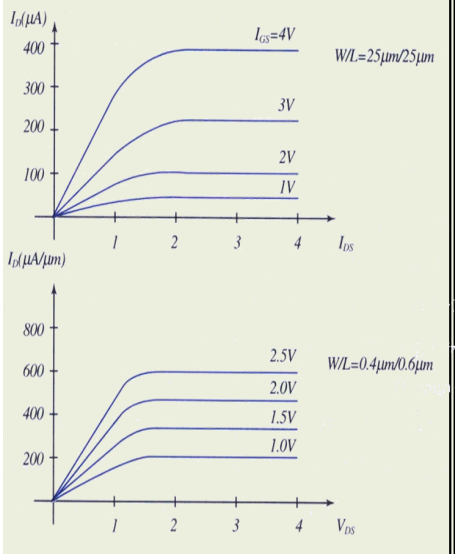

I가 아니라 VDS인데 이게 무슨 말이냐면 같은 VDS에서 게이트에 큰 전압이 걸릴수록 더 많은 전류가 흐른다는 것이고, 어느순간 전류가 Saturation되는데 그 이유는 Drain 쪽에 양의 전압이 가해져서 공핍층이 점점 확장되다가 channel을 끊은 pinch-off 현상이 발생함 그러면 전하 증가량이 감소하게 됨

이때 채널이 많이 잠식돼서 채널 길이가 많이 짧아졌을 때, PN정션에 걸린 역방향에 의해 전류가 흐르게 되고 이값이 포화함

그리고 위에서 아래로 가는 걸 보면 W랑 L 모두 줄었는데 오히려 Vgs= 2V이고 Vds = 3v일 때를 보면 W/L = 4/6일 때가 전류가 더 많이 흐른다. 이에 의해서 W를 바꾸는 것보다 S-D 사이의 거리를 바꾸는 것이 전류 증감에 더 큰 영향을 준다는 사실을 알 수 있다.

전류는 l에 의해서는 지수함수적으로 비례하는 성질을 가지고 있다.

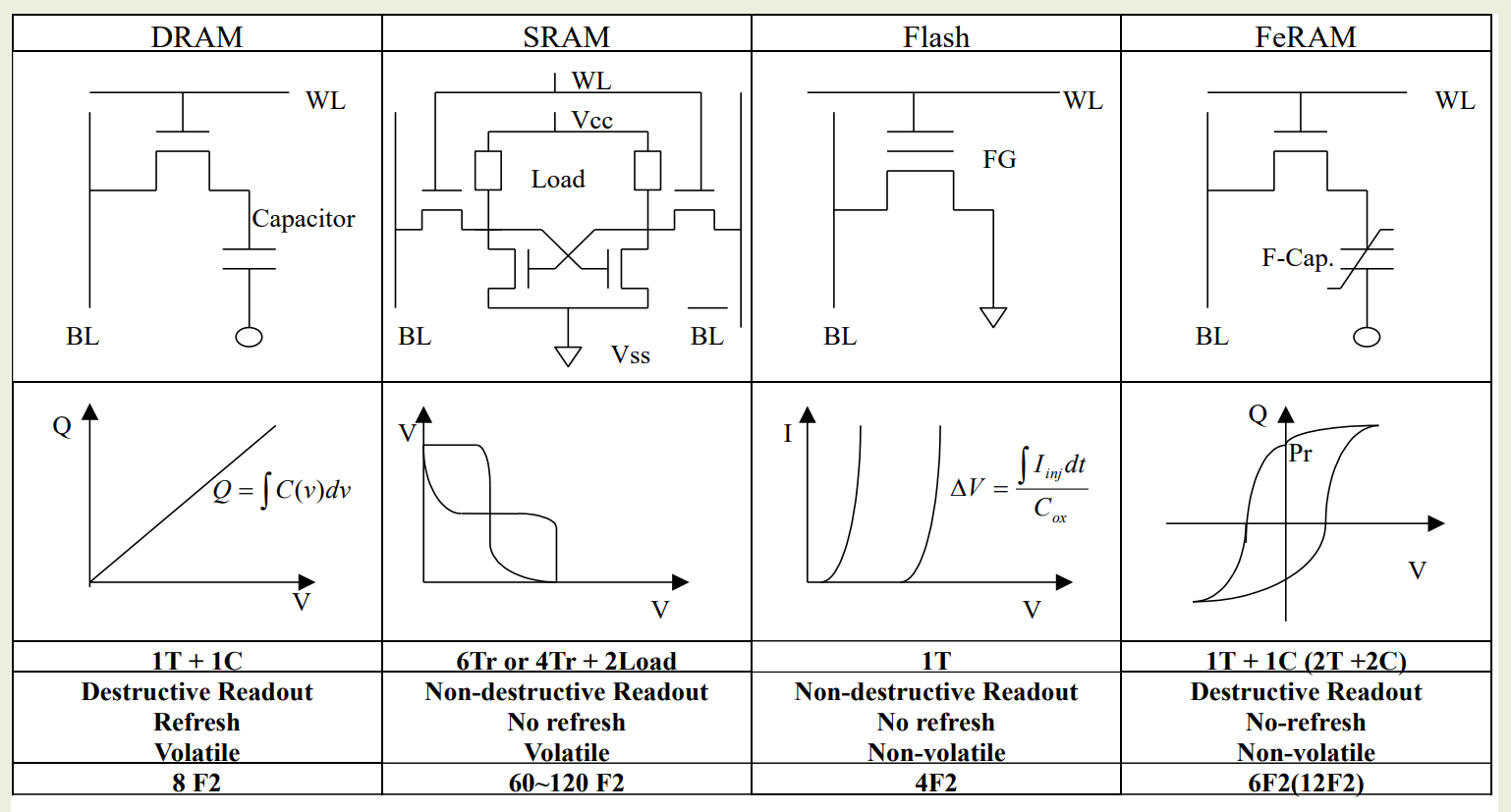

다양한 메모리들

DRAM - 1T + 1C

SRAM - 6T -> 집적도가 떨어진다

Flash - 전하가 있냐 없느냐에 따라서 신호 전달 여부를 결정함

FeRAM - DRAM의 Capacitor에 들어가는 절연체에 특별한 물질을 사용해서 전압을 제거해도 남아 있을 수 있는 Non-volatile임

Flash 매우 느림

DRAM의 Retention time 짧음 -> 계속 rewrite 해줘야

Flash -> 전압을 제거하면 다날아가는데 전압만 있다면 retention안해줘도 됨

Function of DRAM capacitor

Gate 열었을 때, capacitor의 전하가 빠져나오거나 들어오거나해서 Bit=line에 변동폭을 줘야함

그런데 상온에서 전하가 가지고 있는 열 E가 25mV이기 때문에 안정적으로 차이를 감지하기 위해서 최소 100mV의 변동폭을 주어야함

DRAM structures

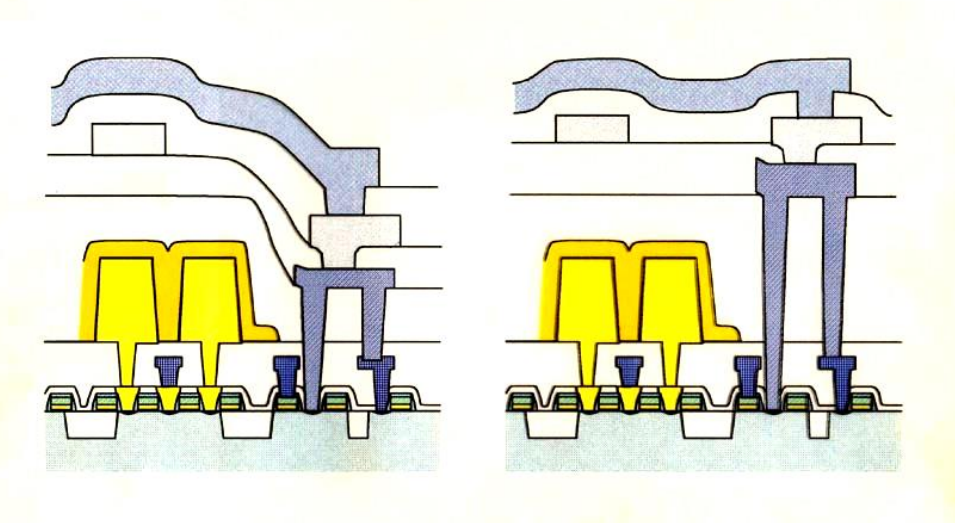

capacitor를 위에 만드느냐 VS 아래 만드냐인데

Trench capacitor의 경우, 아래에 캐패시터 만들고 위에 Tr넣는 과정에서 Source Drain 도핑을 위해 고온을 가해야하는데 이러면 캐패시터가 열에 망가짐 . 열에 강한 캐패시터를 써야하는데 그러면 유전율이 작은 물질이고 Capacitance가 작아짐

DRAM cell structure

왼쪽의 경우 높이가 달라서, 포토공정을 할 때 초점 맞추기가 어렵다

오른쪽은 높이를 맞춰서 포토 공정이 쉬운데, 대신 저렇게 높이를 맞추기 위한 증착과 에칭 공정이 어려워진다.

이러한 구조에서 B/L과 B/L_bar의 경우 두 전선 사이에 insulator가 있으니까 일종의 캐패시터로 볼 수 있다. 그리고 뒤에서 얘기하자면 이 두개의 캐패시턴스를 같게 만드는게 어렵다.

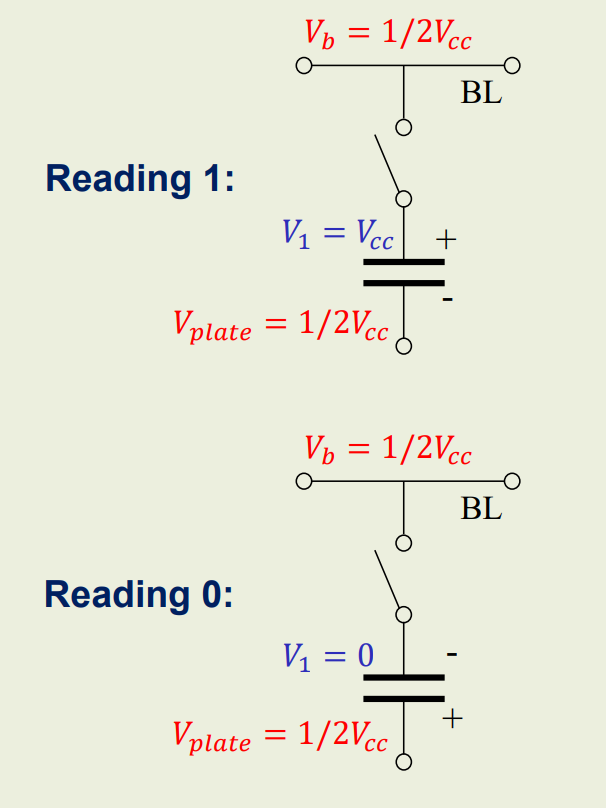

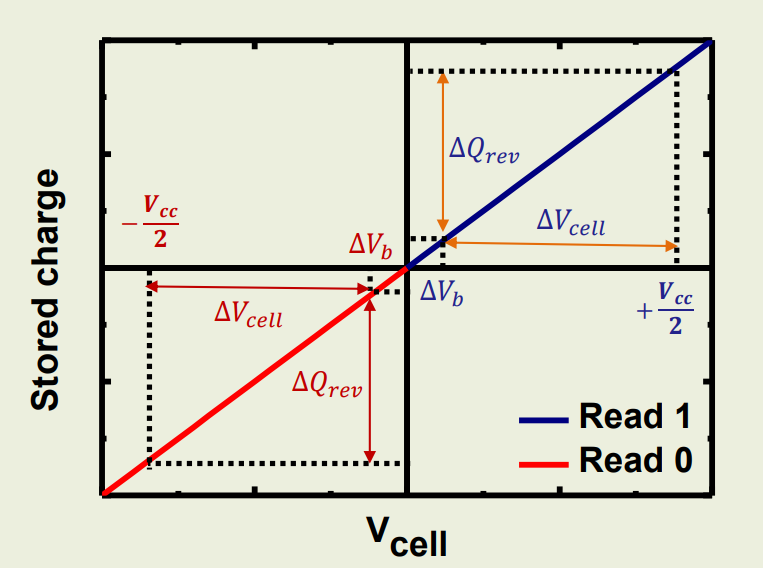

Charge sharing

Read를 할 때는 Vb = 1/2Vcc를 가해준다. 그러면 이때 Vb가 변하는 정도를 감지하게 되는데 이때 전압의 변화폭이 100mV는 되어야 한다.

여기서 보면 Capacitor에 저장된 전하를 전부 뱉어내지는 않고, 뱉어내더라도 최소 델타Vb의 charge는 남아 있는 것을 확인할 수 있다.

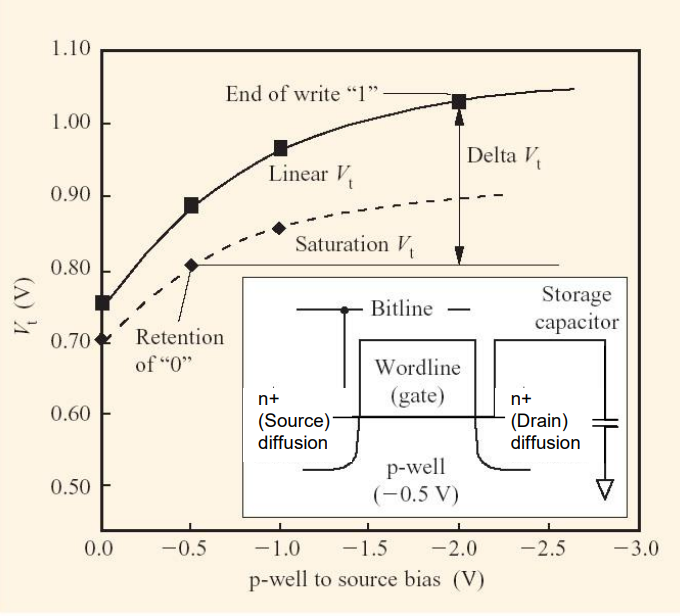

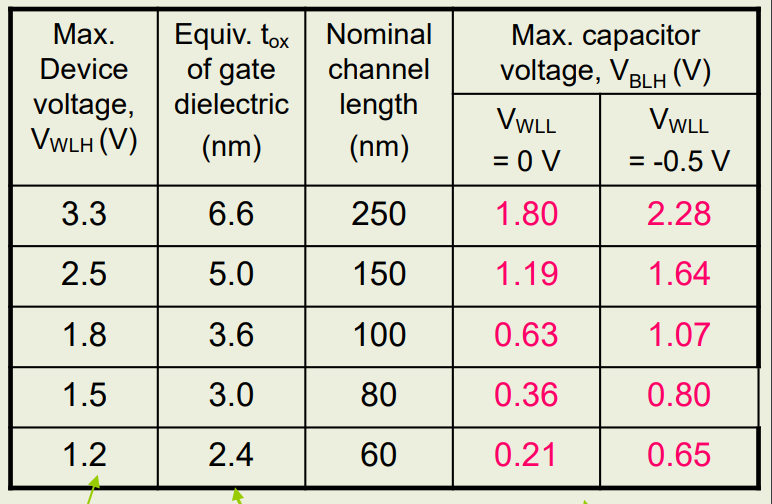

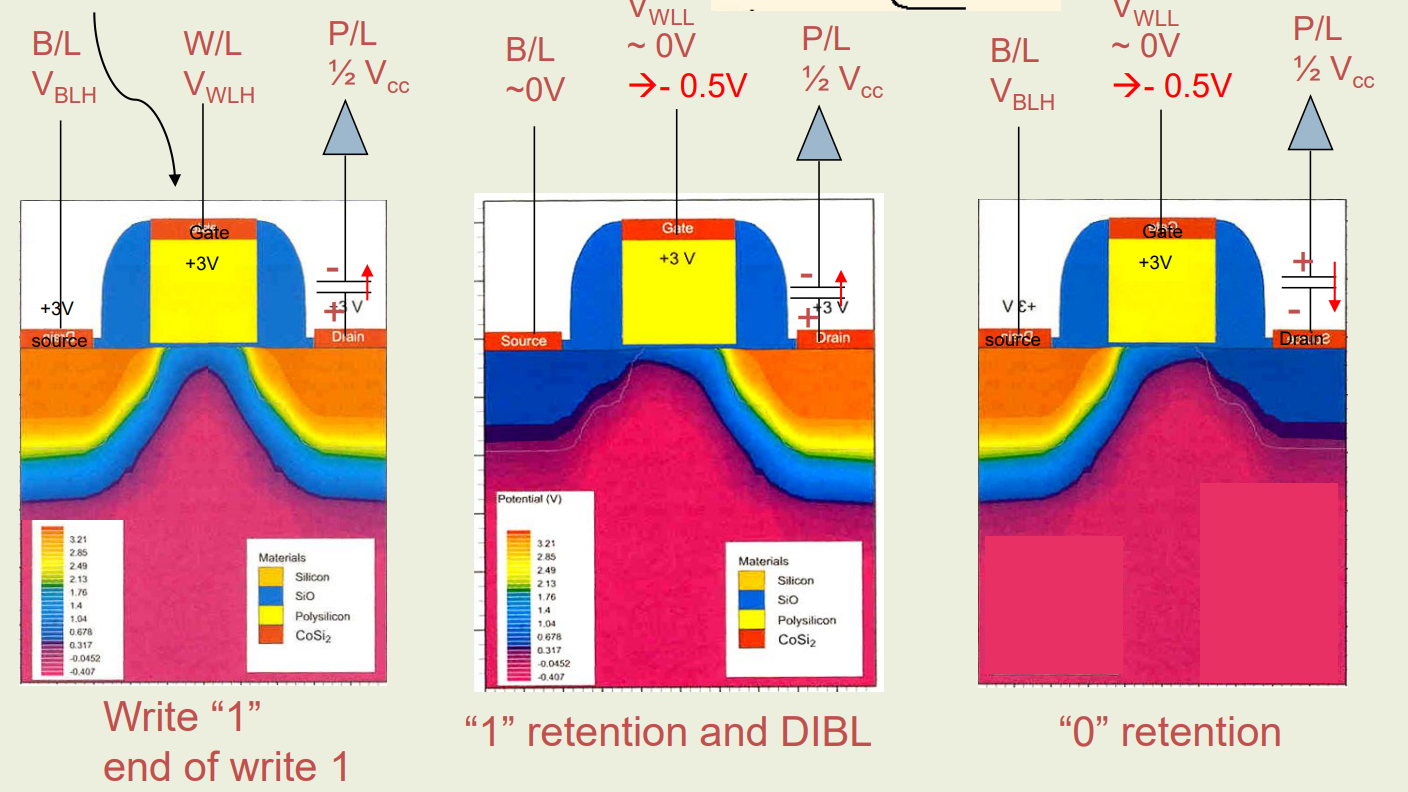

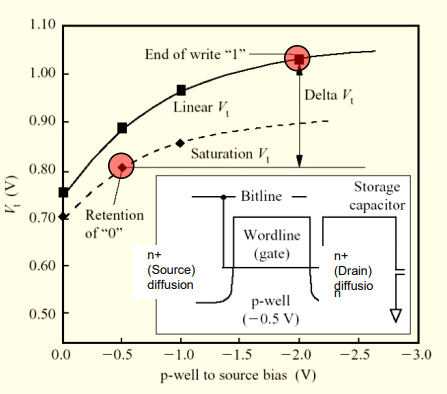

Scaling challenges for the DRAM TR: Voaltge scaling

트랜지스터의 기본 동작 원리는 Gate에 DS전압보다 높은 전압을 인가해주는 것이다. 양의 전압이 가해지면 전자가 Gate쪽으로 몰리면서 채널을 형성하게 되고 이 채널을 통해 전류가 흐르게 되는 것! 그런데 D나 S쪽에 양의 전압이 있다면 전자들이 자꾸 그쪽으로 끌려가기 때문에 더 큰 전압을 Gate에 인가해주어야 한다.

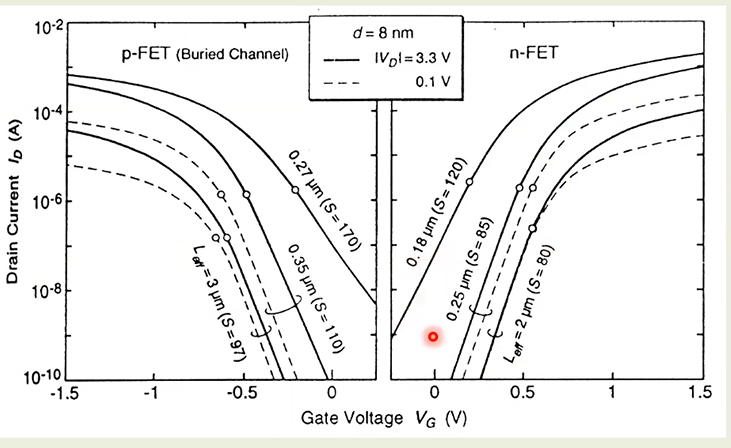

따라서 그래프를 보면 1이 써져있는 경우, 즉 Drain에 양의 전압이 있는 경우(실선)이 0이 써져있는 경우 (점선)보다 Vt가 크다. 또한 p-well to source bias가 body bias가 -0.5이기 때문에, Vs가 점점 증가할수록 Vt 또한 증가하는 것을 알 수 있다.

0이 써져 있는 경우에, Vb = 0이 들어올 때가 어떻게 보면 Vt가 가장 작아서 0을 지키기가 취약하고, 오히려 Vb가 커지면 Vt 또한 커져서 0을 지키기 쉽다.

1이 적혀있을 때를 보면 1을 rewrite해주어야 하는데, Vt가 너무 커서 쉽지 않다. 따라서 Vt를 무작정 크게하는 것은 좋지 않다.

또한 SS(Subthreshol Swing: Drain current를 10배 증가시키기 위한 Gate 전압)의 개념을 통해서 우리는 On/ Off current의 비를 10^8배 유지하고 싶기 때문에 On/ Off시 Gate 전압이 최소 800mV 차이나야한다는 것을 알 수 있다. (100mV당 10배 차이가 난다)

그런데 표를 보면, VWLH에 3.3V를 주었는데 Capacitor에는 겨우 1.8V의 전압이 걸리는 것을 확인할 수 있다. (VWLL = 0인 경우)

이는 Gate전압에 Vt보다 대략 0.7V의 전압을 더 주어야 Transistor가 충분히 켜져서, 우리가 의도한 대로 한정된 시간 안에 충분한 양의 전류가 흐를 수 있게 되는데, 이러한 Vt + Vover voltage가 S->D 쪽으로 갈 때 potential barrier를 형성하기 때문에 VWLH에 가해진 3.3V가 온전히 Drain 쪽으로 전해지지 못하고, 1.5V 깎인 1.8V만 전해지는 것

그런데 만약에 VWLL = -0.5V를 준다면 Vt를 0.3으로 줄 수 있음 따라서 Vt+ Vover voltage가 1.0v로 줄어들고 3.3V를 주었을 때, 대략 2.3V 정도까지는 전달되는 것을 알 수 있다.

그리고 VWLH와 tox(Gate oxide 두께) 사이에 어느정도 비례관계가 있는데, 이는 gate insulator에는 5MV/cm까지만의 전압을 가해줘야 SiO2의 기능이 망가지지 않기 때문이다. Channel length또한 tox의 대략 30배 정도인 걸 알 수 있는데, 따라서 Scale 적인 측면에서 Channel length를 줄이려면 tox를 줄여야하고 VWLH 또한 줄여야하는 것을 알 수 있다.

그런데 동작 전압을 줄이면 DelV까지도 줄어들기 때문에 또 결국엔 Cb를 줄이는 것이 이 모든 것의 핵심 포인트 !

근데 거의 불가능함,,,그래서 Cc라도 늘리자 이렇게 가지만 Cc를 늘리려면 캐패시터의 면적을 넓혀야해서 또 스케일의 반대로 가게 됨 ㅎ

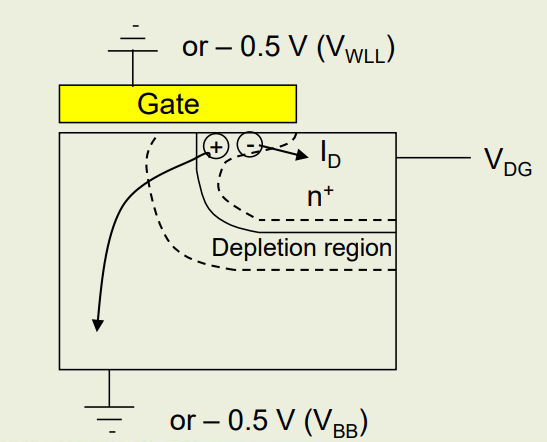

Body bias

VWLL = -0.5V를 주면 Vt를 낮출 수 있게 된다. 게이트가 꺼져있을 때 음의 전압을 주면 전자들을 밀어내서 전류가 흐르는 것을 막아주기 때문임 !

그런데 여기 말고도 P-well 그 자체에 -0.5V 전압을 줄 수도 있다. 이렇게 되면 우주선에 의해 긴 BL에 있던 전자들이 교란되고, 교란된 전자들이 Gate가 꺼져있을 때 source에서 drain으로 이동하려고 할 때가 있는데 그럴 때 p-well의 음의 전압이 potential barrier를 높여줘서 그걸 막아줌

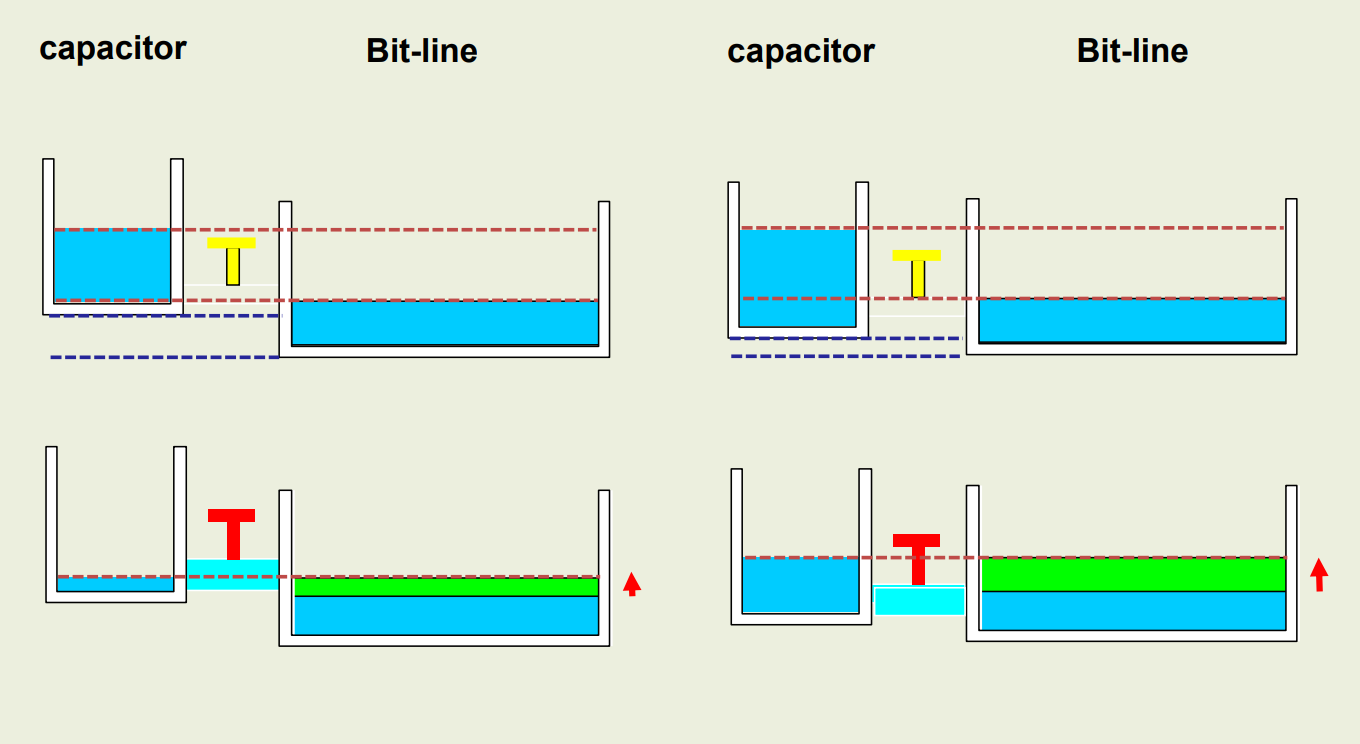

Function of DRAM capacitor

왼쪽에서 보면 capacitor에서 B/L으로 전류가 흘러나올 때, 관의 높이가 너무 높아서 (Vt + Vover) 어쩌면 충분히 더 내려갈 수 있는데 더 내려가지 못했다.

그런데 오른쪽처럼 VWLL에 음의 전압을 가해서 Vt를 낮게 만들어주면 관의 위치가 아래로 내려오게 되고, 같은 양의 전하로도 delV를 키울 수 있게 된다.

따라서 Vt는 줄일 수 있으면 좋다,, 그리고 줄여서 나타나는 문제는 음의 전압을 인가함으로써 방지

NPN Transistor

그림처럼 원래는 N+ p N+ (강하게 도핑) 이런식으로 되어 있어서 아래에는 전류가 흐르지 않음

따라서 Gate에 양의 전압을 주면 저렇게 전자들이 모여서 채널이 형성되고 흐를 수 있게 되는 것임

Voltage Scaling

여기서 보면 1이 써져있을 때 BL에 1이들어오는 경우의 Vt가 최대다.

따라서 1V(Vt) + 0.3V (over voltage) + 0.2V(Vt의 공정상 편차) ~1.5V 가 되기 때문에 대략적으로 VWLH - VBLH = 1.5V라고 생각하면 되겠다.

0이 적혀 있을 때 Vt가 작아서 0을 지키기 어렵고, 1이 적혀 있을 때, Vt가 너무 커서 적기 어려워지는 문제가 있고, 나머지 케이스에서는 문제 X

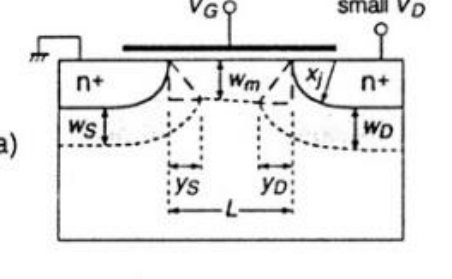

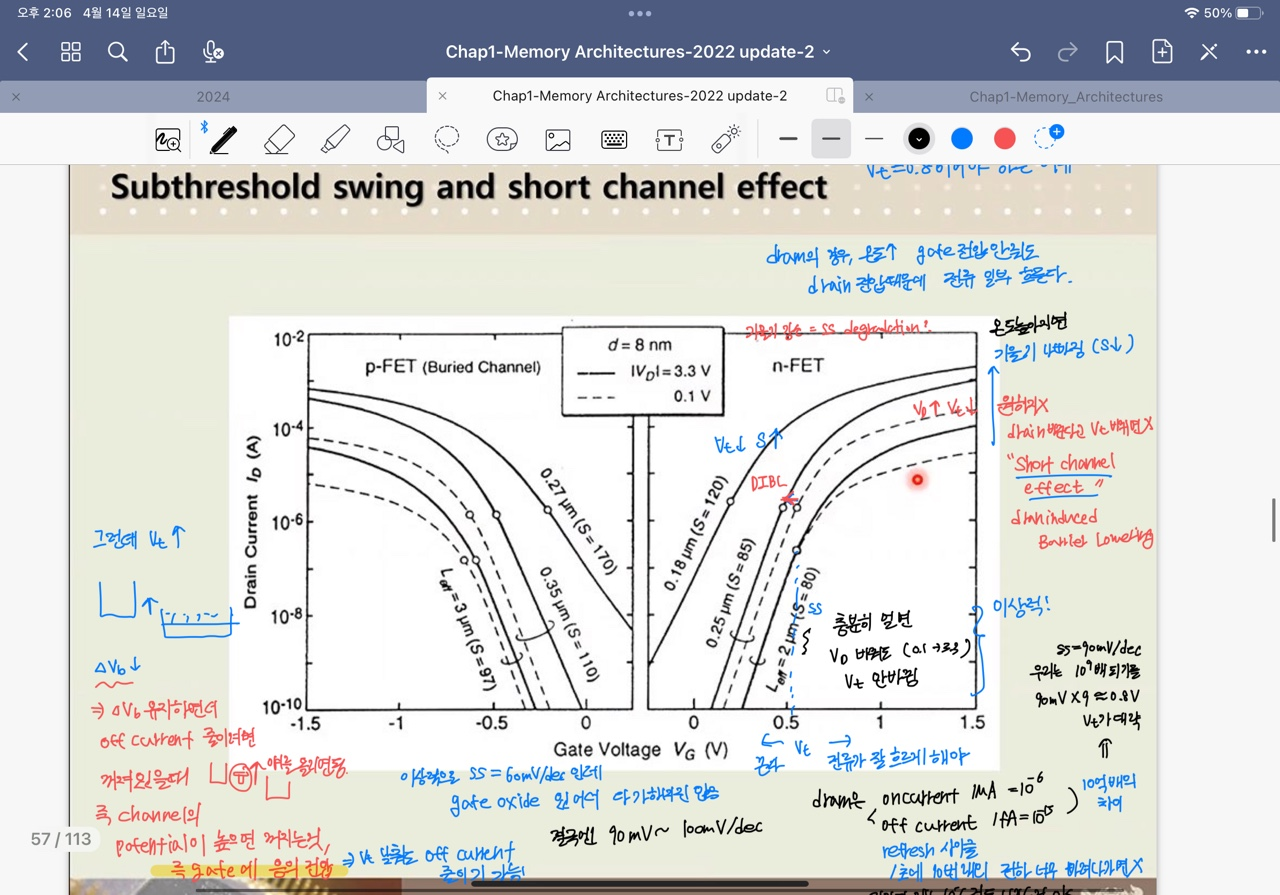

Subthreshold swing and short channel effect

Short channel Effect란

Channel length가 짧을 때 Vt가 감소하는 현상을 말한다.

Source와 Drain 사이가 좁아지면 Depletion 영역이 겹칠 수 있게 된다.

요론 상황! 이와중에 VD에 양의 전압까지 준다? 그러면 Depletion 영역이 확장됨 -> 따라서 Vt가 감소하는 영향을 줌(왜냐 Gate가 더 꺼지기 어렵다는 뜻이 잖슴)

그래서 Drain voltage에 의해 Barrier가 감소하는 효과이기 때문에 DIBL이라고 부른다.

그런데 저런식으로 왜 Gate 밑에서 Drain Source 영역이 겹쳐지냐! 이렇게 묻는다면

Gate를 먼저 만든다음에, Self align을 통해 S, D의 위치를 게이트에 맞추는 것임... 불순물을 주입하고 에너지가 높아져서 격자가 망가진다. 따라서 재결정화하려고 열을 가해주는데 이때 게이트쪽으로 퍼지게 된다.

이게 무슨말이냐면 우선 L이 충분히 클 때를 보자, 이떄는 short channel이 아니기 때문에 Drain 전압이 높아져서 Vt가 감소하거나 하지 않는다. 하지만 길이가 짧아지면 VD가 증가함에 따라서 Vt가 확 줄어들게 된다.

이 그림을 보면 일단 온도가 높아지면 Gate 전압을 안줘도 Drain 전압이 양이면 전류가 일부 흐르게 됨. 따라서 온도가 높아질때 SS는 값이 작아진다.

그림에서 같은 Channel length에서 VD가 증가할 때, VG가 감소하는 현상이 DIBL. channel length가 짧아질수록 S가 감소하는 것을 알 수 있다.

이상적으로는 ss가 60mV인데, 실제로는 Gate oxide에도 전압이 나눠 걸리기 때문에 10배만들려면 대략 90mV의 전압을 가해줘야하고, 10억배의 on/off current 비를 만들려면 90 * 9 = 0.8V의 전압을 Vt로 만들어준다 !

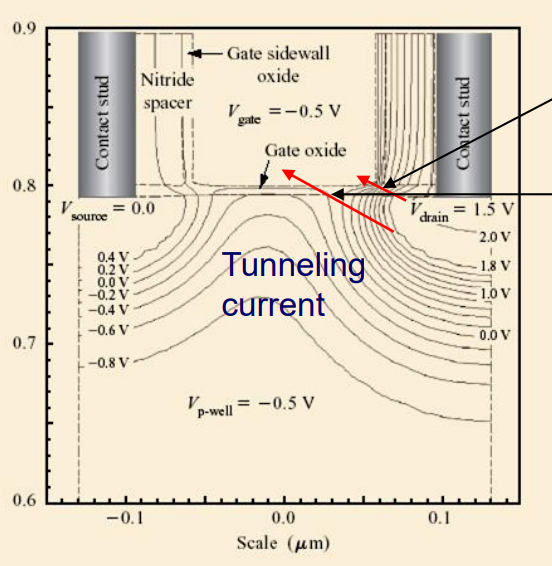

Scaling challenges for the DRAM TR: Leakage current

총 4가지의 Leakge component가 있다.

1. storage junction-to-well leakage

2. Array MOSFET GIDL (Gate induced drain leakage)

3. Tunneling current in gate insulator

4. Storage capacitor dielectric leakage

이 모든 종류를 합쳤을 때, 1fA/cell 이하가 되어야 한다. (logic MOSFET은 10^배 정도 더 큰 off current를 허용해줌, on current 늘리는게 더 중요해서)

이때 기본전제로 Gate Oxide의 두께는 얇아야 한다. (Gate 전압이 나눠걸리기 때문에, gate oxide의 C가 커야 channel 쪽에 전압이 많이 걸리게 되고, 두께를 얇게 해야함. 근데 그러면 leakage current가 증가하게 됨

따라서 logic에선 얇게 만들고, dram에서는 상대적으로 두껍게 만든다.

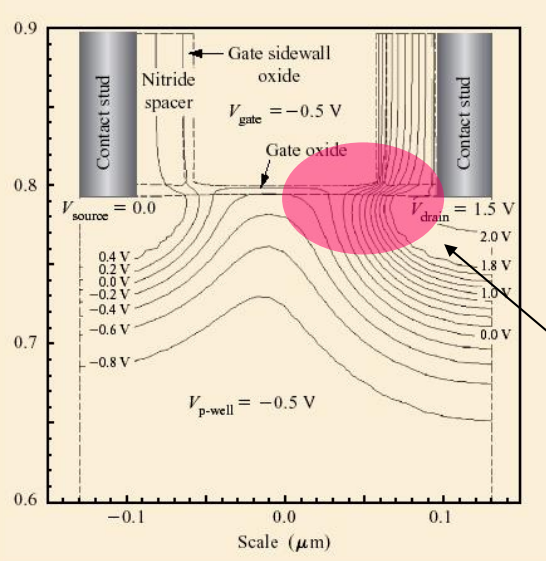

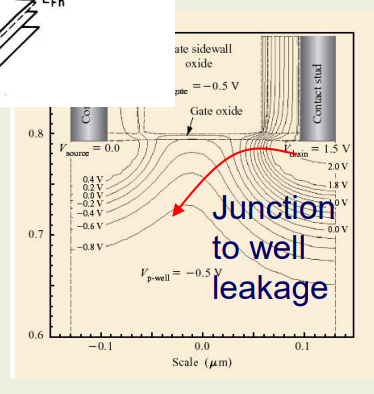

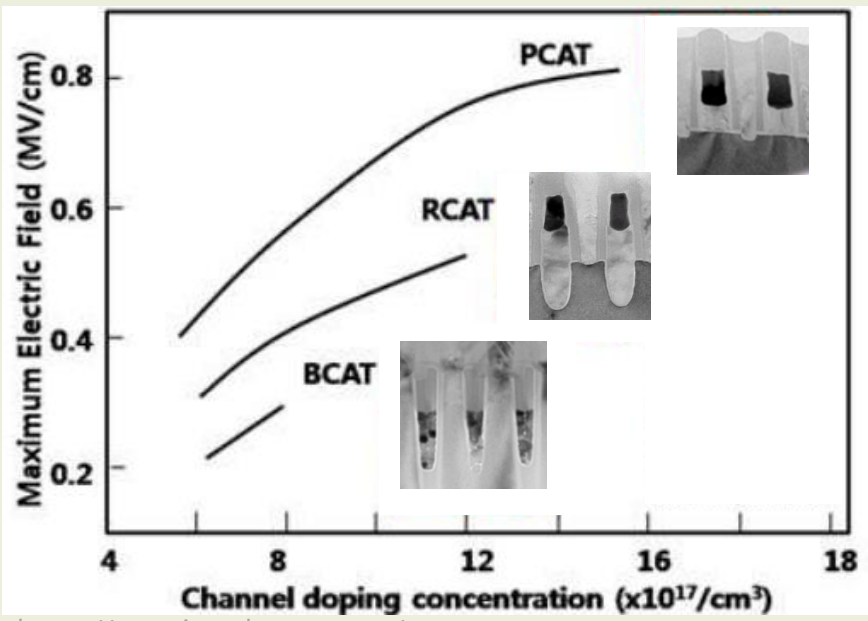

1. Junction to well Leakage

이런 식으로 p-well에는 -0.5V가 가해져있고, Drain 쪽에는 양의 전압이 가해져있기 때문에 전기장이 형성되어 있어서 전류가 새게 된다.

왜 저렇게 저기 등고선이 조밀하냐면, 좀전에 언급했던 short channel effect를 막기 위해서는 depletion 영역이 좁아져야하고 그러기 위해서는 P의 도핑 농도가 높아져야한다. 그러다보니 등고선이 촘촘해져서 전기장이 세지고 leakage가 증가하게 됨

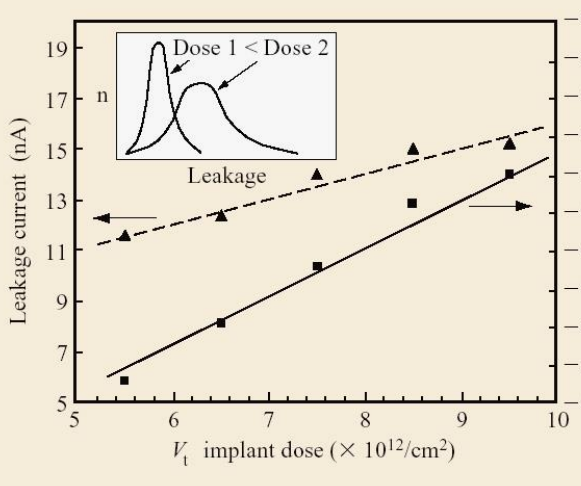

얘를 보면 알 수 있는게 도핑 농도가 높을수록 leakage가 증가하는 것을 확인할 수 있다.또한 도핑을 많이한다는 것은 반도체의 결함이 커진다는 뜻이고, 가지는 분포 또한 넓어지게 된다는 뜻.

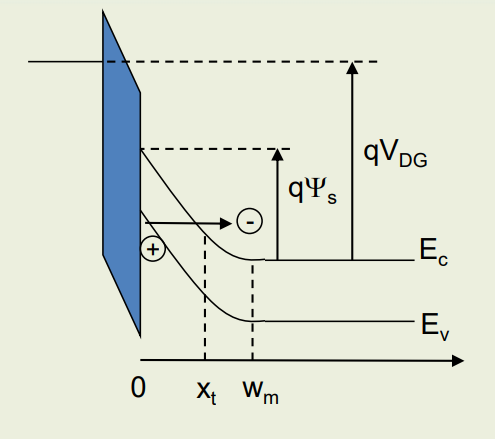

2. Gate induced Drain leakage current (GIDL)

DIBL은 Drain 전압이 높아지면 Barrier가 낮아지는 (Vt가 낮아지는)현상이고

GIDL은 Gate에 전압을 가해주면 Drain에서 전류가 새어나오는 현상을 의미한다.

우리가 Gate에 -0.5V 음의 전압을 준 상황을 생각해보자

그러면 요롷게 (파란색이 gate insulator임) 에너지 밴드를 살펴볼 수 있는데 Drain쪽에서 보면 게이트에 음의 전압이 가해졌으니 에너지 밴드가 저렇게 굽어지게 됨 (전자가 가기 어려워짐)

원래 Drain 쪽에 양의 전압이 있다는 건 Conduction 밴드에 있던 전자들을 다 빼놓은 상태인데 그림처럼 Band가 많이 구부려져서 Gate insulator쪽에서 보면 Ev가 Ec와 같은 높이가 되고, 이때 Tunneling이 발생해서 Ev에 있던 전자가 Ec로 넘어가게 된다. 그럼 electron + hole pair가 발생함

그러면 이그림에서 본것처럼 생긴 pair가 각각 하나는 p-well쪽으로, 전자는 Drain 쪽으로 이동하게 됨

->Gate에 음의 전압을 줌으로써 의도치 않은 Drain leakage current가 발생하게 되었다!!

근데 사실 문제는 안됨ㅋ

왜냐 Scaling을 진행하다보면 필연적으로 VD가 줄어서 GIDL을 덜 유발함

3. Tunneling current through the gate insulator

그럼 이제 Drain에서 직접적으로 gate로 빠져나가는 전류는 없냐!

당연히 있음ㅎㅋ

보면 빨간색 화살표쪽에서 매우 조밀한 영역이 있는데 여기가 전기장이 엄청 세다. 그래서 Gate oxide가 있어도 새어나갈 수도 있는데

GPOX라는 공정 때문에 이런 코너부분의 산화막이 매우 두꺼워짐 (공정을 할 때 1. gate oxide만들고 2. gate 만들고 3. s,d 도핑하고 4. 높은 온도에 구운다음 5. 산소에 일정시간 방치시키는데, 이때 추가적으로 저 코너부분의 산화가 발생해서 두꺼워짐)

따라서 tunneling이 발생해서 전자가 새어나갈 수 있는 통로부분의 산화막이 두껍고, 저 긴 빨간색 화살표 같은 경우에는 산화막이 얇아서 새어나갈 수 있지만 거리가 멀어져서 또 그렇게 문제가 되지는 않는다.

4. Storage capacitor dielectric leakage in addition to the MOSFET subthreshold off-leakage

당연히, 캐패시터에 전하를 저장해놓음 근데 이 Dielectric 층이 완전히 절연이 되지 않는다면 전류가 새겠지

누가 제일 문제냡

GIDL은 아까도 말했듯이 Vt도 있고, Vcc가 결과적으로 계속 낮아지고 있기 때문에 VD가 낮아져서 큰 문제 X

Gate oxide leakage 또한 산화막이 두꺼워서 괜찮음

Junction to well leakge 얘가 제일 문제다 !

short channel effect 막으려고

->Depletion 영역 좁히기 위해 P타입 도핑 많이 함

-> PN junction에 걸리는 전기장 증가함

-> junction to well leakge도 증가

도핑 농도가 증가할수록 전기장 또한 커지는 것을 확인할 수 있다.

그래서 누가 제일 좋게?

당연히 같은 도핑 농도에서 전기장 작은 BCAT, RCAT, PCAT 순으로 최신 제품

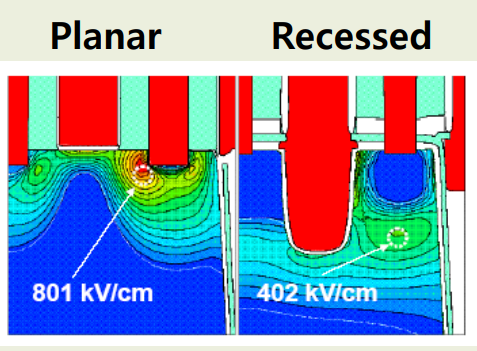

RCAT과 PCAT이 뭐가 다르냐면

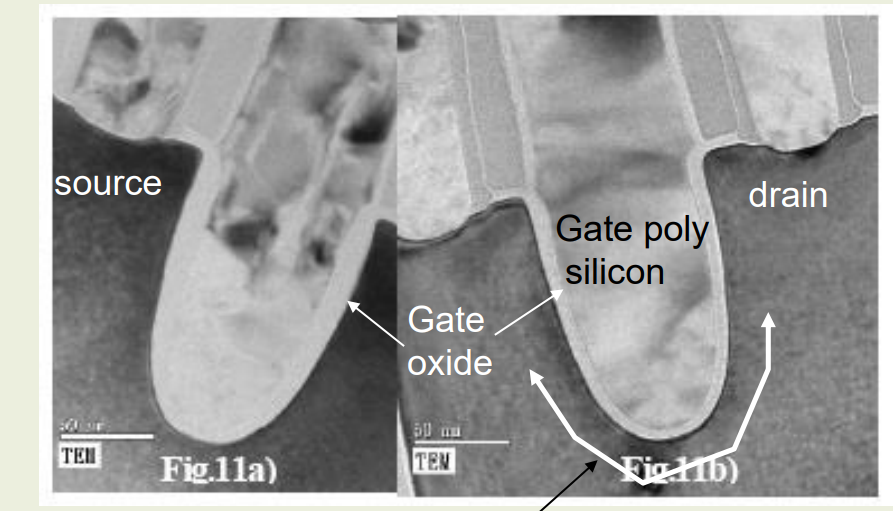

Planar에서 gate를 아래쪽으로 끌어내리면 RCAT이 되는데 보면 Source에서 Drain까지 가는 거리가 멀어졌다는 것을 알 수 있음 !

따라서 도핑을 많이 하지 않아도 괜찮아짐

-> 전기장 많ㄴ이 안크고 -> junction lkg 줄일 수 있음

BCAT은 Gate랑 Drain 접촉면적을 줄이기 위해 아래쪽은 Gate, 그 위는 insulator로 막아버린 구조

RCAT( Recessed Channel Array Transistor)

이제 보면은 drain과 금속이 닿아 있는데 이 사이의 contact저항을 줄이기 위해서는 Drain 쪽 도핑을 많이 해야함

n타입 도핑 농도 높이면 Short channel effect가 심해짐 (depletion 영역이 커짐)

그래서 PCAT 같은 경우에는 도핑 농도를 많이 못 높임 근데 RcAT은 도핑 농도 높여도 전기장이 많이 안커져서 short channel effect가 덜함

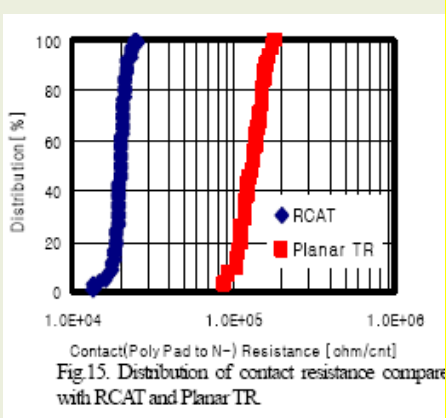

따라서 contact 저항은 도핑을 많이 할수있는 RCAT이 더 낮음

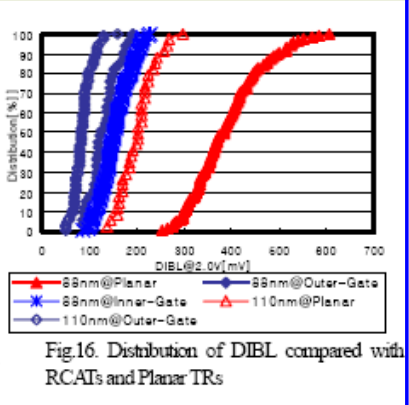

DIBL 같은 경우도 보면 short channel effect가 덜한 RCAT이 덜함

VD = 2v일 때, barrier가 얼마나 낮아지느냐를 나타낸 표이고 파란색이 RCAT 빨간색이 PCAT임

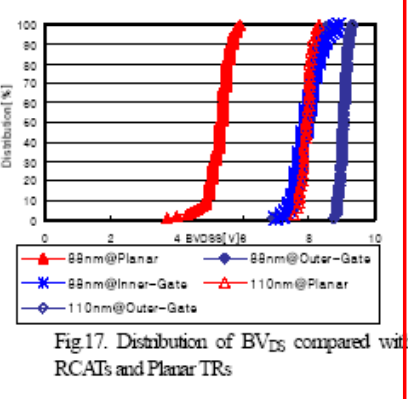

source와 Drain 사이의 breakdown voltage

같은 PCAT이어도 channel length 길 때가 높고, 이제 RCAT은 channel length가 짧아도 괜찮은 성능을 보인다고 할 수 있겠다.

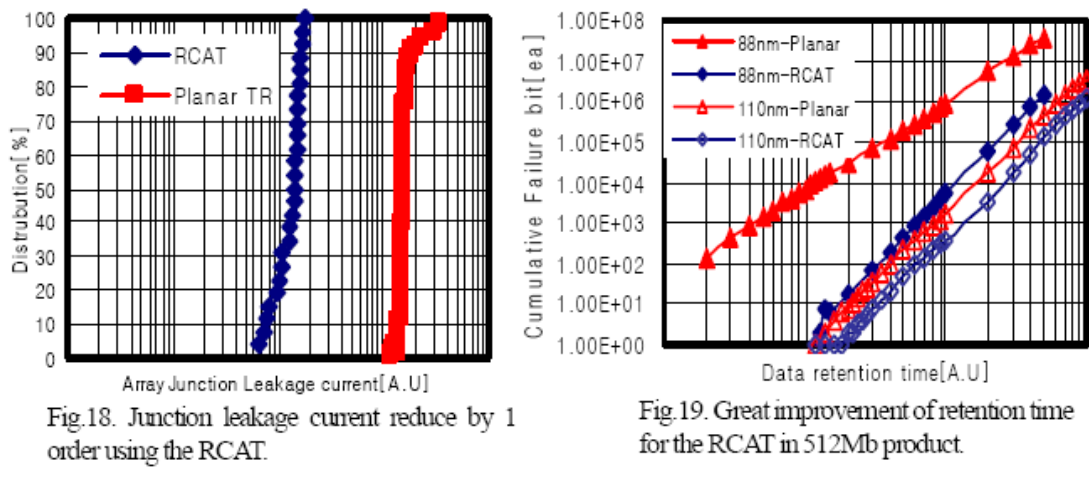

Merits of RCAT

보시면 Junction lkg도 적고, retention time 또한 주기를 늘렸을 때 failure가 낮아졌다는 것을 확인할 수 있다.

DRAM에서는 junction leakage current가 매우 중요하기 때문에 얘가 10배 향상되었다는 것은 아주 큰 장점 !!

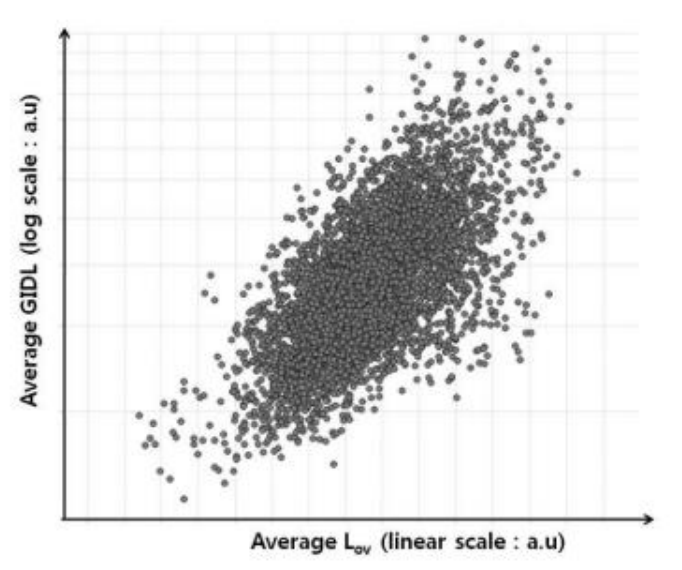

Merits of BCAT

아예 gate를 땅에 파묻어 버렸다고 볼 수 있는 BCAT (drain 과 접촉면 줄임)

->GIDL을 완전 해결해버림

GIDL이라는게 사실 Drain 쪽이 Gate에 음의 전압이 걸리면 Ev가 꺾여 올라가면서 발생하는 band 터널링 효과인데

이렇게 접촉 길이 (Lov)를 아예 줄여버리면 GIDL 자체가 줄어들 수밖에는 없음

하지만 Lov를 줄이게 되면 Gate의 단면적을 줄이는 것이기 때문에, Gate의 저항이 커지고 소자 동작 속도가 느려진다 T_T

그리고 깊이 파버리는 것도 어렵,,

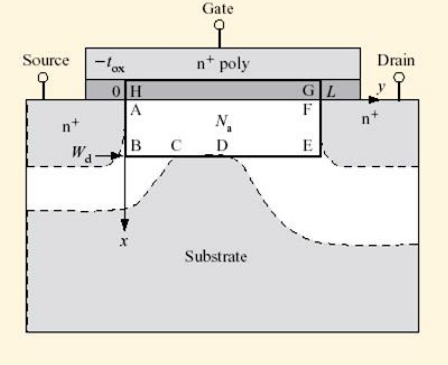

Short channel effect and device design

여기서 보면 채널이 형성되고, 충분한 양의 VG가 가해졌다면 이미 channel 쪽이 도체와 같은 성질을 띄게 되어서 더 큰 VG를 주어도 Depletion 영역이 넓어지지는 않는다.

Wdm은 도핑 농도에 의해서 결정된다고 보면 됨 !!

( 자세히는 안배웠지만 사실 저렇게 표면에서 형성된 건 channel이라고 불러서 n+의 도핑된 전자들이 있으니까 majority carrier가 있는데,

막 Punch through(??) 같은 애들은 body 쪽에서 depletion 영역이 맞닿는 거라서 carrier가 없다. 하지만 이때 Drain 전압이 참을 수 없을 정도로(!!) 높아지면 minority carrier를 끌어당기기 시작하면서 전류가 흐르게 됨 이때 망가진다고 보면 될듯 (Gate 전압으로 전류가 조절되는게 아니니까))

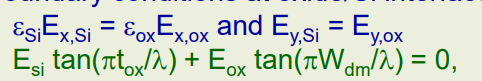

어쨌든 boundary condition을 쓰면 (Gate가 저장하고 있는 총전하량과 channel에서 전하량이 같다)

이렇게 되고 왜인지는 잘 모르겠으나

이렇게 된대

따라서 채널 length인 L과 tox의 관계식을 찾을 수 있게 되는데

이때 SS를 보면 실리콘 캐패시턴스에는 비례하고, Gate oxide의 캐패시턴스에는 반비례하는 것을 알 수 있다. (Gate oxide 얇을수록 캐패시턴스 커짐, 그러면 channel에 전압이 많이 걸림 -> 동작이 쉬워지겠지 / 대신에 lkg current가 증가하고 off current가 증가함)

gate oxide의 캐패시터를 작게 만들면 ss가 감소함, 이 말은 게이트에 전압을 걸 때 gate oxide에 많은 전압이 걸리게 되고

여기서 하고 싶은 거는 gate ox의 두께를 정하고 channel length를 어느정도까지 줄여도 되는지 결정하기

DRAM의 경우 ss가 충분히 작아야 Vg가 꺼졌을 때 트랜지스터가 충분히 꺼질 수 있음

Logic에서는 On current가 더 중요해서 Vt를 좀 떨어뜨려야함. (직접적인 연관은 아니지만 Vt를 떨어뜨릴 때 SS보존하기 어려워서 결국 SS 어느정도 희생해야함)

Logic Transistor에서는 L ~20tox-25tox 정도, DRAM에서는 L~35tox-40tox

DRAM에서는 L이 좀 길지 그러니까 Off current가 적겠지

DRAM cell architecturers and sensing

이제는 소자 scaling을 넘어서서 만들어진 애를 어떻게 배치할 거냐의 문제도 집적도 향상에 매우 중요해졌다

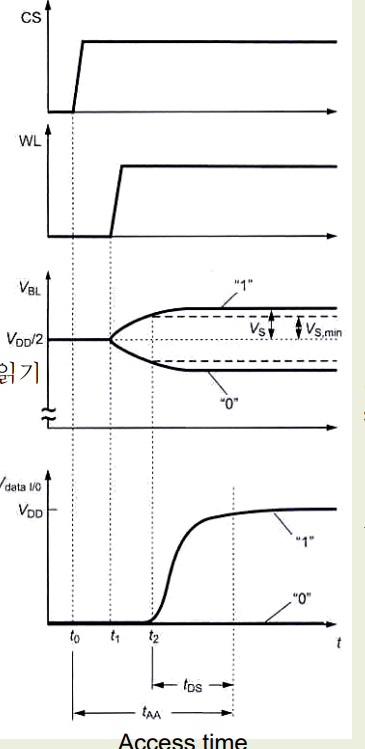

DRAM이 작동하는 timing diagram을 살펴보자

맨처음 WL과 BL에 신호를 주면 VBL에 변화가 감지됨 ( 전류가 새어 나옴)

이걸 Sense amp가 감지해서 맨 아래서처럼 0또는 1로 휙휙 바꿔줌

Access time은 신호주고 동작까지 완료한 시간

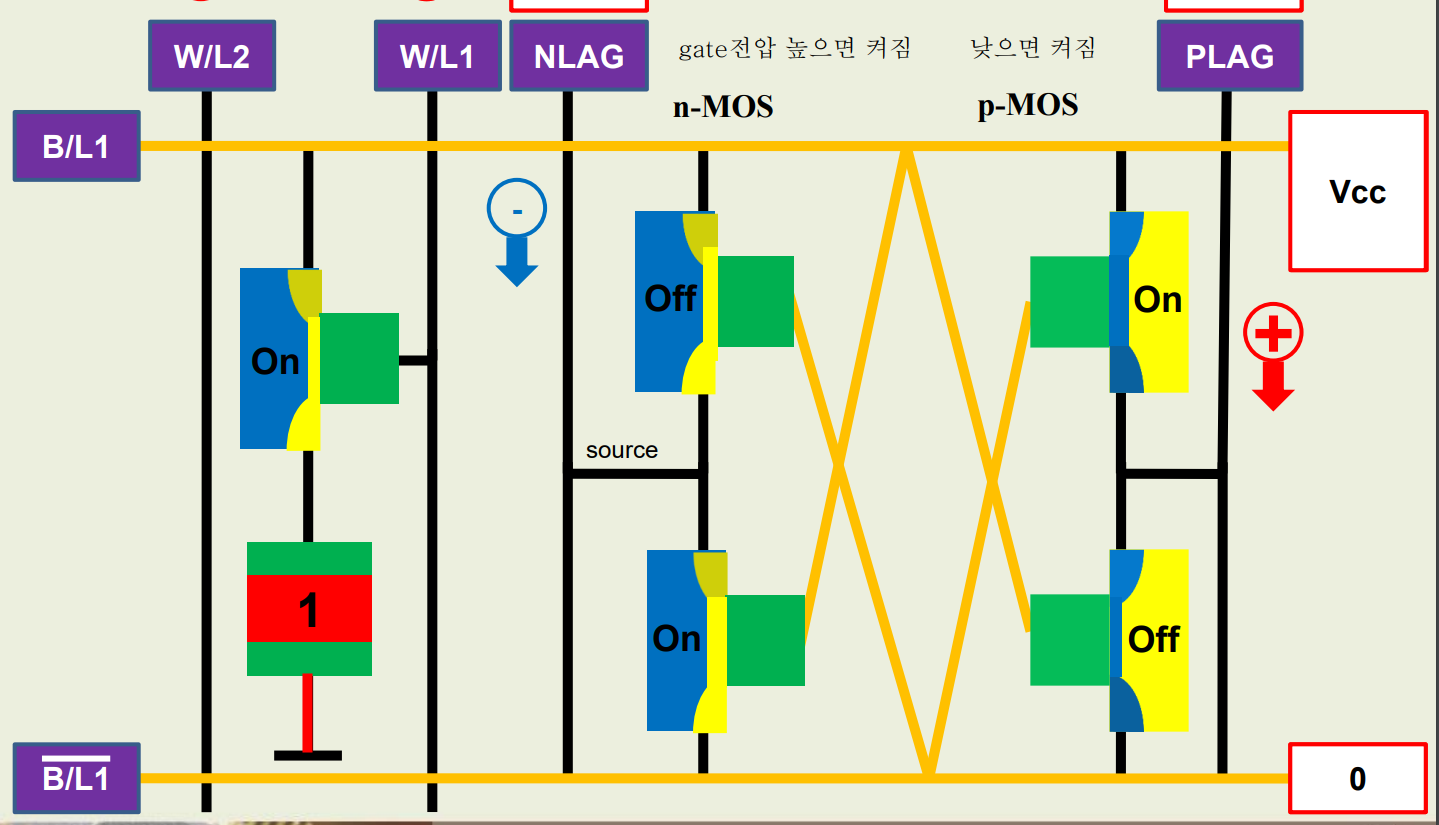

Read "1"

사진이 이거 밖에 없는 on /off 다 무시하고, 순서만 써보겠다.

-

맨처음에 저 빨간색 Cap에는 1이 저장되어 있었다. 얘를 읽고 싶어서 W/L1을 켜고, 나머지들 전부 Vcc/2

-

그렇게 되면 Transistor가 켜져서 cap에 있던 전류가 B/L1으로 새어나오게 되고 Vcc/2 + delVb가 됨 그렇게 되면 여기에 연결된 아래의 n-Mos가 slightly on, p-Mos는 약간 꺼진 상태가 됨

-

NLAG에는 0, PLAG에는 Vcc를 줌

-

그러면 아래의 p-mos는 완전히 꺼지게 되고, 위쪽의 p-MOS의 경우 PLAG와 연결된 source 전압이 B/L 레퍼런스보다 높아져서 완전히 켜지게 됨다. 따라서 B/L이 VCC로 바뀜

그리고 위쪽 n-MOS가 완전히 꺼지게 되고, 아래쪽 n-MOS가 완전히 켜지게 되면서 B/L 레퍼런스가 0이 된다. -

이상황에서 B/L1이 다시 Vcc가 되었기 때문에 cap에는 다시 1이 써지게 된다. (Write Back)

Read "0"

얘도 맨처음에 Vcc/2로 시작함

-

W/L1을 켜줌

-

B/L1의 전류가 캐패시터로 흘러들어가겠지 그럼 Vcc/2 -delVb가 됨

-

아래쪽 n-MOS 살짝 꺼지고, 위쪽 p-MOS 살짝 꺼짐

-

NLAG에는 0, PLAG에는 Vcc를 줌

-

그렇다면 위쪽의 n-MOS가 완전 켜지고, 아래쪽 p-MOS 완전 켜짐

-

고러면 B/L1은 0, B/L1 reference는 Vcc가 됨

-

다시 Cap에는 0이 저장됨 ㄷ ㄷ ㄷ

헐 이제 이해했는데 그러면 Read할 때는 W/L만 켜주니까 사실상 연결된 모든 W/L에서 B/L로 누설됐다가 다시 write back이 되는 것임 ㄷ ㄷ ㄷ ㄷ

*여기서부터 몹시 재미씀**

W/L에 달린 1k개의 cell들이 한꺼번에 read가 되는 상황 그런데 생각해보면 컴퓨터 시스템에서 메모리에서 정보를 읽어올 때 Page 단위로 읽어옴 그래서 저렇게 한꺼번에 읽어오는게 상관이 없게 됨

그런데 이제 이렇게 되려면 B/L1과 B/L1의 레퍼런스 전압이 동일하게 Vcc/2가 되어야함 그러려면 Capacitance가 동일해야하는데 이게 쉽지 않음

(B/L은 너무 길기 때문에 ㅠㅠ)

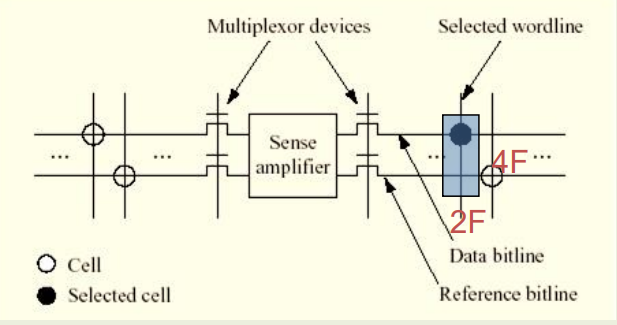

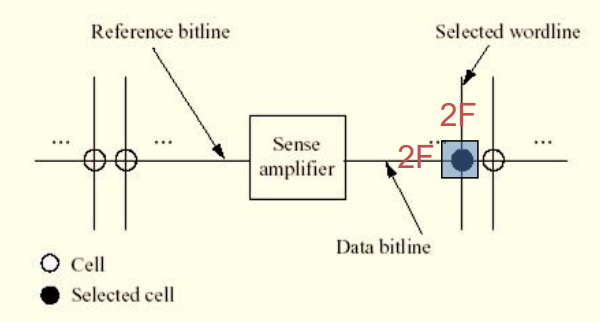

Folded-bitline array architecture : 8F^2

자 그래서, DRAM에서 읽기 동작을 수행하려면 B/L과 B/L 레퍼런스가 아주 중요하다는 것을 이해했다.

그래서 다양한 방법이 있는데 이 그림에서 보면 이제 아래쪽에 있는 cell을 read할 때 위의 B/L을 레퍼런스로 잡는다. 그런데 만약 같은 WL에 B/L 레퍼런스에 셀이 위치한다면?

WL이 켜질 때마다 위에있는 cell에서도 B/L으로 전류가 막 새어 나올 것이다.

이러면 B/L과 B/L 레퍼런스를 비교해서 정보를 읽는게 불가능해짐 ㅠㅠ

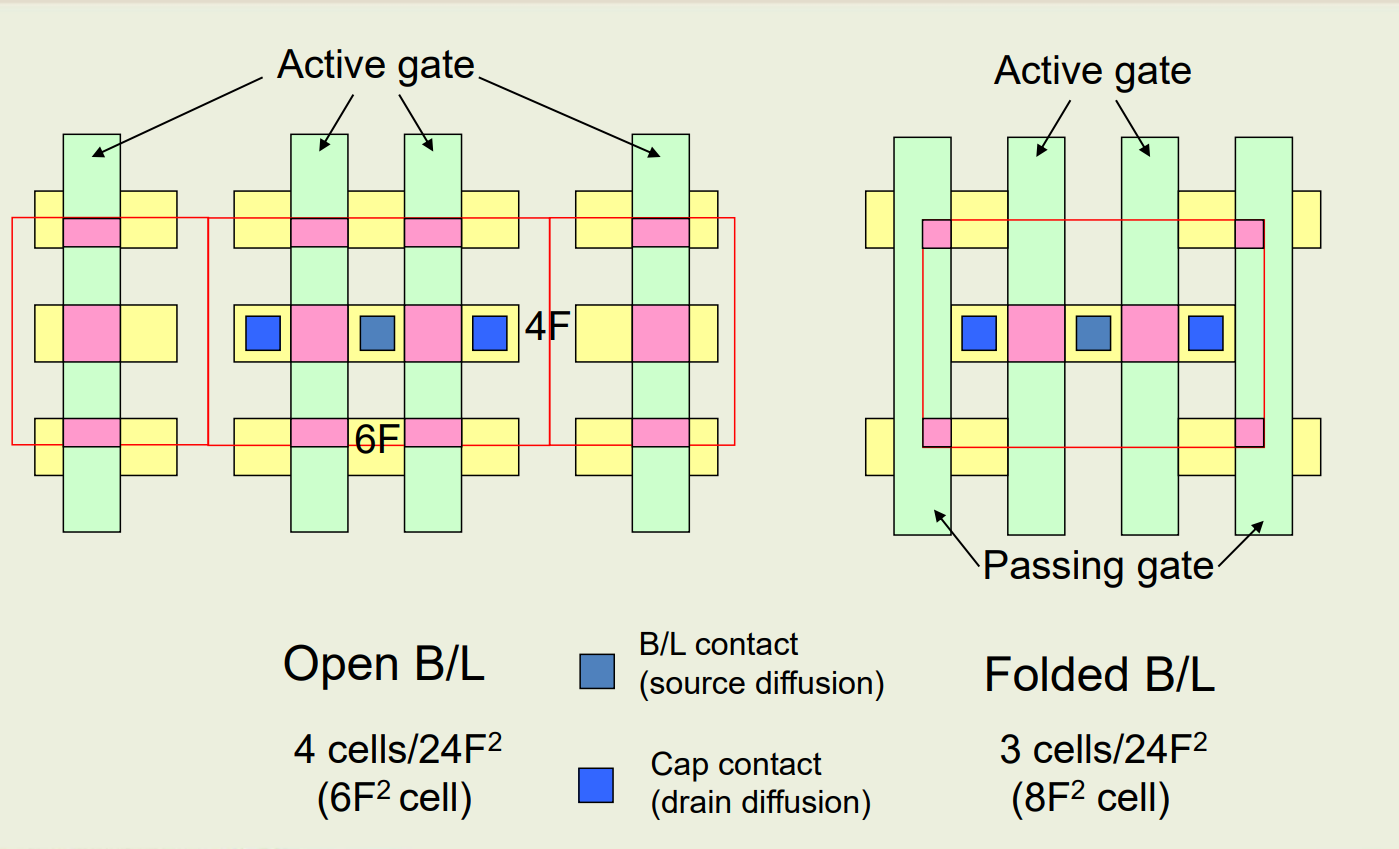

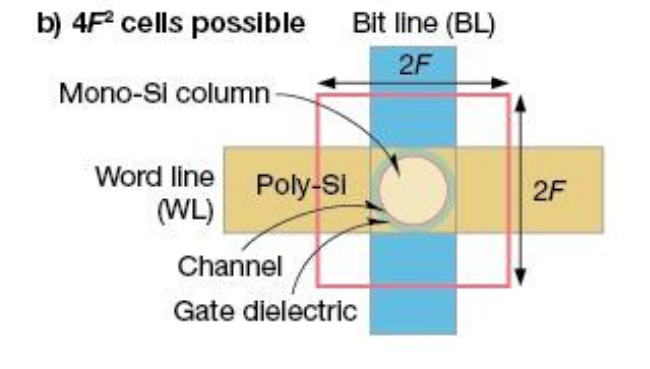

그래서 저렇게 격자 형태로 배열을 하게 되었고, F에 대해서 4F^2은 당연히 불가능

그리고 가운데 Sense amp를 둬서 양쪽을 읽기 때문에 더 많은 cell area controll이 가능하다 !

어쨌든 저렇게 격자무늬로 두는건 누가봐도 낭비아닌가,,, 싶은 그래서 등장한게

Open-bitline architecture

이렇게 되면 모든 위치에 cell을 둘 수 있어서 언뜻 보기에는 4F^2이 될 것처럼 보인다 (하지만 당연히 안됨ㅋ)

B/L과 레퍼런스 B/L의 캐패시턴스가 동일해야하기 때문에, 아무래도 같은 쪽에 있는 Folded-bitline이 그렇게 유지하기가 쉽다

bit line 하나를 두개의 cell이 같이 쓴다고 생각해보자

이때 b/l이랑 Capacitor랑 접촉이 되면 안돼 (접촉될수록 Cb가 증가하게 됨)

그래서 올렸을 때 결국 2F안되고 2.5F * 4F가 된다

Open B/L은 결과적으로 6F^2으로 볼 수 있고, folded는 8F2

Capacitor랑 BL이 통과하면 안돼서 이런식으로 BL을 Capacitor랑 다른 곳으로 이렇게 한 칸 올려줘야함

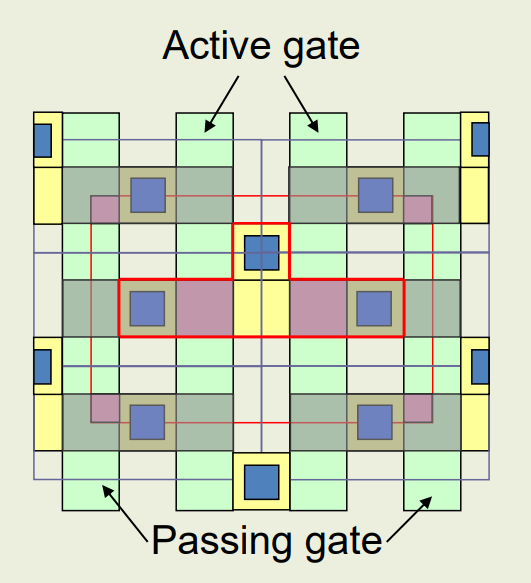

Array architectures: for sub-8F^2 cell, twisted bitline array

B/L을 하나는 위에 하나는 아래에해서 Cb같도록

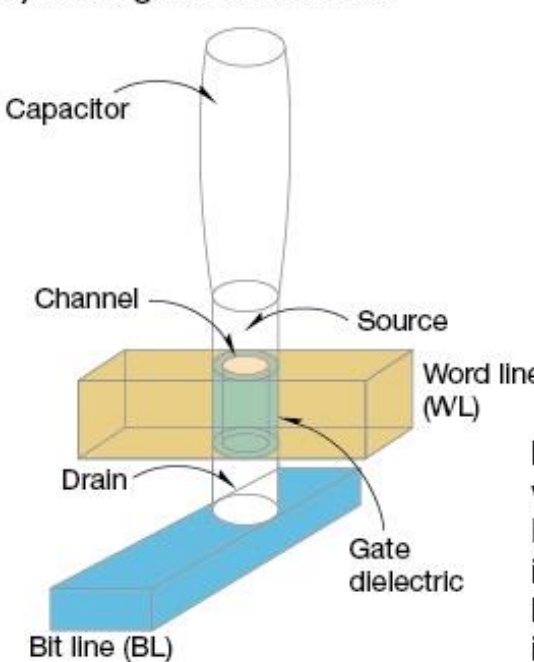

DRAM Vertical cell & buried B/L

이런식응로 하면 Cell이랑 BL이 애초에 닿지를 않음

-> Cb가 커지지 않음( 캐패시터와 접촉하면 Cb증가함)

그렇다면 4F^2이 될까?????????????

안됨

왜냐 저렇게 하려면 결국

이런 그림을 오른쪽, 즉 화면에 수직한 화면을 생각해봤을 때, cell과 cell 간격이 일단 F는 되어야하고 그러한 기둥 형태를 WL이 감싸고 있을 것임.

그럼 그게 총 F안에 들어와야하는데 그러면 WL의 두께를 매우 얇게 만들어야하겠지

이론적으로는 채널 F에 사이 공간 F있을 거고 WL 넣을 자리가 없을텐데 뭐 어찌저찌 채널 줄여서 WL을 붙였다고 생각해보자

그러면 채널 두께 얇아져서 성능도 안좋아지고, WL 너무 얇아지면 저항이 너무 커짐

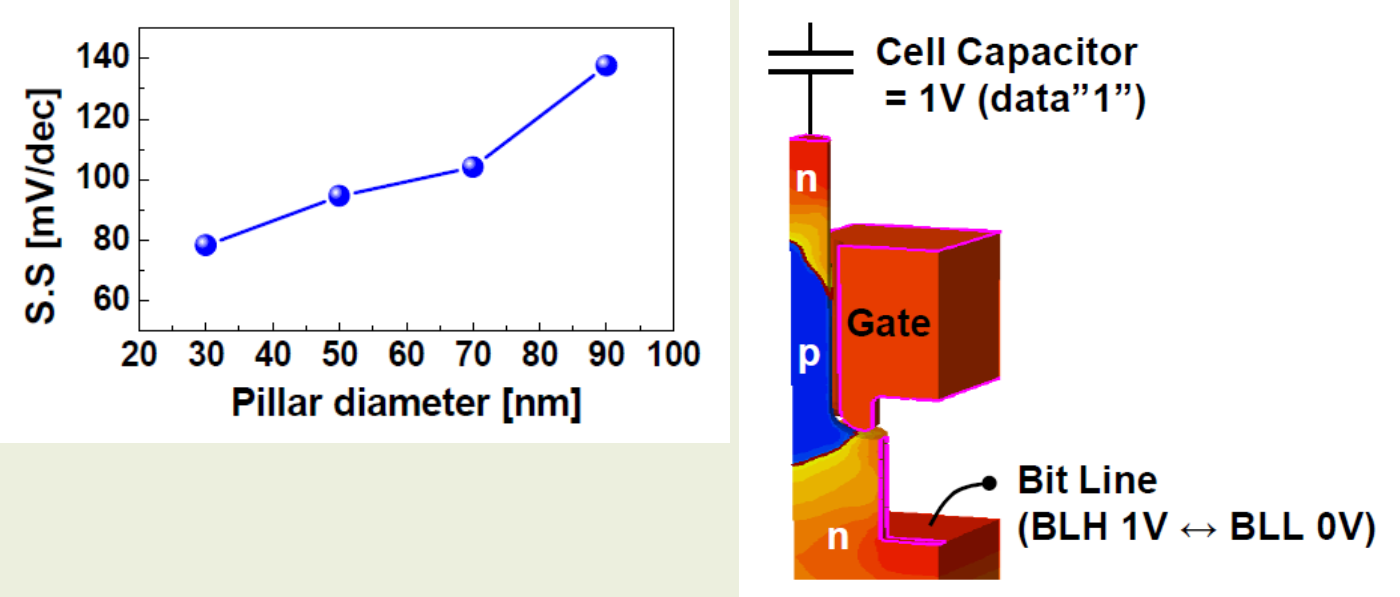

Subthreshold Swing

위에서 언급했듯이 이 값은 Vt보다 낮은 전압에서 전류를 10배 증가시키기 위해 필요한 게이트 전압이다.

SS가 작아야, on/off가 확실히 된다. (당연함. 조금만 gate 전압 높여도 on이 되고 낮추면 off가 됨)

얘의 이상치는 60mV라는 한계를 갖는데, 이는 전류가 thermal injection에 의해 흐르기 때문임. 따라서 이한계를 극복하려면 열통계적분포가 아닌 다른 요인에 의해 전류가 결정되는 소자를 사용해야함 (Ex. 터널링)

여튼 SS가 작아야 gate가 잘 꺼지고, 따라서 short channel effect도 줄어든다.

그런데 이제 이런 구조에서 pillar 직경이 작아지면 ss 또한 감소해서 좋아짐

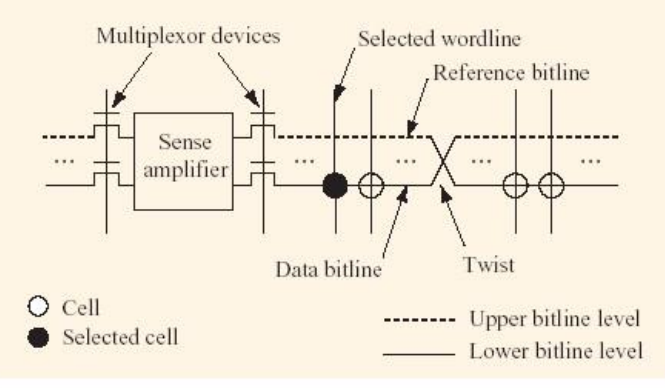

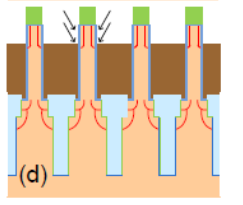

Vertical Pillar Transistor cell Array

여기서 포인트는

1. 저 빨간색이 양쪽해서 하나가 BL이라는 점

2. Word gate가 수직한 쪽으로 보면 굉장히 얇게 이 기둥을 감싸고 있다는 점

근데 실제로는 기둥마다 길이 맞추는 것도 어려워서 Trainsistor마다 Vt의 산포가 커진다 ㅠㅠ 그래서 상용화는 안됐대

Candidate channel material of 3D DRAM

Single crystalline

-얜 좋은데 시간이 너무 오래걸림 (Si/ SiGE 번갈아가면서 쌓고 에칭)

Poly-Si

얘는 Si / SiO2 합쳐서 마구잡이로 만드는데 grain boundary때문에 각 채널마다 성질이 일정하지 않다.

비정질

이동성이 낮음 (on current가 너무 작음)

따라서 이동성 어느정도 괜찮은 비정질 산화물 반도체를 쓴다! (ZTO, IGZO)

3D DRAM의 새로운 이슈 : 온도

디램을 적층하면 열이 못빠져나가서 off current가 증가한다.

따라서 산화물 반도체(AOS)를 사용하면 off current를 낮출 수 있다.

왜냐ㅑ bandgap이 3eV이상으로 매우 커서 channel을 통한 lkg current도 없고, 온도 올라가도 lkg current가 많이 증가안함

3D DRAM의 장점

- 집적도 향상

- BL cap 줄이기 가능

- 리소그라피 줄이는 것대신 다양한 재료를 골라서 해볼 수 있음

단점

Thermal budget

cell 간의 영향

에칭 공정이 어려워짐 따라서 구조적으로, 잘 쌓아야하고