Pipelining

One instruction is executed through multiple stages.

Stages

Typically, an instruction execution consists of the following stages:

- Fetch (IF - Instruction Fetch): The instruction is retrieved from memory.

- Decode (ID - Instruction Decode): The fetched instruction is decoded to determine the operation and the operands involved.

- Execute (EX): The operation specified by the instruction is performed, which may involve arithmetic or logical calculations.

- Memory Access (MEM): If the instruction requires reading from or writing to memory (for load/store instructions), this stage handles those operations.

- Write Back (WB): The results of the execution are written back to the register file.

Example

I1: ADD R1, R2, R3I2: SUB R4, R5, R6I3: LW R7, 100(R8)

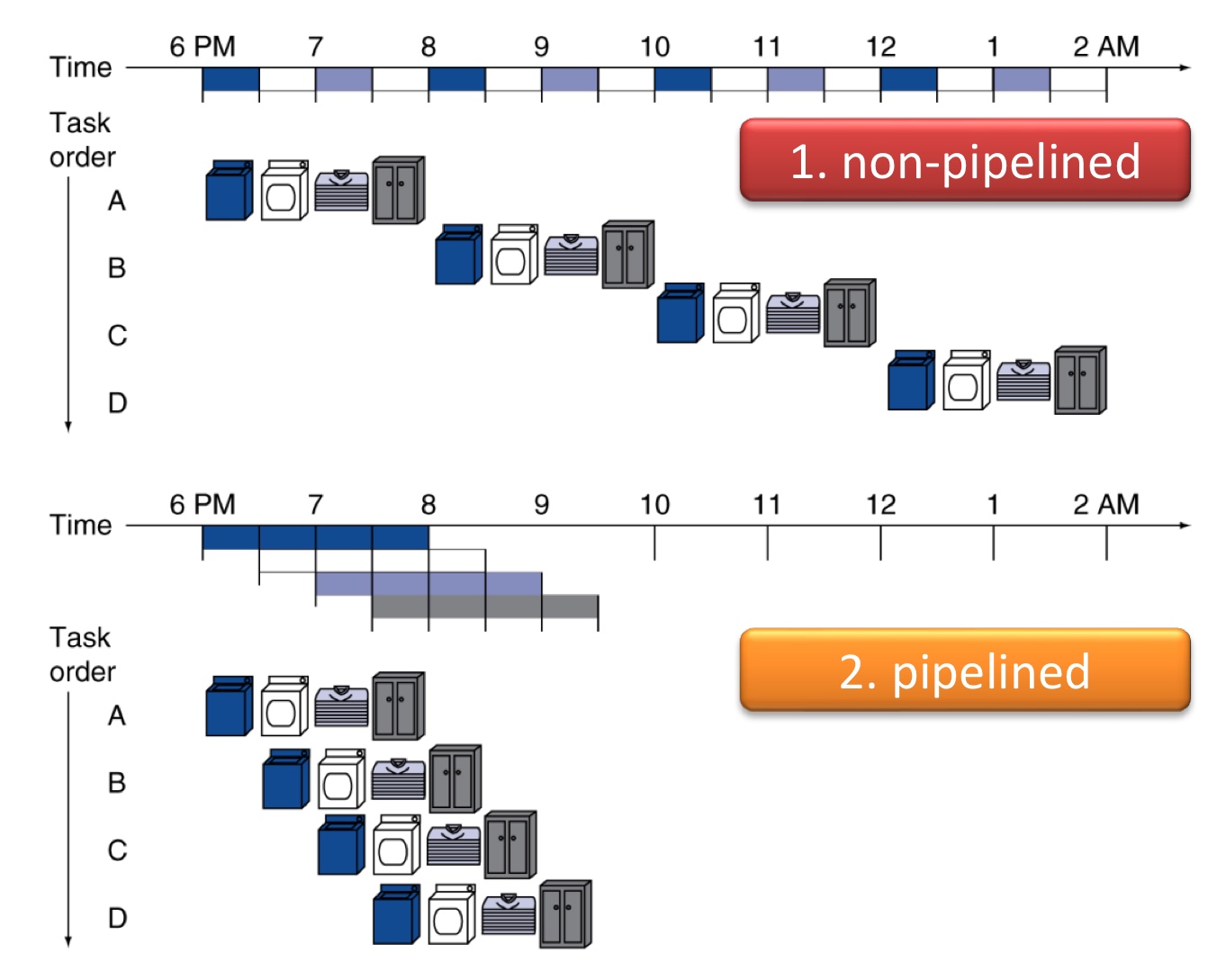

Without Pipelining:

| Cycle | Fetch (IF) | Decode (ID) | Execute (EX) | Memory (MEM) | Write Back (WB) |

|---|---|---|---|---|---|

| 1 | I1 | ||||

| 2 | I1 | ||||

| 3 | I1 | ||||

| 4 | I1 | ||||

| 5 | I1 | ||||

| 6 | I2 | ||||

| 7 | I2 | ||||

| 8 | I2 | ||||

| 9 | I2 | ||||

| 10 | I2 | ||||

| 11 | I3 | ||||

| 12 | I3 | ||||

| 13 | I3 | ||||

| 14 | I3 | ||||

| 15 | I3 |

With Pipelining

| Cycle | Fetch (IF) | Decode (ID) | Execute (EX) | Memory (MEM) | Write Back (WB) |

|---|---|---|---|---|---|

| 1 | I1 | ||||

| 2 | I2 | I1 | |||

| 3 | I3 | I2 | I1 | ||

| 4 | I3 | I2 | I1 | ||

| 5 | I3 | I2 | I1 | ||

| 6 | I3 | I2 | |||

| 7 | I3 |

There's some pitfalls such as problems from branching, but pipelining obviously improves performance