모든 내용을 정리하는 것이 아니라, 주 맥락이나 파헤치며 배우고 깨닫게 된 부분에 대해서 정리합니다.

하아... 일단 2강은 너무 재미없었다. 뭔가 부족하게 알아서 그런가 아무튼 시작!

Instruction Set Architecture I (ISA)

강의보다 블로그 정리가 더 잘 되어있어 참고하여 정리한다.

출처

-

명령어 집합 구조 이며, 마이크로프로세서가 인식해서 기능을 이해하고 실행할 수 있는 기계어 명령어를 말한다.

-

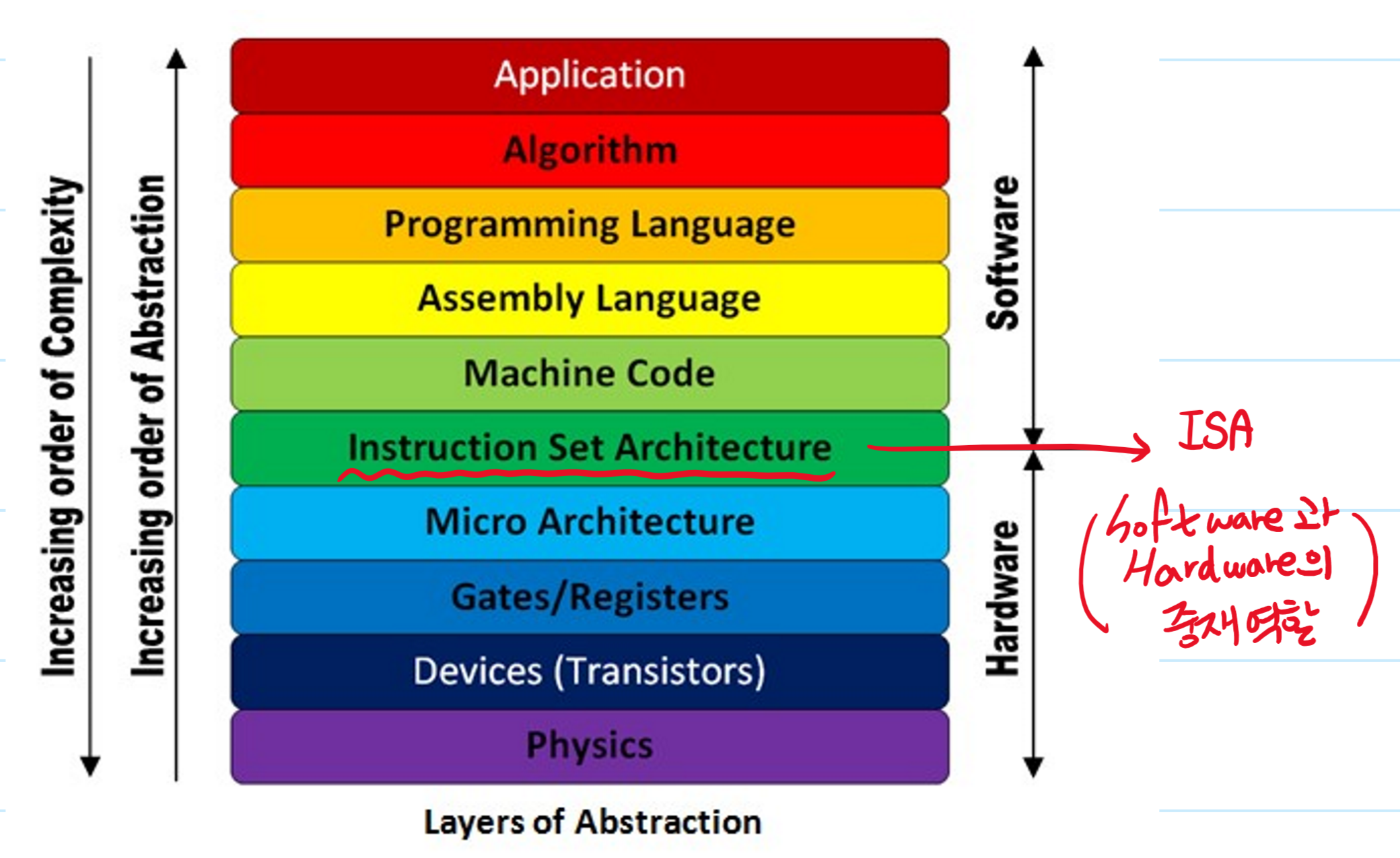

다양한 단계를 거쳐서 Software 에서 Hardware로 넘어가게 된다.

이때, Software 에서 Hardware 로 넘어가는 단계에서 중재자 역할 을 해주는 것이 ISA.

-

ISA는 최하위 레벨의 프로그래밍 인터페이스로, 프로세서가 실행할 수 있는 모든 명령어들을 포함한다.

-

🎯🔥따라서 ISA는 아래 요소들이 명시되거나 결정되어 있다.🔥🎯

- Data format and size

- “Programmer Visible State” (a.k.a. architectural state)

- Instructions: how to changethe programmer visible state?

- Instruction-to-binary (or vice versa) encoding

- How to interface with the outside world?

- Protection and privileged operations

- Software conventions

- Memory Addressing Mode

용어로 개념 정리

CPU Architecture

아래 세 가지 메인 서브 카테고리를 포함한다.

- Instruction set architecture, or ISA,

- Microarchitecture, also known as Computer organization

- System Design

그리고, ISA의 예시로 Intel x86-64, Arm v8, RISC-V이다.

Bit

Bit는 CPU가 처리하는 데이터의 최소 단위(레지스터)의 크기가 몇 Bit인지?에서 나온 말.

x64 vs x86

32비트 환경을 x86이라고 하는게 아니라, 통칭 x86계열의 CPU가 32비트까지 나와있고, 여기서 64비트를 지원하도록 확장된게 x86-64죠. 그래서 x86-64를 줄여서 간단히 x64...

x86-64

x86 명령어 집합 아키텍처의 64비트 버전이다. x86-64 명령어 집합은 에뮬레이션 없이 인텔의 x86를 지원하며 AMD64로 이름 붙인 AMD에 의해 고안되었다.

RISC(Reduced Instruction Set Computing)

A. 단순하고, 빠르고, 효율적인 소수의 명령

B. 복잡한 처리는 모두 소프트웨어를 이용

CISC(Complex Instruction Set Computing)

A. 편리하고 강력한 다수의 명령

B. 여러 개의 명령을 하나의 명령으로 처리

RISC-V

2010년부터 미국의 UC 버클리대학에서 개발중인 새로운 컴퓨터 CPU 구조이다. 리스크 브이가 아니라 "리스크 파이브(risc-five)"라고 발음하며, V는 영문 알파벳 V가 아닌 로마숫자 5를 가리킨다.

Stored Program (von Neumann) Architecture

내장 메모리 순차처리 방식으로서, 데이터 메모리와 프로그램 메모리가 구분되어 있지 않고, 하나의 버스를 가지고 있는 구조를 말한다.

Von Neumann vs. Dataflow

Dataflow적 구조의 경우 Program Counter가 없이 데이터 흐름에 따라 instruction 순서가 결정되는데 반해, Von Neumann 구조는 데이터 메모리와 프로그램 메모리가 구분되어 있지 않아서, Von-Neumann Bottleneck 이 생기게 된다. 과연 둘 중 어느 것이 더 나은가? 장단점 및 한계는?

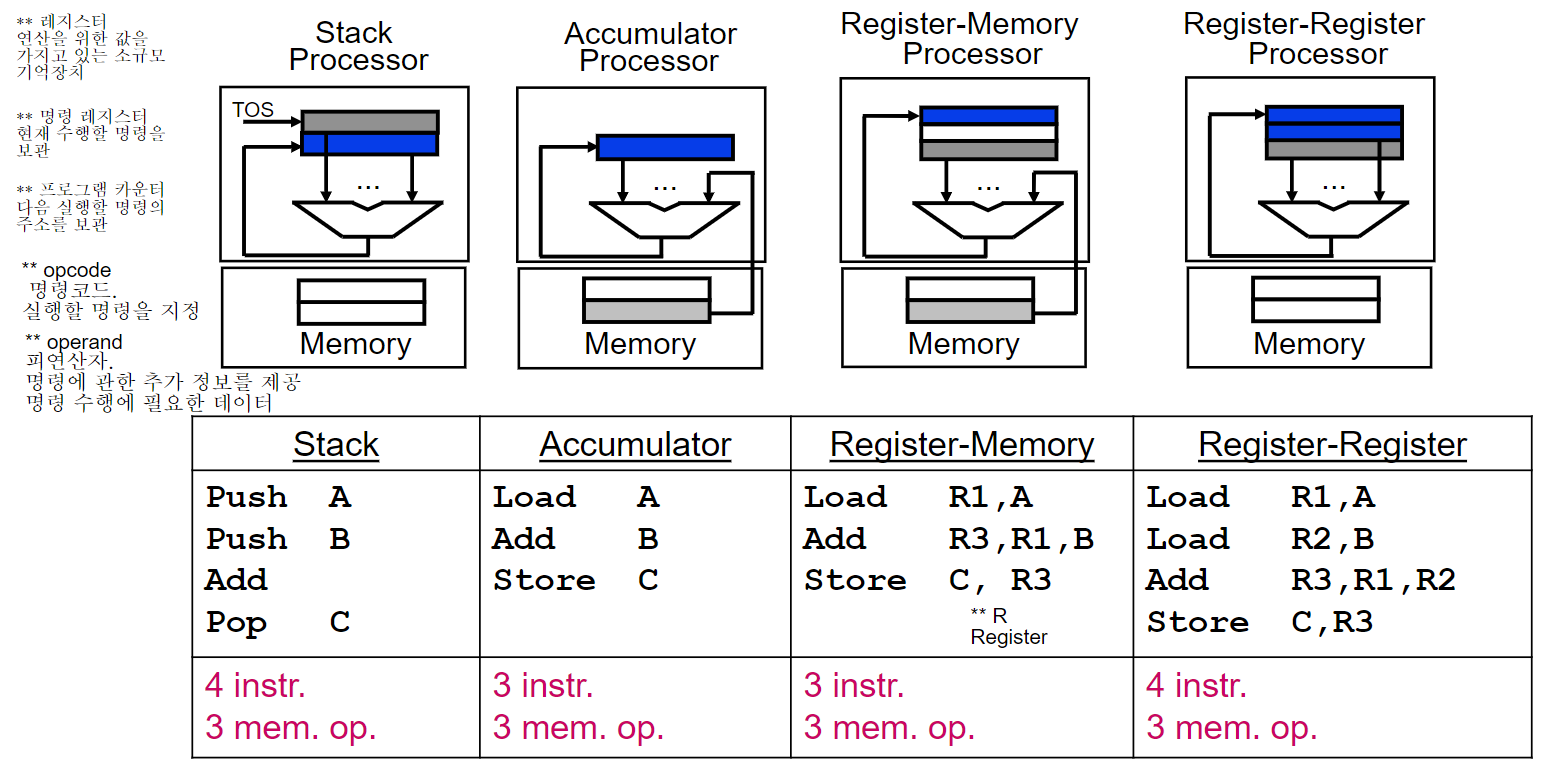

ISA Examples & Code Sequence for C=A+B

-

어떻게 보면, 기술 발전에 따라 왼쪽에서 오른쪽으로 개발되었다고 볼 수 있다.

- 메모리 용량 및 성능 기술, 프로그래밍과 컴파일, 더 빠른 속도의 메모리 기술.

- Stack architecture - Early machines

- Accumulator architecture - Early machines

- General purpose register (GPR) architecture: machines after 1980.

-

메모리에 저장된 것을 Load하고 다시 메모리에 저장하는 것

-

CPU 내부에 존재하며 직접적으로 ALU에 연결되어 입출력 값을 저장하는 레지스터의 출현

-

RISC와 같이 register-to-register로 ALU ops가 이동하여 간단한 데이터 이동으로 빠르게 구현. (load-store architecture = RISC)

추가로 대략적으로 레지스터(CPU Registers), 캐시(Static RAM), 메모리(Dynamic RAM), 디스크(Magnetic Disk) 순으로 용량이 커지고 속도는 느려진다.