I/O 장치 | DMA | CPU (DMA는 I/O장치 담당 일진)

DMA (Direct Memory Access)

직역하면 직접 메모리 접근

- CPU의 개입 없이, 장치(디바이스)가 메모리와 직접 데이터 전송하는 방식

보통 데이터를 주고받을 때는

디바이스 → CPU → 메모리

메모리 → CPU → 디바이스이렇게 CPU가 중간에서 계속 데이터 전송을 중계함.

근데 이러면 CPU가 계속 데이터 전송 처리에 붙잡혀서 다른 중요한 연산을 못함

- 그래서 CPU를 거치지 않고 장치가 메모리랑 직접 데이터를 주고받게 만든 게 DMA

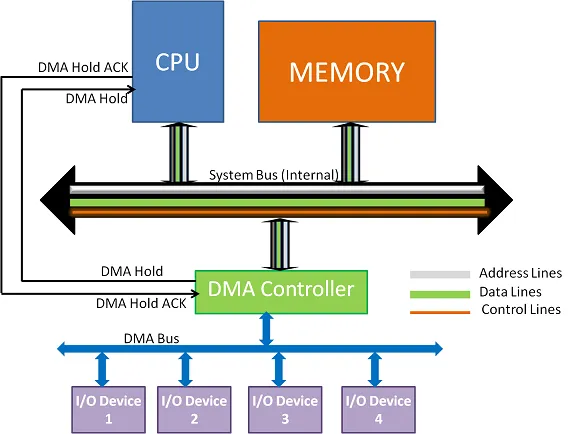

구조

- 일반적인 데이터 이동 (CPU 이용)

[디바이스] → [CPU] → [메모리]

CPU가 일일이 데이터를 받아서 메모리로 전송

- DMA 이용

[디바이스] → [DMA 컨트롤러] → [메모리]

DMA 컨트롤러(DMA Controller):

데이터를 어디에서 어디로, 얼마나, 어떻게 옮길지 관리하는 독립적인 하드웨어

CPU는 명령만 내려주고 옆에서 쉬고 있음

(데이터 전송 다 끝나면 DMA가 CPU에게 “다 끝났어~” 하고 인터럽트로 알려줌)

동작 과정

-

CPU가 DMA에게

→ “이 주소에서 저 주소로 데이터 1024바이트 옮겨!”

→ 명령 전달

-

CPU는 다른 일 하러 감

-

DMA가 디바이스와 메모리 사이에 직접 데이터 전송

-

전송 끝나면

→ DMA가 CPU에게 인터럽트 발생

→ “데이터 옮겼다!”

DMA의 전송 방식

| 방식 | 설명 |

|---|---|

| Burst Mode (블록 전송) | 한 번에 데이터 블록 통째로 전송. 빠르지만, 그동안 버스 독점 |

| Cycle Stealing Mode | CPU와 버스 사용권을 번갈아가며 사용 (CPU 작업 잠깐 멈추고 DMA가 버스 사용) |

| Transparent Mode | CPU가 버스 안 쓸 때만 DMA가 사용 (가장 CPU 친화적, 느림) |

DMA의 장점

- CPU 부하 감소

- 데이터 전송 속도 향상

- CPU는 계산/연산 같은 중요한 일에 집중 가능

DMA의 단점

- 하드웨어 복잡성 증가

- 버스 경합 발생 가능 (특히 Burst Mode)

DMA가 쓰이는 곳

| 분야 | 활용 예시 |

|---|---|

| 💾 저장장치 | 디스크 ↔ 메모리 데이터 전송 |

| 🎮 그래픽 처리 | GPU ↔ 메모리 이미지 전송 |

| 🎧 오디오 처리 | 사운드카드 ↔ 메모리 오디오 데이터 |

| 📡 네트워크 | NIC ↔ 메모리 패킷 전송 |

- CPU는 명령만 주고 기다림

- DMA가 디바이스와 메모리 사이 데이터 전송

- 끝나면 CPU에 인터럽트

CPU vs DMA 전송 방식 비교

| 항목 | CPU 방식 | DMA 방식 |

|---|---|---|

| 처리 방식 | CPU가 직접 데이터 이동 | DMA 컨트롤러가 전담 |

| CPU 개입 | 계속 필요 | 명령만 내리고 대기 |

| 속도 | 느림 (CPU 부하) | 빠름 (CPU 자유로움) |

| 효율성 | 저효율 | 고효율 |

정리

DMA는 CPU를 데이터 전송에서 해방시켜 효율적인 시스템 동작을 가능하게 하는 하드웨어 기술

실제 OS 커널이나 하드웨어 설계 공부할 때,

DMA가 인터럽트와 버스, 메모리 매핑이랑 같이 작동하는 구조를 알아야 디바이스 드라이버, 커널 네트워크, 디스크 I/O 같은 것까지 이해가 잘됨

참고

DMA 컨트롤러는 어디에 있을까?

과거에는 CPU 칩셋 외부에 독립적인 DMA 컨트롤러 칩이 따로 있었음

예를 들어 옛날 PC에는 Intel 8237 DMA 컨트롤러 같은 게 메인보드에 따로 박힘

요즘 시스템은 CPU 칩셋이나 SoC 내부에 DMA 컨트롤러가 통합되어 있음

즉, CPU 칩셋 안에

- 일반적인 데스크탑/서버용 메인보드에서는 칩셋(보통 Southbridge/Platform Controller Hub) 안에 DMA 기능 포함

- 스마트폰이나 임베디드 SoC에서는 CPU, GPU, DMA, 메모리 컨트롤러 다 한 칩에 있음

예전 구조 (외부 DMA)

[CPU] ── [DMA 컨트롤러] ── [메모리]

│

[디바이스]

현대 구조 (칩셋/SoC 내부 통합)

[CPU] ──┐

│

[칩셋 (PCH)]

│

┌───────────┐

│ DMA 컨트롤러 │

└───────────┘

│

[메모리] ↔ [디바이스]

혹은 SoC라면

[SoC]

├── CPU

├── DMA 컨트롤러

├── GPU

├── 메모리 컨트롤러

└── I/O 컨트롤러

짤에 설명이 추가되었네요 !👍 좋아요