- 버스는 공용으로 쓰는 통로이기 때문에 서로 요청이 들어 왔을 때 우선 순위를 정해줘야한다!

- 버스란? 구성요소들 서로간의 정보를 주고받는 통로를 시스템 버스라고 한다.

- 자세한 내용은 이전 포스팅 "컴퓨터 구성 요소 간 통신" 확인하기!

▶ 시스템 버스 구조

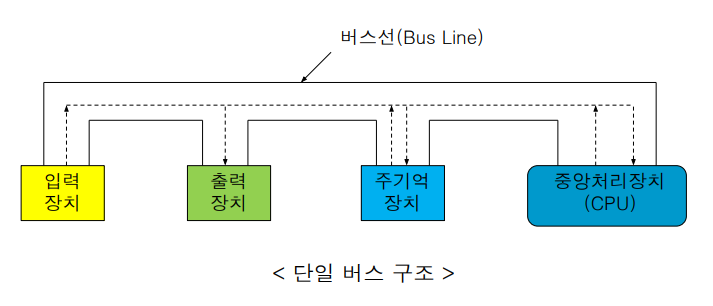

▷ 단일 버스 구조

- 구조

- 모든 장치들이 하나의 버스에 연결

-

특징

- 한 개의 통로를 가진다.

- 버스는 오직 하나의 전송만 가능 → 두 개의 장치에서만 동시에 사용 가능

-

장점

- 경비와 저렴하며 주변 장치 쉽게 연결

-

단점

- 동작 속도가 느리다. → 대기 시간 길어짐

- 동작 속도가 느리다. → 대기 시간 길어짐

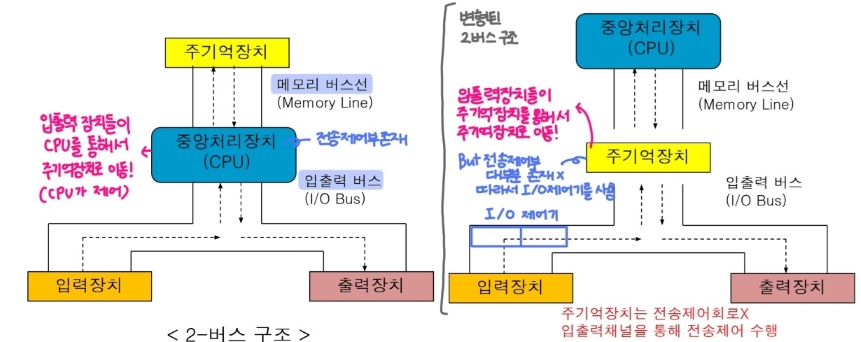

▷ 2-버스 구조

-

구조

- CPU-주기억장치 사이는 메모리 버스를 통한 데이터 교류

- CPU-입출력장치 사이는 I/O 버스를 통한 데이터 교류

-

특징

- 두 개의 통로를 가진다.

- 데이터들은 CPU를 통하여 주기억장치로 가게된다.

-

구분

- 변형되지 않은 2-버스 구조

- 입출력장치에서 교환되는 데이터들이 주기억장치로 갈 때 CPU를 통해서 간다.

- 입출력을 할 때 CPU 제어로 처리한다. (CPU를 거쳐 가기 때문)

- 입출력장치에서 교환되는 데이터들이 주기억장치로 갈 때 CPU를 통해서 간다.

- 변형된 2-버스 구조

- 입출력장치에서 교환되는 데이터들이 주기억장치로 갈 때 주기억장치를 통해서 간다.

- 하지만, 주기억 장치에는 전송제어부가 대부분 존재하지 않기 때문에 대부분 I/O 장치를 사용한다.

- 변형되지 않은 2-버스 구조

▶ 시스템 버스

- 이전 포스팅 "컴퓨터 구성 요소 간 통신" 에서 다뤘던 내용이다! 잠깐 복습해보자.

- 데이터 버스: 데이터 전송, 양방향

- 주소 버스: 기억장치에 대해 쓰기/읽기 동작, 단방향

- 주소 버스 비트 수에 의해 전체 기억장치 용량이 결정된다.

- 제어 버스: 제어 신호 전송

▷ 버스 사이클

- 개념

- 버스를 사용해 기억장치에서 입출력 장치에서 데이터를 읽거나 쓰기 위해, 버스를 이용해 반복적으로 수행하는 일련의 연속 동작

-

쓰기 동작의 순서

① 버스 마스터가 버스 사용권 획득한 다음

② 버스를 통해 주소, 데이터, 쓰기 신호 전송

* 버스 마스터 : 버스를 직접 제어, 버스를 쓰고 있는 주체

버스에는 여러 개의 버스 마스터가 존재하지만, 어떤 한 순간에는 하나의 마스터만 장악하여 사용한다.

-

읽기 동작의 순서

① 버스 마스터가 버스 사용권 획득한 다음

② 주소와 읽기 신호를 전송하고, 데이터 수신 대기

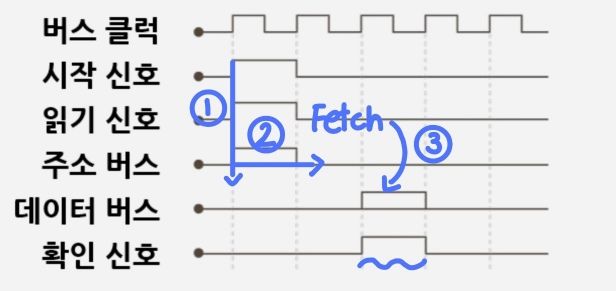

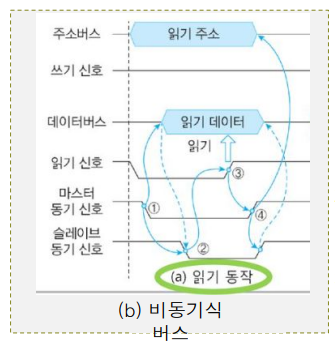

▷ 버스 동작 타이밍

사이클들은 타이밍에 의해 분류가 된다.

- 동기식 버스

- 버스 클럭 주기를 기준으로 발생

① CPU가 주소와 읽기 신호를 기억장치로 보냄

② 기억장치에서 데이터 인출

③ 데이터를 버스를 통해 CPU로 전송하는 동시에, 전송 확인 신호 보냄

=> CPU가 전송확인신호를 받고, "요청한 데이터가 버스에 실려있다" 라는 것을 알 수 있게 된다.

- 버스 클럭 주기를 기준으로 발생

-

비동기식 버스

-

동일한 시간이 아닌, 다른 버스의 동작 발생 여부에 따라 눈치 보면서 실행

-

MSYN(마스터 동기신호), SSYN(슬레이브 동기신호)라는 정보가 필요하다.

① CPU가 버스에서 읽기 주소, 읽기 신호 띄어놓고, 신호 안정 시 마스터동기신호 내보냄

② 기억장치・입출력장치가 버스 상의 읽기 데이터 출력, 신호가 안정되면 슬레이브동기신호 내보냄

③ CPU가 데이터를 읽어오고 읽기가 완료되면 읽기 주소, 읽기 신호, 마스터동기신호 제거, 주소버스에 알려줌

④ 기억장치・입출력장치는 버스 상의 읽기 데이터, 슬레이브동기신호를 제거해 전송 완료 -

장점

- 낭비되는 시간이 없다.(주기마다 이루어지지 않으므로)

-

단점

- 회로가 복잡하다.

- 회로가 복잡하다.

-

▶ 버스 중재 방식

버스 중재가 왜 필요할까?

버스 마스터는 한 순간에 하나의 버스 마스터만 시스템 버스를 사용할 수 있기 때문이다!

- 시스템 버스

- 구성요소들 서로간의 정보를 주고받는 통로를 시스템 버스라고 한다.

- CPU, 주기억장치, 모니터, 키보드, 프린터, 캐시의 작동은 전부 시스템 버스를 통해서 작동이 된다.

- 이 시스템 버스의 종류에는 3가지(데이터 버스, 주소 버스, 제어 버스)가 존재한다.

- 버스 마스터

- 시스템 버스에 접속되는 요소들 중에서 이러한 버스 사용의 주체가 되는 요소들을 말한다.

- 버스 마스터들은 한 순간에 한 개의 버스 마스터만 시스템 버스를 이용할 수 있어 버스 중재를 해줘야한다.

- ex. CPU, 기억장치 모듈, I/O 제어기 등

- 버스 경합

- 버스 요청이 동시에 두 개 이상 요청되었을 때 발생

- 두 개 이상의 버스 마스터가 동시에 버스 사용을 위해 경쟁하는 상황

- 버스 중재

- 버스 경합 해결 방안

- 버스 중재(버스 우선순위 정함)를 위한 신호선들의 집합

- 버스를 중재하기 위해서는 3가지 신호가 필요로 한다.

- 버스 중재 신호

- 버스 요청 신호 (BREQ, Bus Reguest)

- 버스 사용을 요구하는 신호

- 버스 승인 신호 (BGNT, Bus Grant)

- 버스 요구를 요청한 마스터에게 사용을 승인하는 신호

- 버스 사용 중 신호 (BBUSY, Bus Busy)

- 현재 버스가 사용되고 있는 중임을 나타내는 신호, 해제되는 순간부터 버스 사용 가능, 다른 마스터가 사용 못하도록 마스터가 버스 사용하는 순간에 셋트해야한다.

- 현재 버스가 사용되고 있는 중임을 나타내는 신호, 해제되는 순간부터 버스 사용 가능, 다른 마스터가 사용 못하도록 마스터가 버스 사용하는 순간에 셋트해야한다.

- 버스 요청 신호 (BREQ, Bus Reguest)

- 버스 중재 방식의 종류

제어 신호들의 연결 구조에 따른 중재 방식의 분류

| 병렬 중재방식 | 직렬 중재방식 | |

|---|---|---|

| 특징 | 각 버스 마스터들이 독립적 버스 요구, 버스 승인 신호 발생하고, 버스 승인 신호를 받는다. 버스 마스터마다 Request(BREQ), Grant(BGNT) 선이 각각 존재한다. ( 버스 마스터들의 수 = BREQ 선 및 BGNT 선) 마스터마다 나 쓸래~ 어 너 써~ 하는 신호가 있다. | 버스 요구와 승인 신호 선이 각각 한 개씩만 존재하며, 각 신호 선을 버스 마스터들 간에 직렬로 접속하는 방식 |

- Daisy-Chain이란 연속적으로 연결되어 있는 하드웨어 장치들의 구성을 지칭 (A는 B와 B는 C와 연결)

버스 중재기의 위치에 따른 분류

| 중앙집중식 중재 방식 | 분산식 중재 방식 | |

|---|---|---|

| 특징 | 중재기 개수 한 개 모든 버스 마스터들이 하나의 버스 중재기에 접속한다. | 중재기 개수 여러 개 모든 버스 마스터마다 중재기 존재한다. |

| 장점 | 분산식의 단점이 장점 | 중재 회로가 간단 -> 동작 속도가 빠름 어떤 중재기가 고장이 나더라도 해당 마스터에만 영향 -> 신뢰도가 높음 |

| 단점 | 분산식의 장점이 단점 | 고장을 일으킨 중재기를 찾아내는 방법이 복잡 한 중재기의 고장이 전체 시스템의 동작에 영향을 줄 수도 있음 |

우선순위의 결정 방식에 따른 분류

| 고정-우선순위 방식 | 가변-우선순위 방식 | |

|---|---|---|

| 특징 | 각 버스 마스터에 지정된 우선순위가 고정되어 있는 방식 | 시스템의 상태에 따라 버스 마스터들의 우선순위를 변경할 수 있는 방식 |

| 장점 | 중재 회로 단순 | 모든 마스터들이 공평하게 버스 사용 가능 → Starvation 방지 |

| 단점 | Starvation 발생 | 중재 회로 복잡 |

▷ 병렬 중재 방식

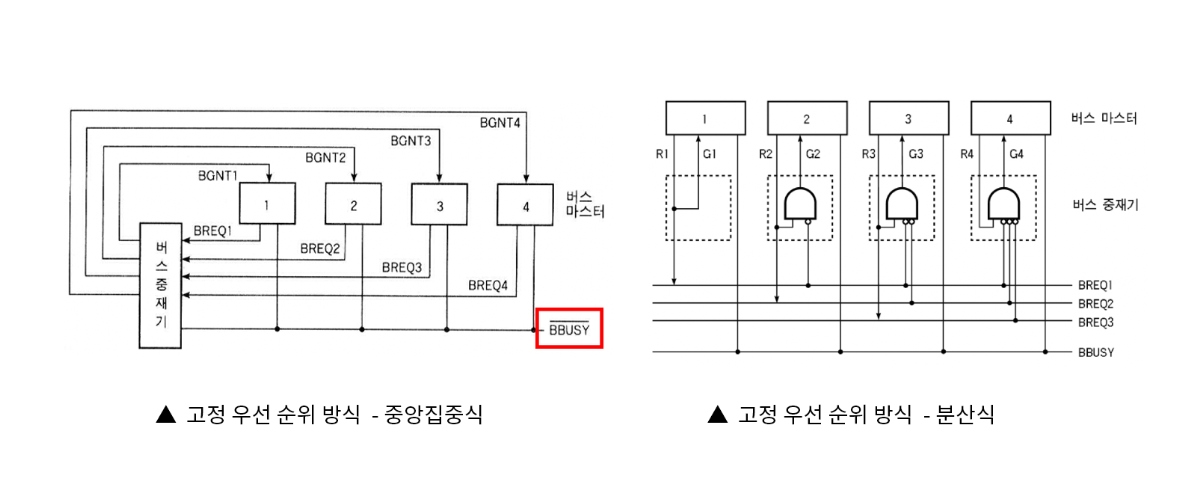

① 고정 우선 순위 방식 (중앙, 분산)

- 고정 우선 순위 방식

- 특징 : 우선순위가 높은 마스터가 BREQ를 보낸 상태일 때 우선순위가 상대적으로 낮은 마스터는 BGNT신호를 세트할 수 없다. 따라서 BBUSY 신호를 검사하여 해제된 상태일 때 버스 사용을 시작한다.

- 단점 : starvation 발생하여 불공평하게 버스 사용한다.

| 종류 | 중앙집중식 - 병렬 | 분산식 - 병렬 |

|---|---|---|

| 구성 | 모든 버스 마스터들이 하나의 버스 중재기에 접속된다. 중재기에 가까울수록 높은 우선순위를 가진다. (버스 마스터 1이 가장 높고, 버스 마스터 4가 가장 낮은 우선순위) | 모든 버스 마스터마다 중재기를 한 개씩 갖는다. |

| 동작 원리 | ① 여러개의 버스 요구 신호를 받은 후, 우선순위가 가장 높은 버스 마스터에게 BGNT 신호를 세트해준다. ② 그 후 BGNT 신호를 받는 마스터는 BBUSY 신호가 세트되어있는 동안에는 기다렸다가, 해제되는 순간 버스 사용을 시작한다. ③ 그 마스터는 버스 사용을 시작하는 순간 BBUSY 신호를 세트하여 다른 마스터가 버스를 사용하지 못하게 막는다. | 각 중재기가 자신보다 우선순위가 높은 마스터들의 BBUSY 신호를 검사하여 없다면 본인이 BGNT 신호를 세트하여 버스를 사용한다. |

| 예시 | Request(BREQ)신호를 1번, 2번, 3번, 4번 버스 마스터에서 각각 보내면 버스 중재기에 정해진 중재 원칙에 따라 중재기가 한 개만 허용(BGNT)해준다. | 첫 번째 마스터는 BREQ한다음 바로 BGNT 받아 실행하면 된다. 두 번째 마스터는 1번 마스터의 BREQ의 값을 받아와 연산하고 수행 세 번째, 네 번째 마스터도 마찬가지! |

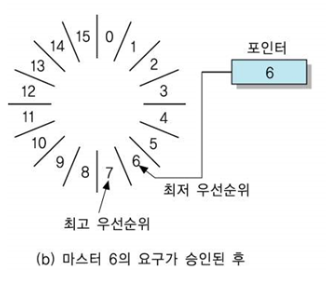

③ 가변 우선순위 방식 (회전, 동등, 최소 최근)

| 종류 | 회전 우선 순위 | 동등 우선 순위 | 최소 최근 사용 |

|---|---|---|---|

| 구성 | 버스 사용 승인을 받은 마스터는 최하위 우선순위, 다음 마스터가 최상위 우선순위를 갖는다. | 모든 마스터가 동등한 우선순위를 갖는다. FIFO알고리즘을 사용하여 먼저 요청한 거부터 grant해준다. | 오랫동안 버스 사용을 보내지 않은 버스 마스터 순으로 우선순위 할당한다. |

| 예시 | 마스터 6의 요구가 승인된 후 -> 최저 우선순위를 갖게 된다. | - | - |

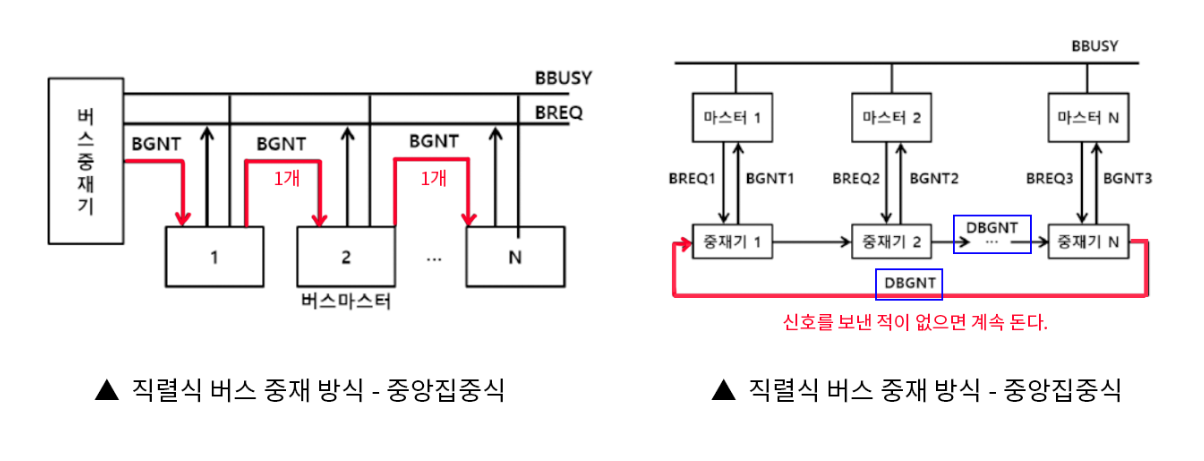

▷ 직렬 중재 방식 (중앙, 분산)

| 종류 | 중앙집중식 - 직렬 | 분산식 - 직렬 |

|---|---|---|

| 구성 | ① 하나의 중재 신호선(BGNT)이 모든 마스터들을 직렬로 연결(Daisy-Chain)하여 접속한다. ② BGNT가 연결된 순서로 우선순위를 결정한다. | 데이지-체인 버스 승인 신호인 DBGNT가 순환형(circular)으로 접속된 형태를 이룬다. |

| 동작 원리 | ① 한 개 이상의 마스터에서 버스 사용을 요구하면 공통의 BREQ 신호가 세트된다. ② 버스 중재기는 데이지체인의 첫 번째 마스터로 BGNT를 전송한다. ③ 첫 번째 마스터가 요청 신호를 보냈으면 BBUSY 신호를 세트하고, 아니면 다음 버스 마스터로 BGNT 신호를 넘겨준다. 이런 식으로 버스 사용을 요구한 마스터를 찾아다닌다. | ① 버스 사용권을 부여 받은 마스터가 버스 사용을 시작하는 순간에 (그 마스터의 중재기는) 자신의 우측에 위치한 마스터의 중재기로 접속된 DBGNT 신호를 세트한다. ② 만약 그 마스터가 버스 사용을 신청하고 기다리던 중이었다면, 중재기는 즉시 DBGNT 신호를 받아들여서 BGNT 신호를 발생시켜 마스터로 전송한다. ③ DBGNT 신호를 받은 마스터가 버스 요구를 하지 않은 상태라면, 그 신호를 우측의 다음 중재기로 통과시키고, 버스를 요구한 마스터를 찾아 낼 때까지 반복한다.(너가 요청했니? 계속 물어보면서 찾음) |

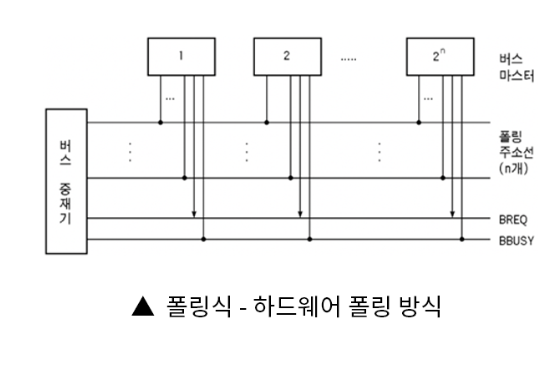

▷ 폴링 방식 (H/W, S/W)

- 버스 사용을 원하는 마스터가 있는지를 버스 중재기가 주기적으로 검사하여 사용 승인 여부를 결정하는 방식을 말한다.

- 주기적으로 너 버스 쓸래? 하고 물어보는게 폴링식이다.

| 종류 | 하드웨어 폴링 방식 | 소프트웨어 폴링 방식 |

|---|---|---|

| 구성 | 버스 중재기와 각 버스 마스터 간의 폴링 선이 존재한다. (공통 BREQ, BBUSY선이 한 개씩 존재) 폴링순서ㆍ중재 동작이 중재기 내부에 H/W로 고정되어있다. | 폴링 순서와 과정이 하드웨어에 내장되어있지 않는 폴링 방식을 말한다. |

| 동작 원리 | ① 중재기는 폴링 주소를 발생하여 검사할 마스터를 지정한 다음에, 그 마스터가 버스 사용을 원하는지 묻는다. ② 지정된 마스터가 버스 사용을 원하면 BGEQ 신호를 세트한다. ③ BREQ 신호가 세트되면, 중재기는 현재 검사중인 버스 마스터에게 버스 사용을 허가하고, 그렇지 않으면 다음 마스터들에 대한 검사를 순서대로 진행한다. | 장점 : 폴링 순서(우선순위)변경이 용이하다. 단점 : 프로그램을 실행해야 하므로 하드웨어 방식에 비하여 속도가 더 느리다. 이와 같은 장단점은 폴링 방식에만 국한되는 것이 아닌, H/W와 S/W의 차이이다. |

| 과정 | ① 중재기는 폴링 주소를 발생하여 검사할 마스터를 지정한 다음에, 그 마스터가 버스 사용을 원하는지 묻는다. ② 지정된 마스터가 버스 사용을 원하면 BREQ 신호를 세트 ③ BREQ 신호가 세트되면, 중재기는 현재 검사중인 마스터에게 버스 사용을 허가하고, 그렇지 않으면(지정된 마스터가 버스 사용을 원하지 않으면) 다음 마스터들에 대한 검사를 순서대로 진행 마스터들에 대한 검사 순서는 정하기 나름이다. | - |

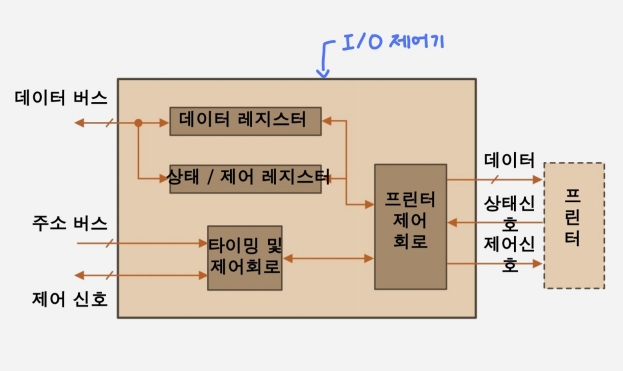

▶ 데이터 입출력 방식

-

I/0 장치는 시스템 버스에 직접 접속되지 못하는 이유

- 장치 종류에 따라 제어 방법이 서로 다름

- 데이터 전송 속도가 CPU의 데이터 처리 속도에 비해 훨씬 느리다.

=> 따라서 I/O 컨트롤러를 사용한다.

▷ I/O 주소 지정 방법

- I/O가 직접적으로 CPU와 연결되는 것이 아닌, I/O 컨트롤러 내부의 레지스터의 주소 값을 이용하여 연결되게 된다.

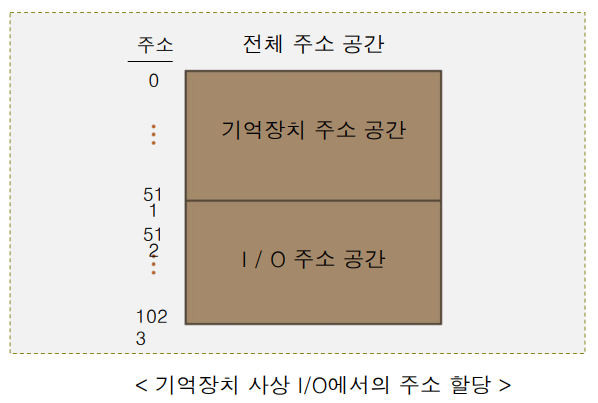

① 기억장치 - 사상 I/O

- 개념

- 기억장치 주소 영역의 일부분을 I/O 제어기 내의 레지스터들의 주소로 할당하는 방식

- 간단히 "기억장치 주소를 나눠쓰는 방식!" 이라고 알고 있자.

- 장점

- LOAD, STORE 등 기억장치 접근 명령어들을 I/O 장치에도 사용 가능하여 프로그래밍 용이

- I/0에 접근하기 위한 별도의 명령어 필요 없이, 메모리에 접근하는 명령어만 사용해도 되기 때문

- LOAD, STORE 등 기억장치 접근 명령어들을 I/O 장치에도 사용 가능하여 프로그래밍 용이

- 단점

- 나눠쓰게 되므로 기억장치 주소 공간이 감소한다.

- 나눠쓰게 되므로 기억장치 주소 공간이 감소한다.

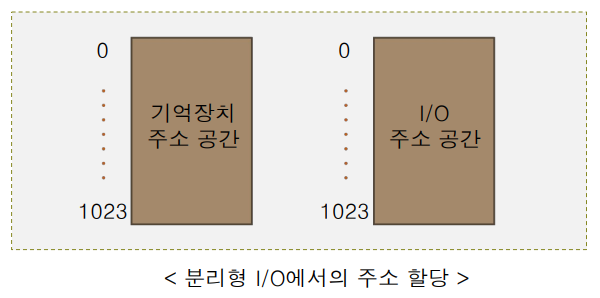

② 분리형 I/O

- 개념

- I/O장치 주소 공간을 기억장치 주소 공간과는 별도로 할당하는 방식

- 장점

- 기억장치 주소 공간이 줄어들지 않는다.

- 단점

- LOAD, STORE 등으로 기억장치에 접근할 수 없어 I/0 제어를 위해 별도의 I/0 명령어를 사용해야한다. (프로그래밍 복잡해짐)

- LOAD, STORE 등으로 기억장치에 접근할 수 없어 I/0 제어를 위해 별도의 I/0 명령어를 사용해야한다. (프로그래밍 복잡해짐)

▷ 데이터 입출력 방식

① 프로그램에 의한 입출력 방식(폰 노이만)

- 개념

- CPU가 주기적으로 I/O 상태 검사하면서 I/O 동작을 처리한다.

- 장점

- 간단하며, 별도의 하드에어가 필요하지 않는다.

- 단점

- CPU가 I/O 동작에 직접 관여해야하므로 I/O 동작이 진행되는 동안 CPU에 유휴 시간 발생!

- 과정

- 상태 레지스터(I/0 상태와 오류 검사), 제어 레지스터 존재

- CPU가 프린터로 데이터를 출력하는 과정

① CPU가 프린터 상태 검사 요청

① CPU가 프린터 상태 검사 요청

② 제어기가 프린터 상태 검사하여 CPU에게 통보 (데이터를 출력할 준비 되었는지, 다른 데이터 출력중인지)

③ 데이터 출력할 준비가 되었으면 CPU가 제어기에게 출력 명령(제어 레지스터로)과 데이터(데이터 레지스터로) 전송

④ 제어기가 프린트 동작을 위한 제어 신호와 함께 데이터를 프린터로 전송

② 인터럽트에 의한 입출력 방식

-

개념

- I/O 동작이 I/O 제어기와 I/O 장치에서 진행되는 동안 CPU는 다른 작업을 처리 → 유휴 시간 효율적으로 이용!

-

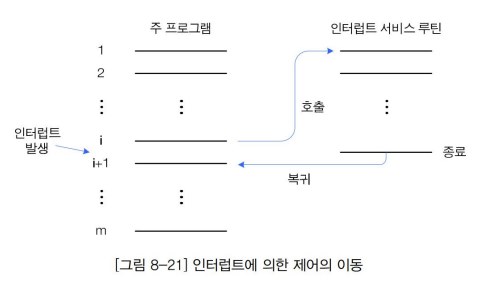

인터럽트

- i번째 명령 실행 중에 인터럽트가 발생했다면, 현재 실행 중인 i번째 명령 마친 후 레지스터 정보 저장하여 ISR에 맞춰 인터럽트 처리, 이후에 i+1번째 명령 수행.

- 인터럽트에 대한 자세한 개념은 "인터럽트" 포스팅을 참고하도록 하자!

- 종류

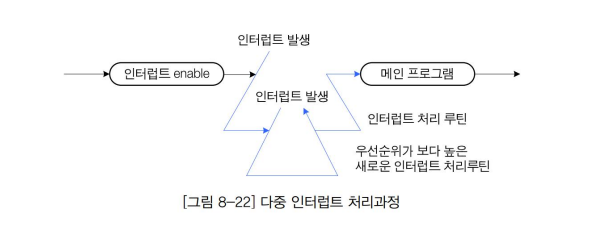

- 다중 인터럽트 방식

- 인터럽트 처리 중 우선 순위가 높은인터럽트가 들어온 경우, 그 인터럽트를 스택에 넣어두고 새로 들어온 인터럽트부터 처리하는 방식

- 인터럽트 처리 중 우선 순위가 높은인터럽트가 들어온 경우, 그 인터럽트를 스택에 넣어두고 새로 들어온 인터럽트부터 처리하는 방식

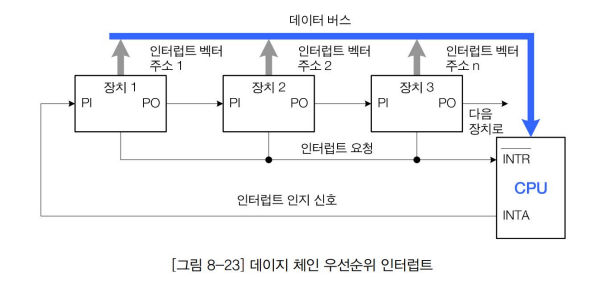

- 데이지 체인 방식 (직렬 우선순위 부여 방식)

- 인터럽트가 발생하는 모든 장치를 한 개의 회선에 직렬적으로 연결하며, 우선순위가 높은 장치를 맨 앞에 위치시키며 우선 순위에 따라 연결하는 방식

- 장점

- 하드웨어로 구현하기가 간단하다.

- 단점

- starvation 발생 가능

- starvation 발생 가능

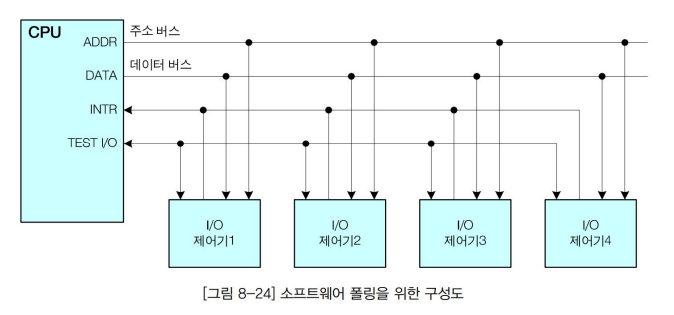

- 소프트웨어 폴링 방식

- 모든 I/O 제어기에 접속된 TEST I/O 선을 이용해 인터럽트 요구 장치를 검사하는 방식

- TEST I/O란?

- TEST I/O 신호는 인터럽트 플래그의 상태를 검사하는 데 사용한다.

- CPU에 INTR(인터럽트) 신호가 들어오면, TEST I/0를 통하여 각 제어기에 Flag 상태를 확인하여 어느 제어기에서 인터럽트 신호가 발생했는지 확인한다.

- 장점

- 우선 순위의 변경이 용이하다.

- 단점

- 처리 시간이 오래 걸린다.

- 처리 시간이 오래 걸린다.

- 다중 인터럽트 방식

- 인터럽트 vs 서브루틴

| 구분 | 인터럽트 | 서브루틴 |

|---|---|---|

| 개념 | 실행중인 프로그램을 잠시 중단하고 다른 프로그램을 먼저 실행하는 것 | 메인루틴에 대응되는 단어로, 프로그램 중의 하나 이상의 장소에서 필요할 때마다 반복해서 사용할 수 있는 부분적 프로그램 |

| 발생 과정 | 내ㆍ외부 신호에 의해 발생 | 프로그램 명령 실행 과정에서 발생 |

| 분기 주소의 결정 | 하드웨어의 의해 결정 | 소프트웨어에 의해 결정 (명령어 주소 필드에 의하여 결정) |

| 저장 값 | 인터럽트 발생 전의 레지스터 내용, PC 값 등 CPU 상태에 관한 모든 정보 저장 | PC값만 저장 |

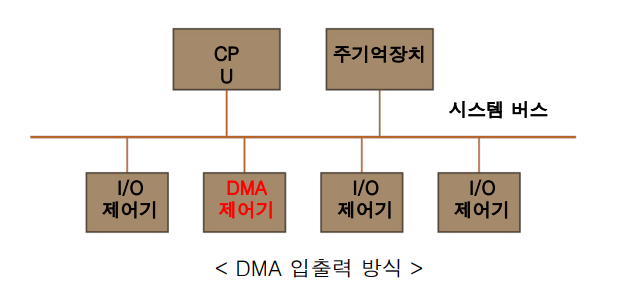

③ DMA에 의한 입출력 방식

- 개념

- CPU 개입 없이 I/O 장치와 기억장치 사이 데이터 전송하는 방식이다.

- CPU가 주기억장치를 액세스하지 않는 시간(CPU가 내부적으로 명령어를 해독하거나 ALU 연산을 수행하는 시간) 동안에 주기억장치가 I/O 장치가 소통하기 위해 DMA 제어기를 사용한다.

- DMA에 대해 더 자세히 알고 싶다면 클릭!

📎참조

- 『 성결대학교 김자원 교수님 』 - 컴퓨터 구조 (2023)

- 『 컴퓨터구조(제5판) 』 - 복두 출판사

- https://blog.naver.com/PostView.naver?blogId=sensecar5351&logNo=221679890641

- https://velog.io/@nayoon-kim/%EC%9A%B4%EC%98%81%EC%B2%B4%EC%A0%9C-%EC%9A%B4%EC%98%81%EC%B2%B4%EC%A0%9C-3%EC%9E%A5

- https://blog.naver.com/PostView.naver?blogId=stjdsmtjs&logNo=221656120236&parentCategoryNo=&categoryNo=48&viewDate=&isShowPopularPosts=false&from=postView

- https://pololove.tistory.com/75

- https://butter-shower.tistory.com/39

- http://contents.kocw.net/KOCW/document/2015/shinhan/leedonggyu/12.pdf