DDR SDRAM

SDRAM

동기식 DRAM (Synchronous DRAM)

DRAM의 액세스 속도 한계를 극복

DRAM의 한계

기억장치 액세스 동작이 연속적

CPU는 액세스의 시작~종료까지 기다려야 함

SDRAM의 극복

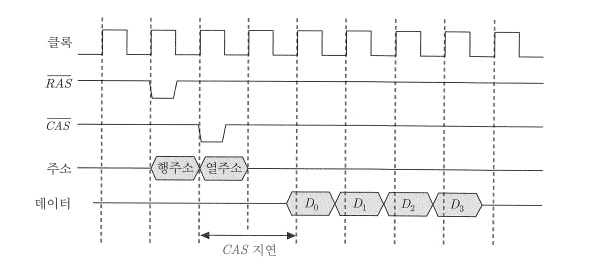

액세스 동작이 시스템 클록에 맞추어 (동기화) 수행

CPU가 결과를 기다리지 않고 다른 연산을 수행

뱅크

SDRAM은 액세스의 동시성을 향상시키기 위하여 여러 개의 뱅크로 구성됨

뱅크마다 서로 다른 주소에 대한 액세스 동작 수행

뱅크에서 행 주소와 열 주소를 통해 연속적인 바이트들이 버스에 실리게 된다. 비스트 모드

버스트 모드

액세스 시, 여러 바이트들을 연속적으로 전송

버스트 길이

버스트 모드에서 전송되는 바이트들의 수

CAS 지연

데이터가 인출되어 버스에 실릴 때까지의 시간

DDR SDRAM

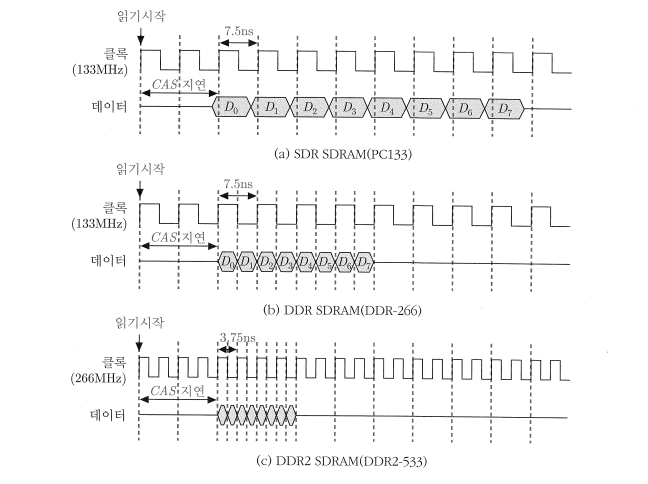

SDR SDRAM

Single Data Rate SDRAM

이전에 서술한 SDRAM

DDR SDRAM

Double Data Rate SDRAM

DDR SDRAM은 클록 주기 당 2번씩 데이터를 전송 (대역폭이 2배)

첫 번째 데이터를 클록의 상승 에지에서 전송,

두 번째 데이터를 클록의 하강 에지에서 전송.

DDR2 SDRAM

클록 주파수가 DDR SDRAM의 2배

기억장치 대역폭

CPU의 단위 시간 당 데이터 전송량

버스 폭 * 클록 주파수

김종현 저, 『컴퓨터구조론』, 생능출판, 2019.