나태했던 지난 날을 타파하고자 개인 프로젝트에 들어갔다

목표는 기존에 설계에 사용하였던 gaisler사의 SpaceFibre IP를 이용하여 CAN bus와 Processor를 구성해보는것이다.

https://www.gaisler.com/index.php/downloads/grlib

해당 링크에서 Source file을 다운로드 받았다.

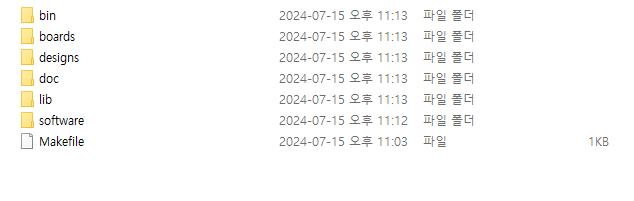

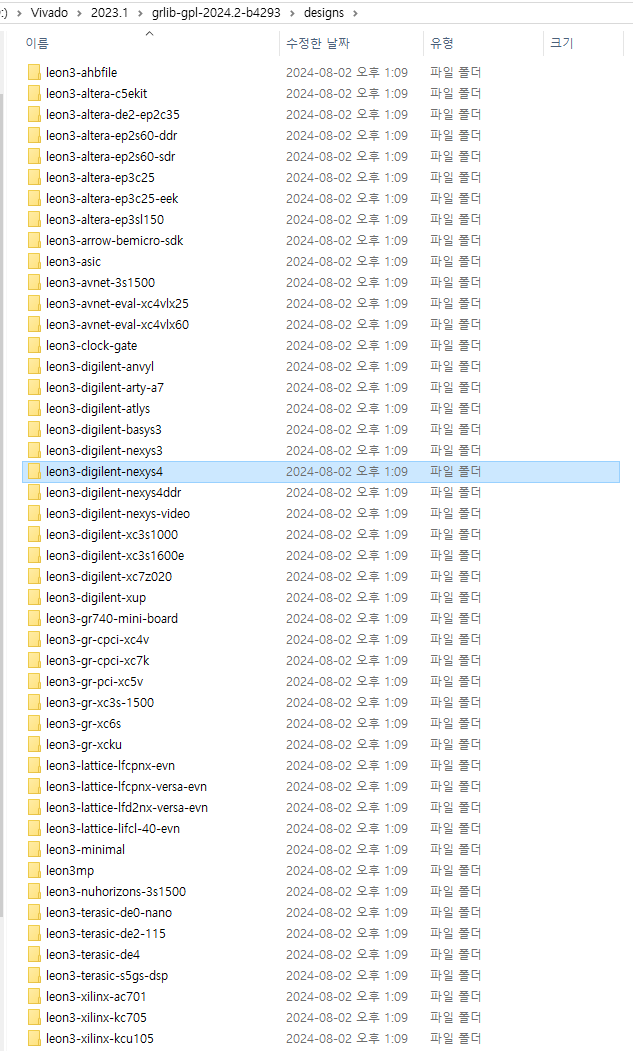

알집을 풀어보면 다음과 같은 구성을 볼 수 있다

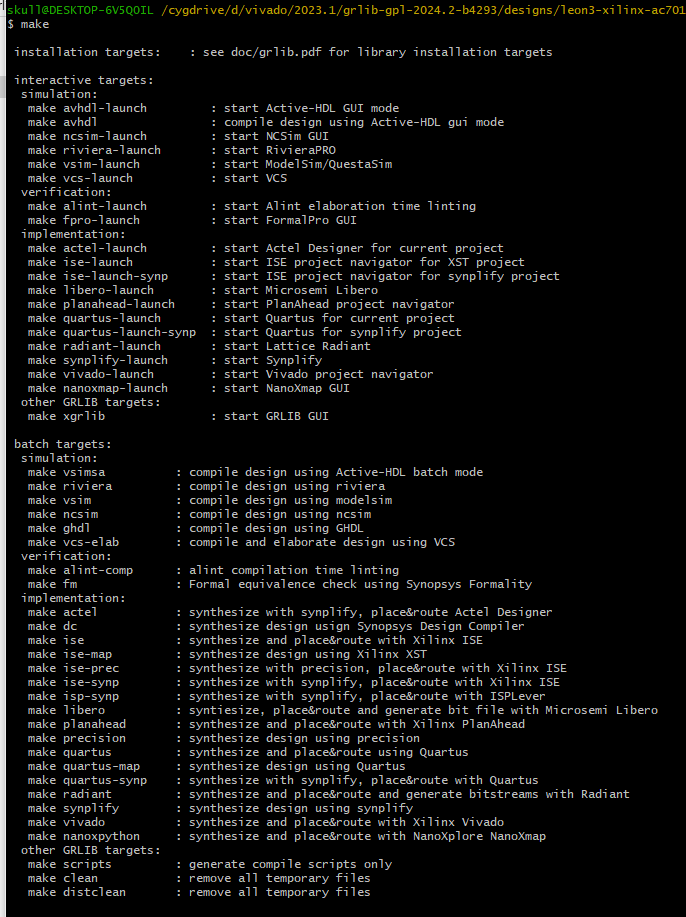

Makefile이 있는 것으로 볼때, 이전에 사용을 했던 cygwin64를 사용할 필요가 있어보인다.

cygwin64의 설치 방법은 찾아보면 많이 나온다.

https://m.blog.naver.com/datarget/222184659459

나는 위의 블로그를 참고하였다.

설치한 package는

automake

make

mingw64x86_64-gcc-core

mingw64x86_64-mpfr

mingw64x86_64-tk

Sharutils

Wget

x11 category 전체 설치

gcc-core

gcc-g++

위의 package들을 설치하였다

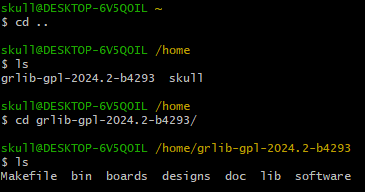

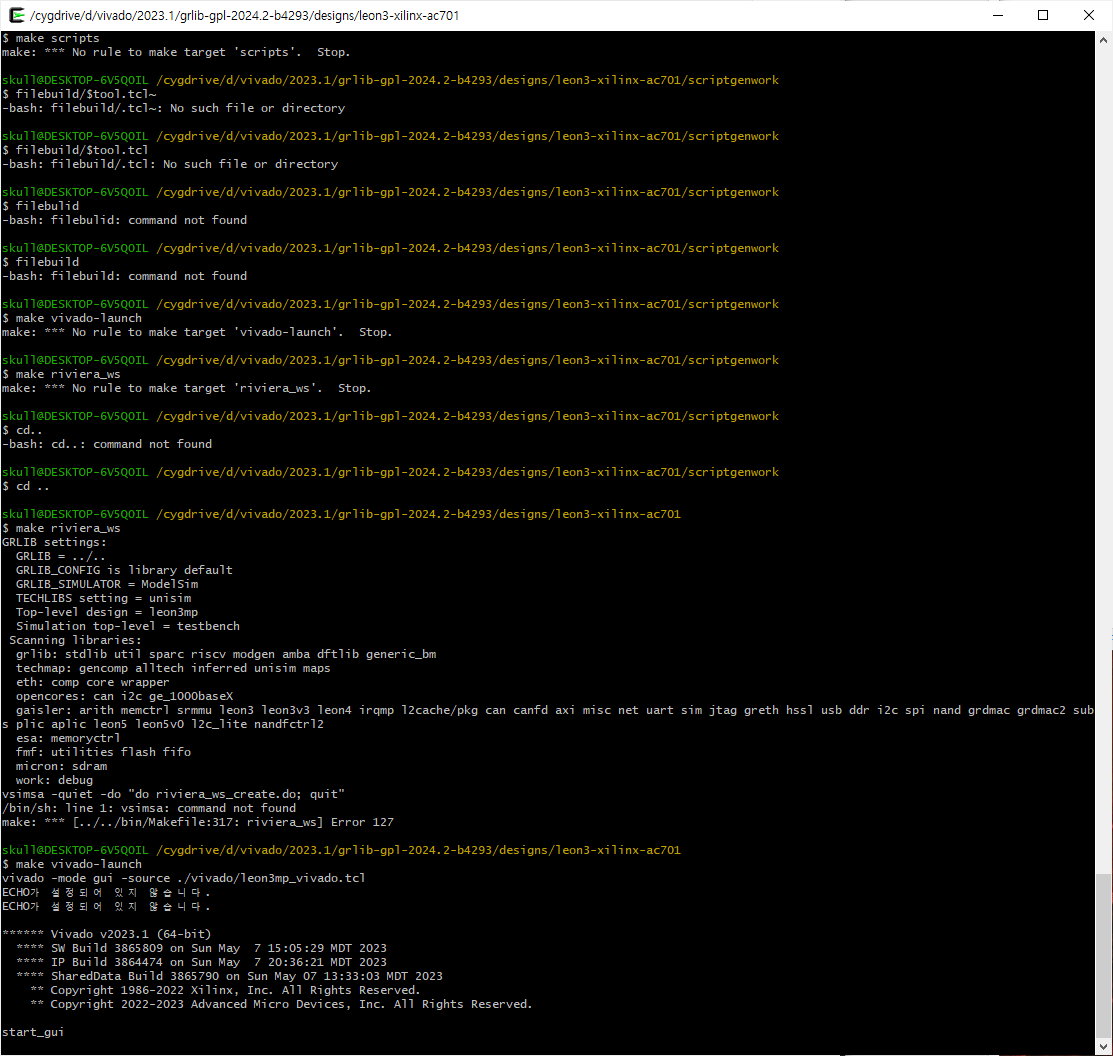

설치 후, cygwin64 terminal을 관리자 권한으로 켜고

home 경로로 이동 후

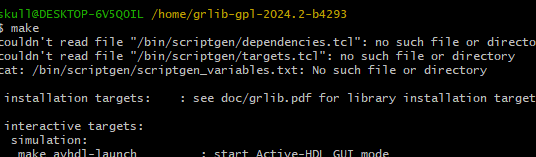

make를 수행하였다

뭐가 설치됐는지 잘 모르겠다.

installation target이 알려준 grlib.pdf를 확인해보자

Design 폴더에서 원하는 Design을 찾아보자

이 design 파일은 vivado 환경에서 돌아가는 듯하다

ahb2.0을 사용하며 Vivado를 지원

보니까 Vivado가 지원하는 디자인은 꽤있는듯하다

이 친구의 경우, CAN통신을 지원한다는데... 처음들어보는 보드인데다가 vivadod에서 지원을 해줄지...

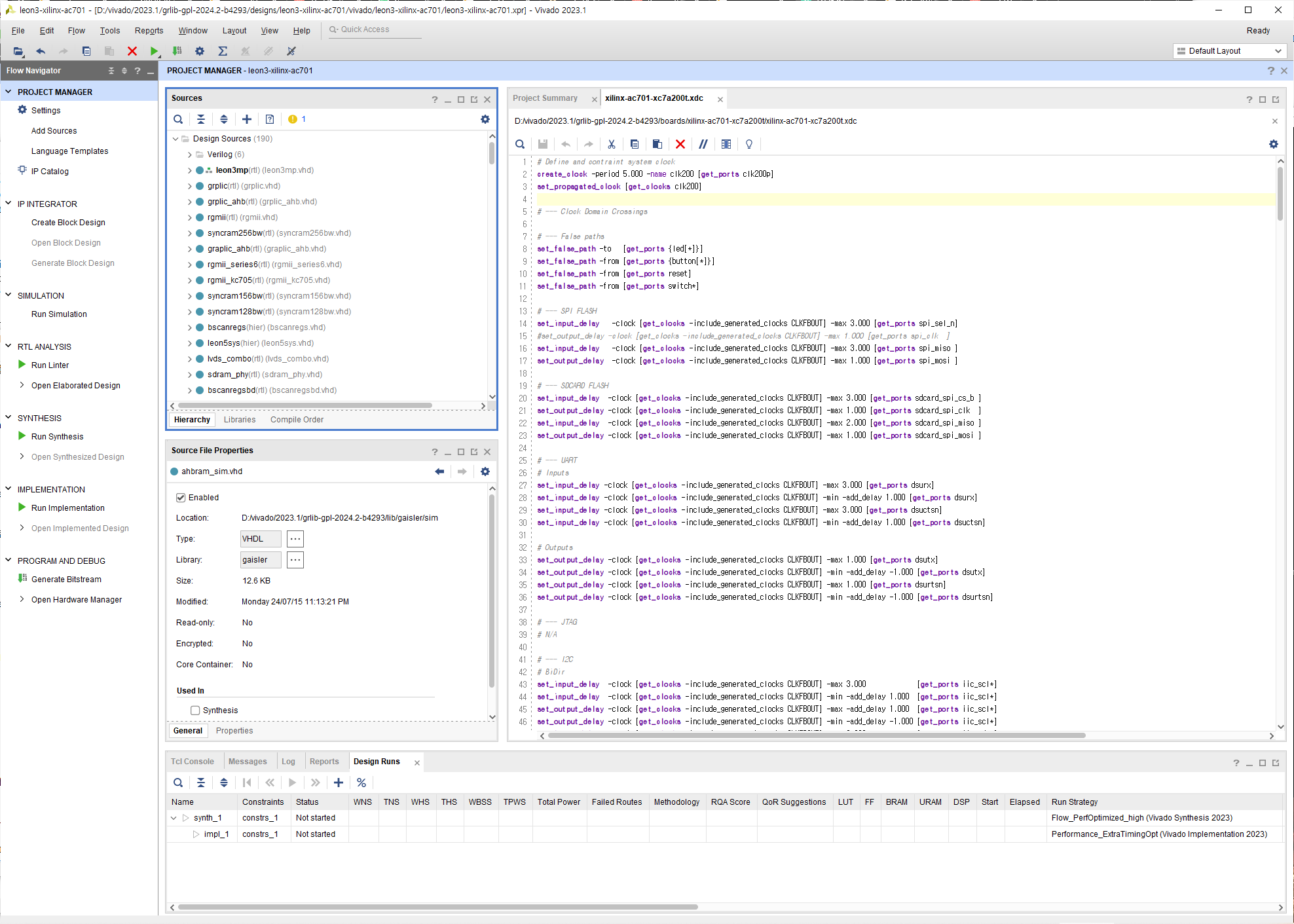

Vivado에 설치된 FPGA가 Artix-7 AC701 EValuation platform이기에 이걸로 해보기로 했다.

make 명령어 입력

파일이 하나 생성됐다

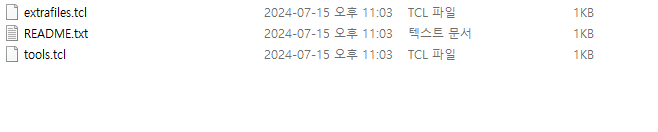

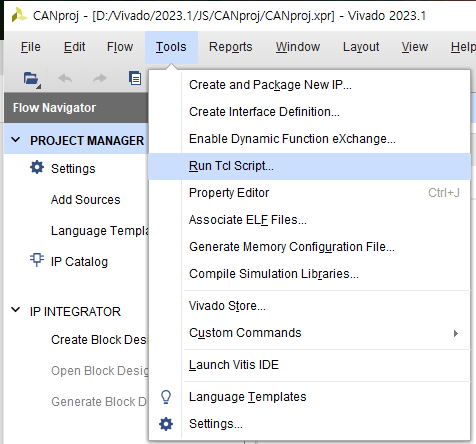

내부를 보면 .tcl파일들이 생성되었는데 어떻게 사용하는지 모르겠다

readme 파일을 보니

해당 위치의 Readme를 또읽으란다

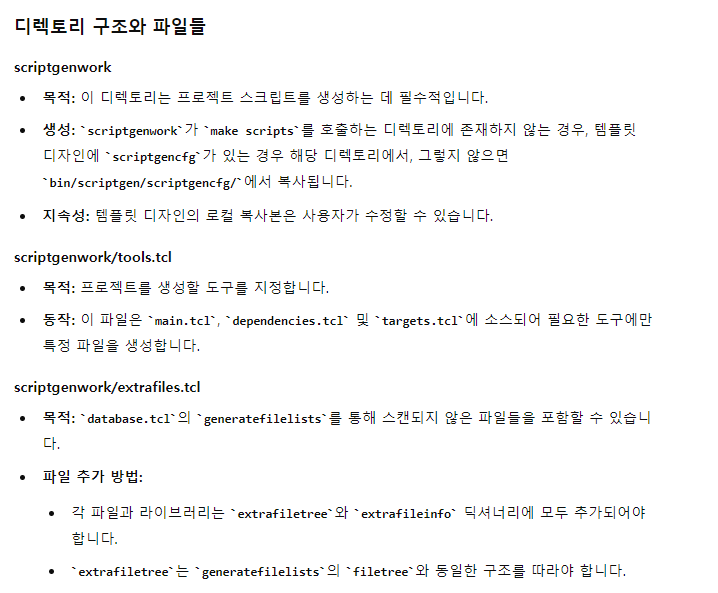

이렇다고 하는데 잘모르겠다...

https://www.youtube.com/watch?v=BXhLFecEPc8

이 유튜브를 참고해봤는데

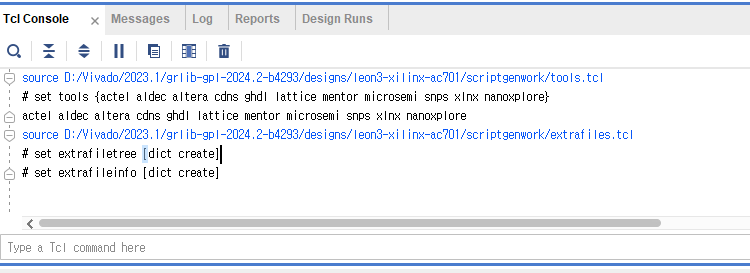

이런 결과가 나왔다... 뭐가 바뀐거지??

cygwin64로 make vivado-launch를 실행해 보았다

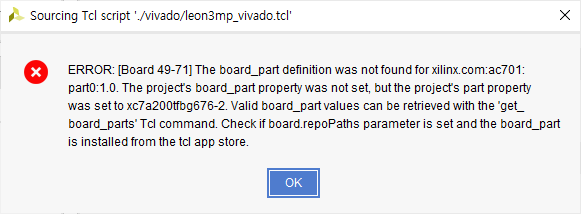

이렇게 에러가떴지만

뭔가 된것같다

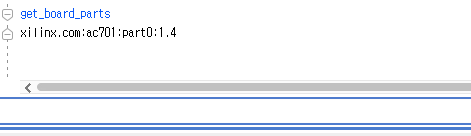

에러문에서 나온것처럼 get_board_parts를 입력하였다