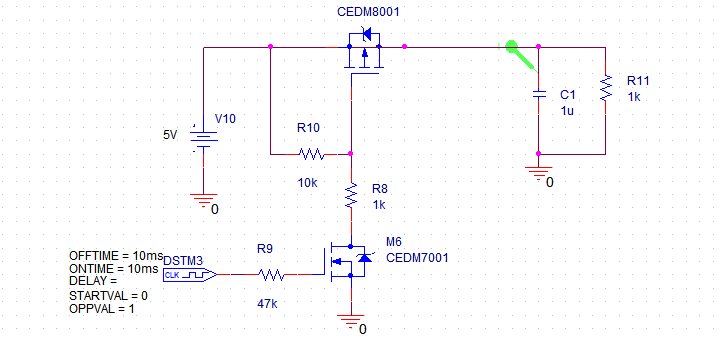

Implementation, Value -> 원하는 소자의 이름을 입력

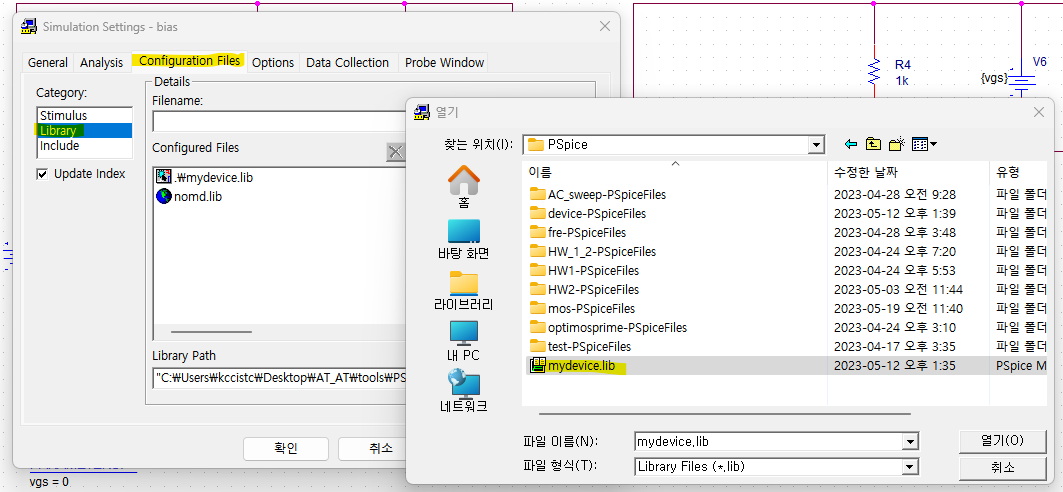

edit simulation profile -> Configuration Files -> Browse -> 추가할 라이브러리 경로 -> Add to Design

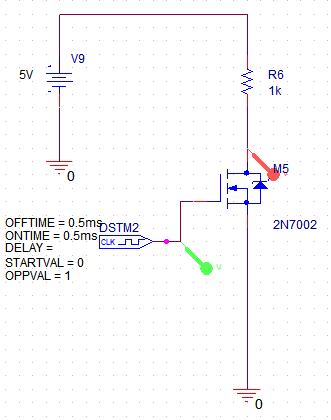

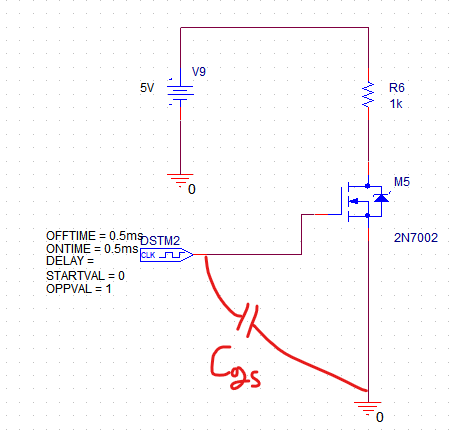

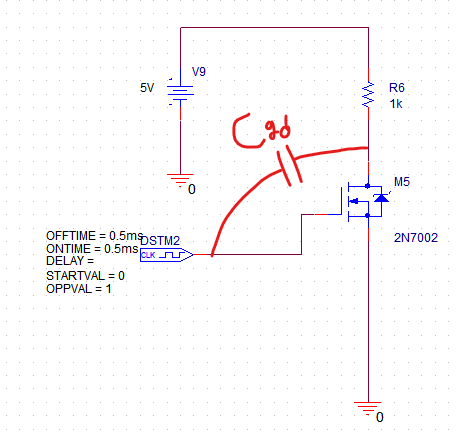

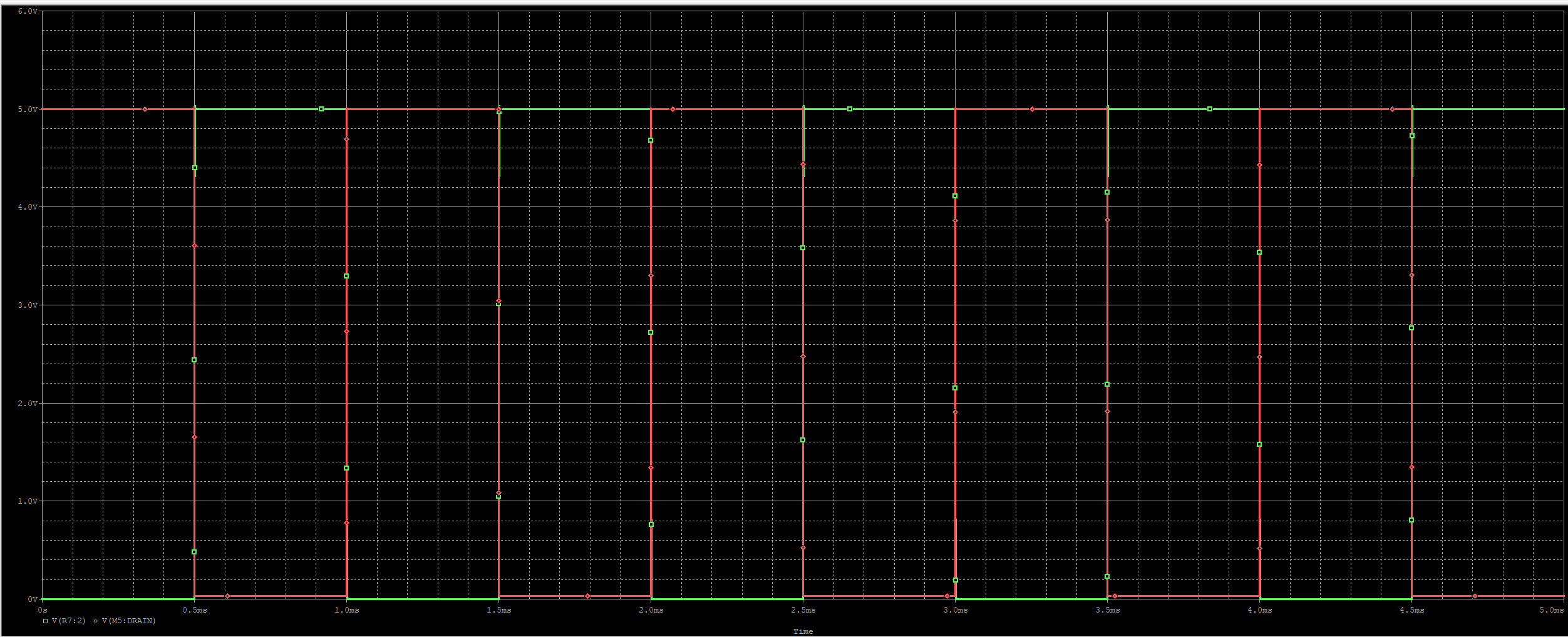

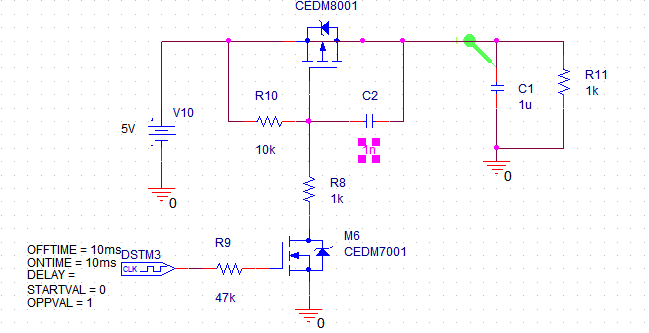

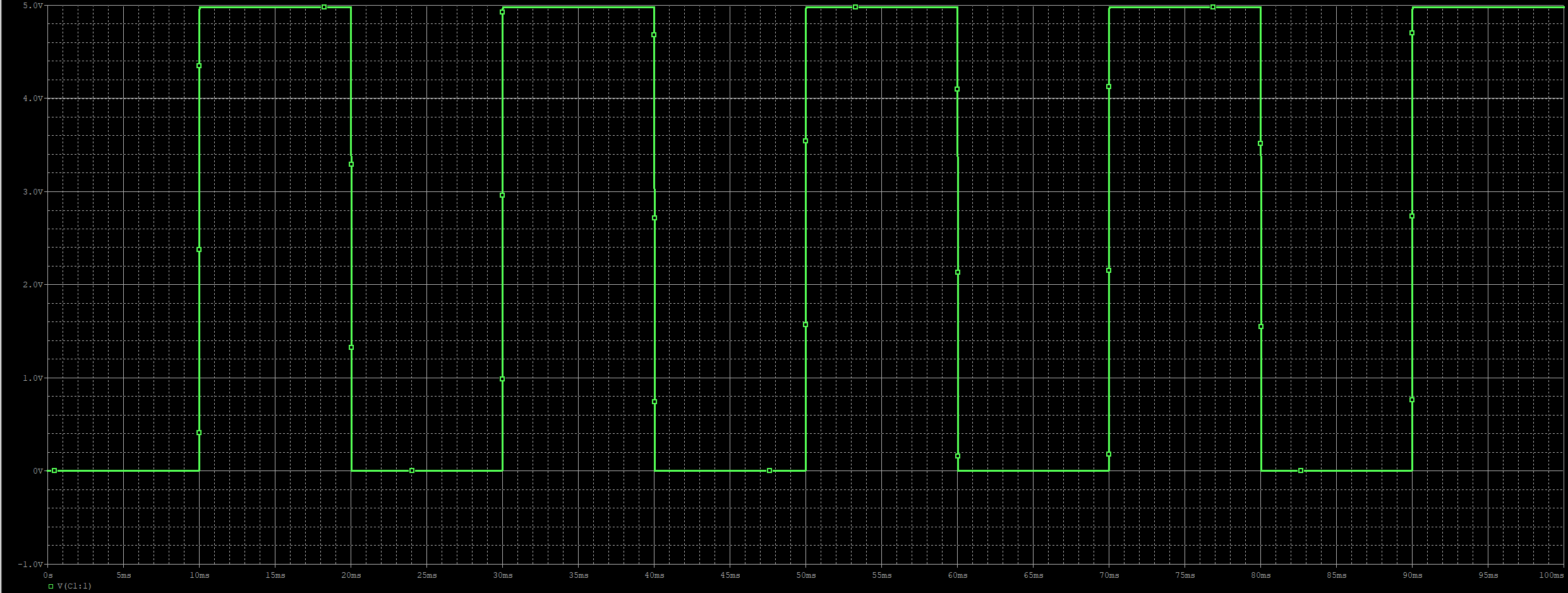

1ms의 주기의 clk를 주는 입력을 NMOS에 인가

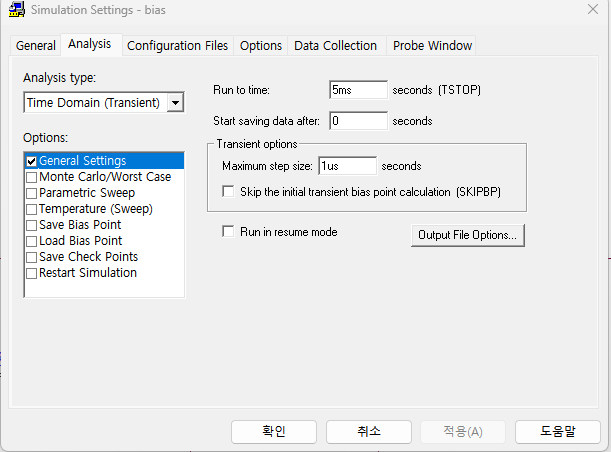

1ms주기를 5번 보기위해 5ms를 인가

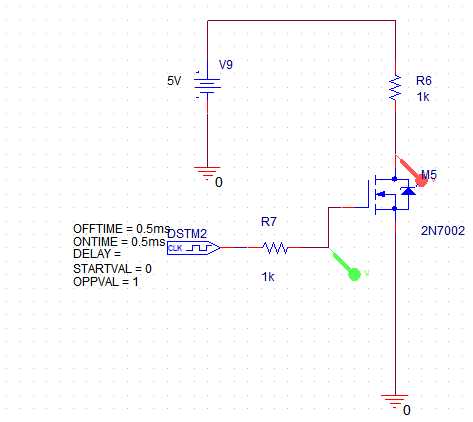

기생cap C_gs에 의해 rising falling edge에 큰 전압이 발생 -> 문제를 해결하기 위해 gate에 저항을 인가

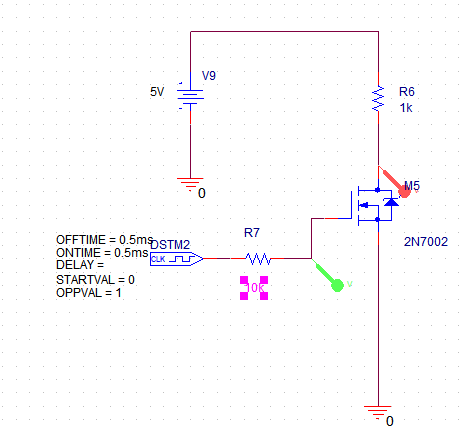

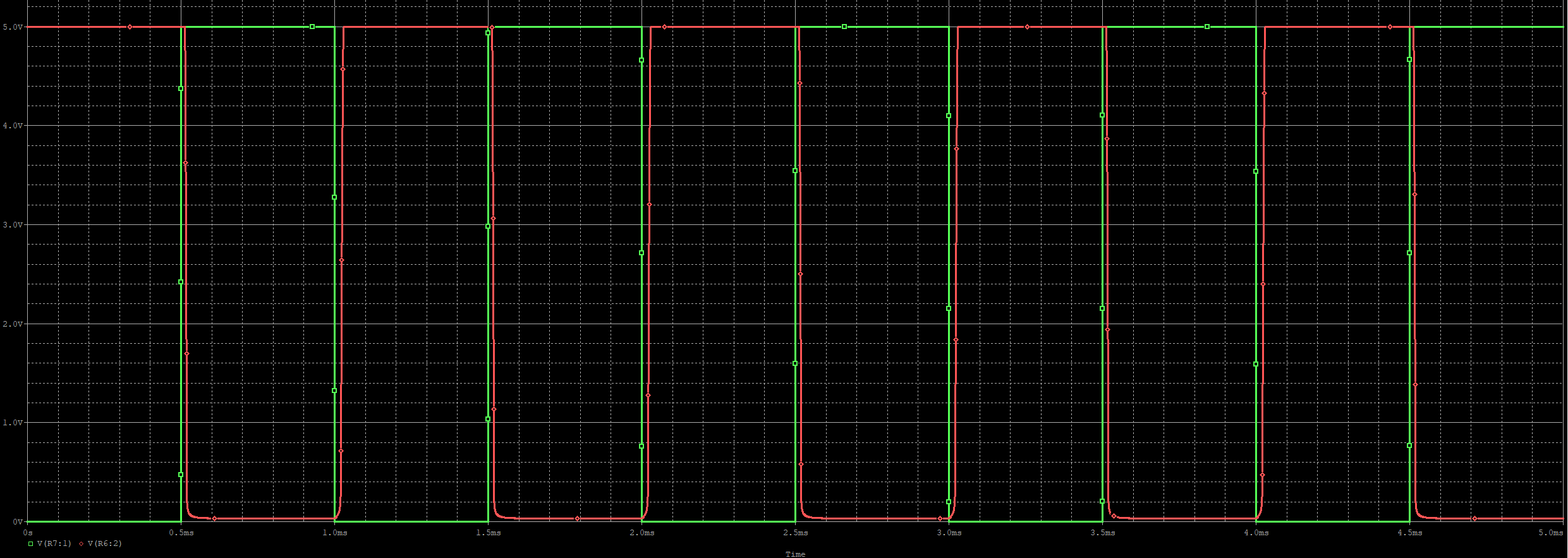

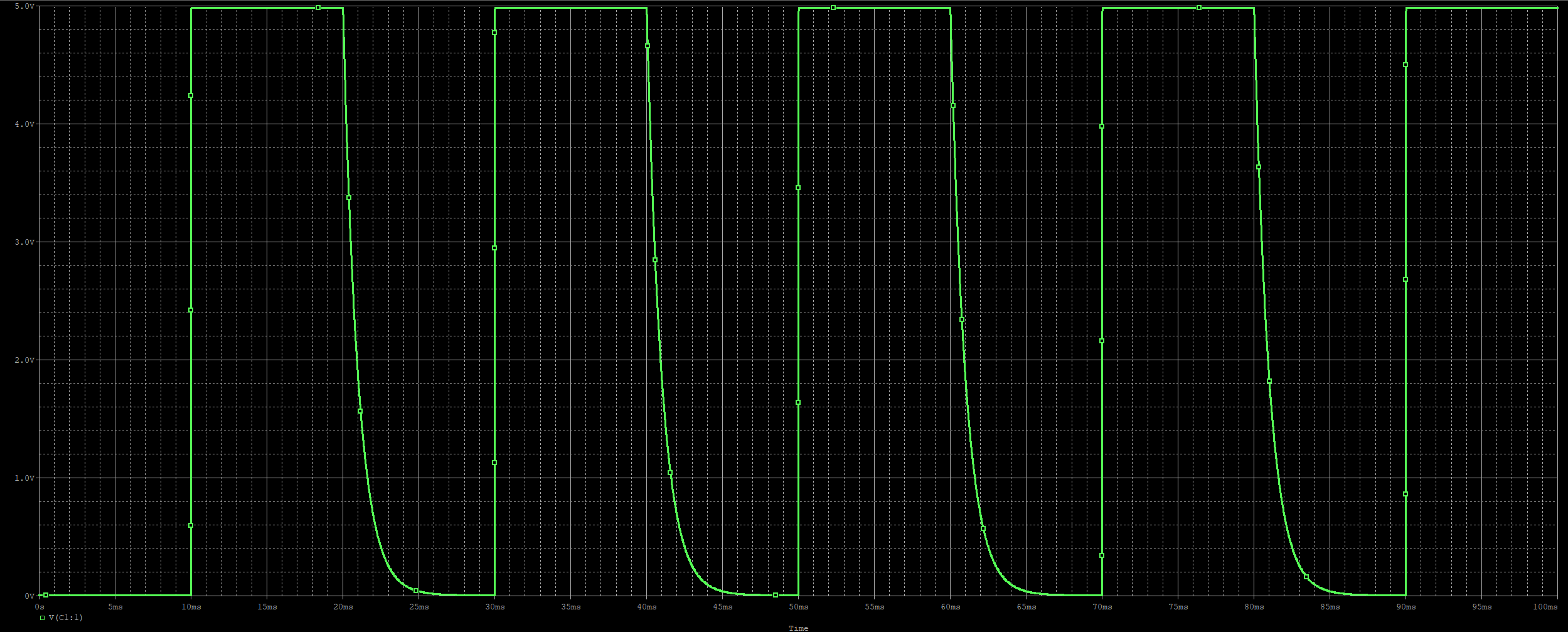

시정수가 커져 rising time과 falling time이 증가 -> dv/dt에서 dt가 증가 -> v가 상대적으로 작아짐 -> edge에서 크게 걸리는 전압이 작아짐을 볼 수 있음

저항을 10k로 하면 edge에서 튀는 전압을 크게 줄일 수 있다.

하지만 저항이 너무 클 경우, 입출력의 신호 타이밍이 어긋난다.

ESD에 의해 큰 전압이 입력으로 인가된 경우, 절연체가 파괴될 수 있음 -> 이때도 gate단에 저항을 달아주어 해결한다.

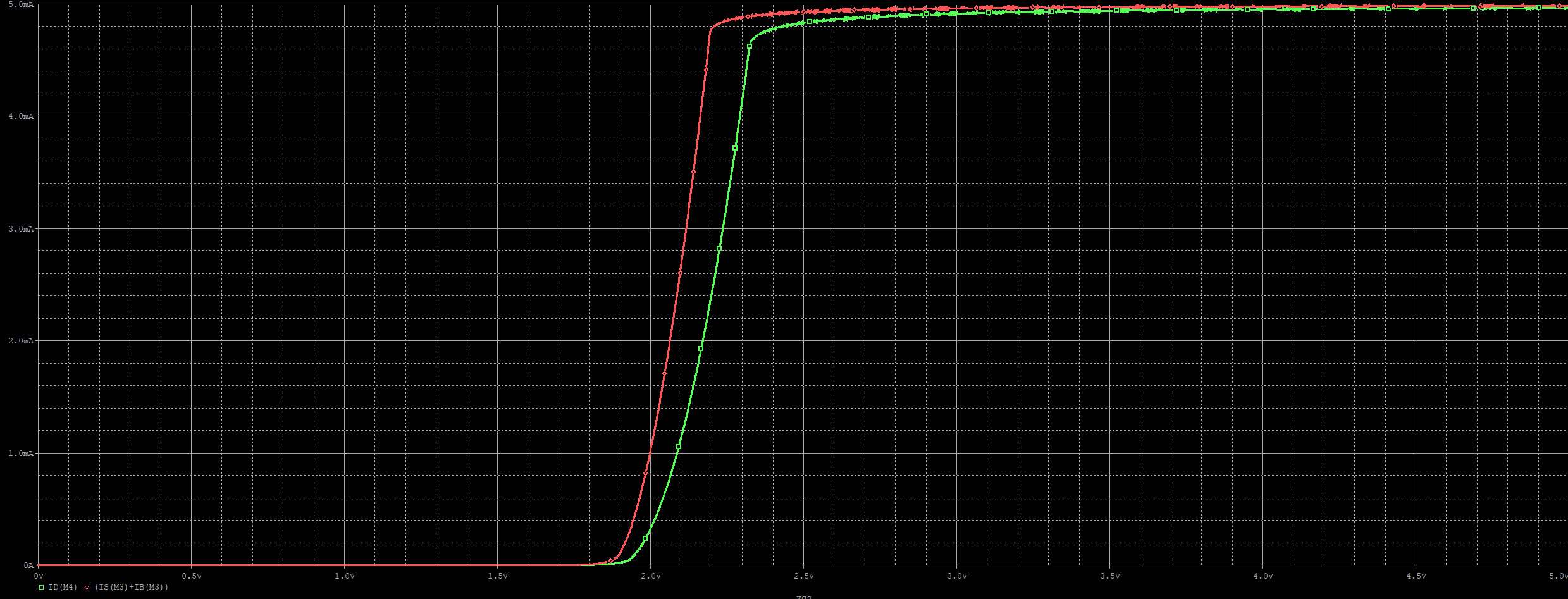

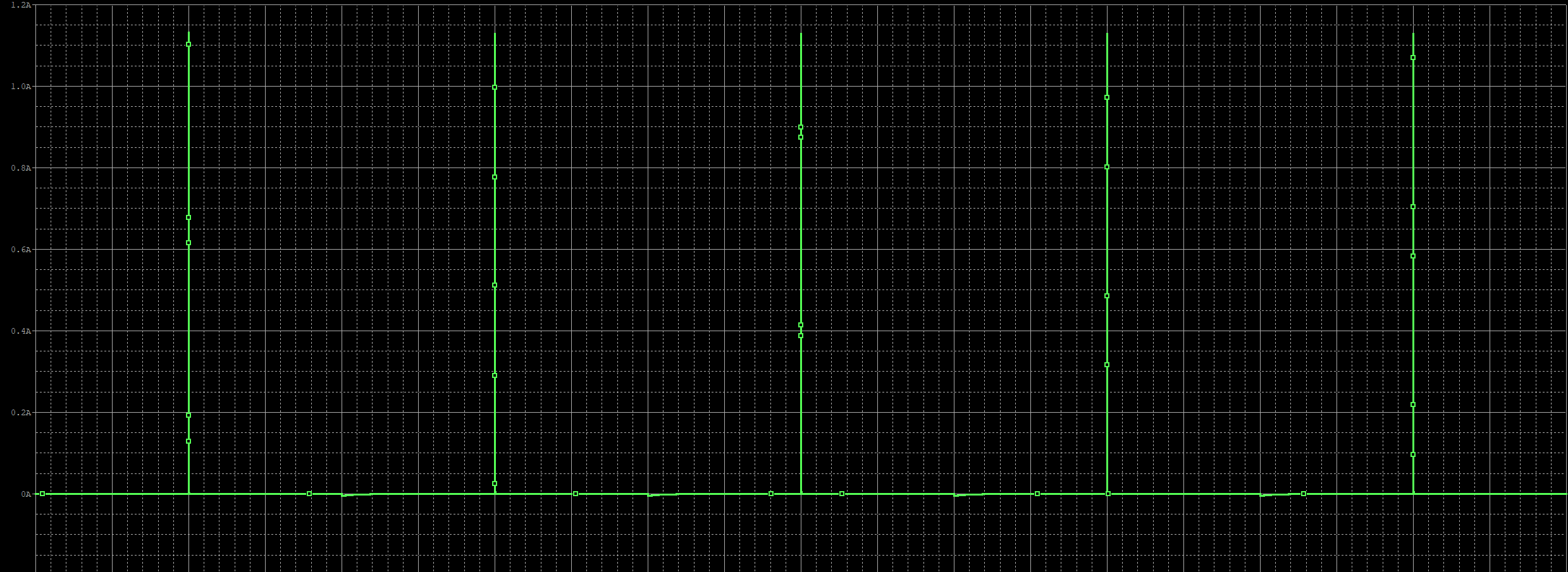

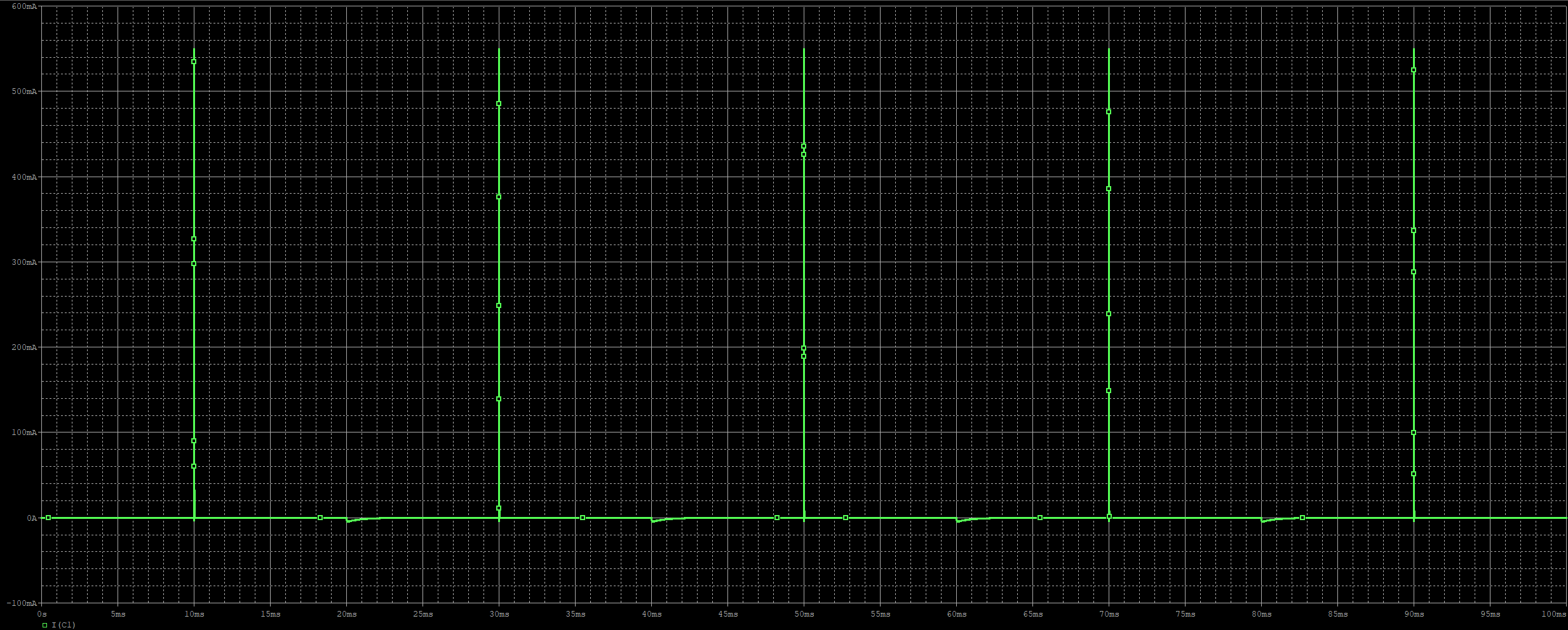

inrush currnet가 줄어들었음을 볼 수 있다.

but, discharge할 때, delay가 발생함을 볼 수 있다.

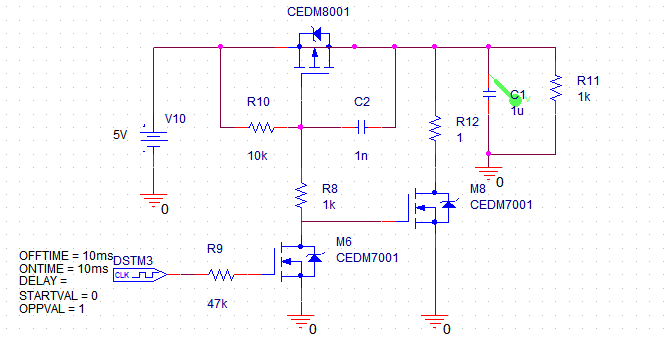

delay크게 감소한 것을 볼 수 있다.