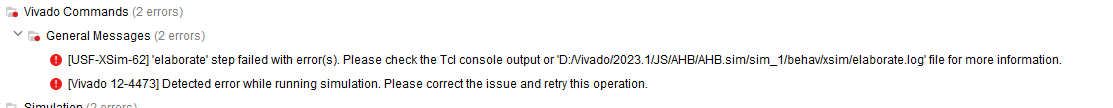

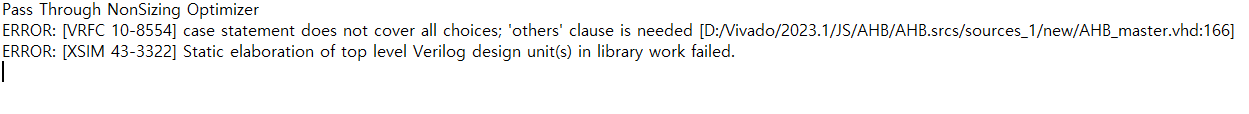

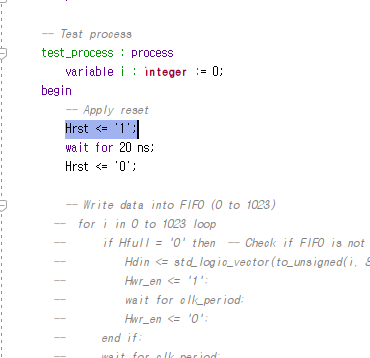

시뮬레이션을 돌리던 중에 다음과 같은 에러가 발생했다

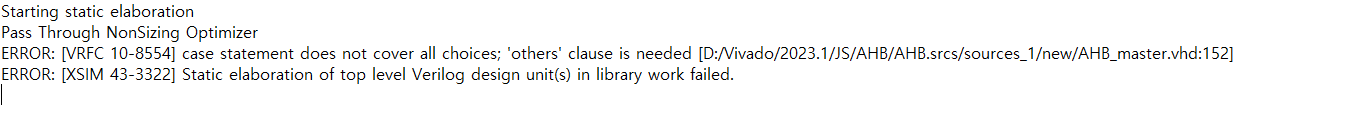

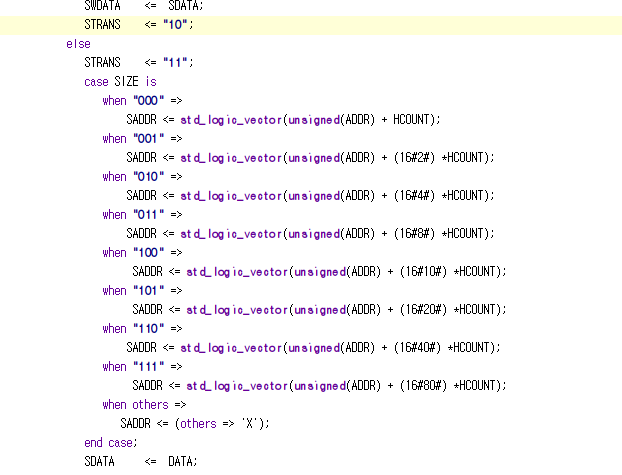

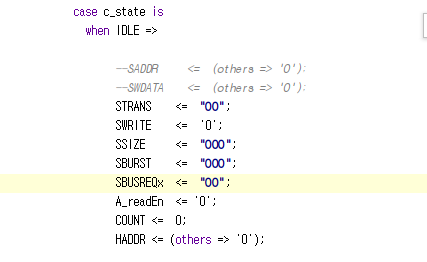

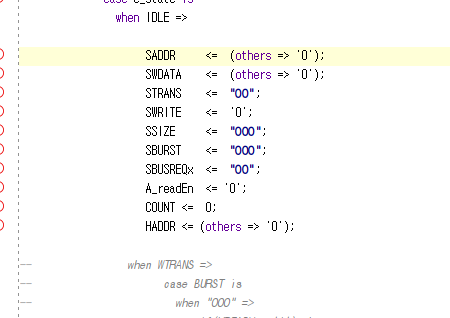

모든 case를 커버하지 못한 case문에 others를 안넣었다...

아직 Burst기능을 모두 추가하지 않아 완성시켜놓지 못한 Case가 문제였다

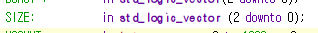

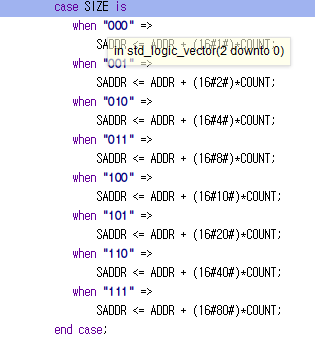

others를 추가해주었다.

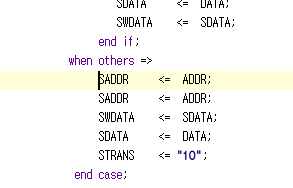

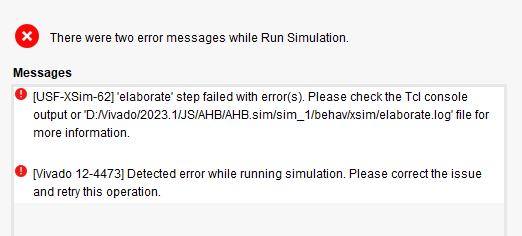

또다른 에러발생

같은 문제인데....

그러나 size는 보다시피 3bit vector이고 8가지 case가 모두 나와있다...

워가 문제인건지...

출처:https://vhdlwhiz.com/case-when/

좀 조사를 해보니 U, X, Z와 같은 상태도 포함되기 때문에 others문이 필요한 것같다.

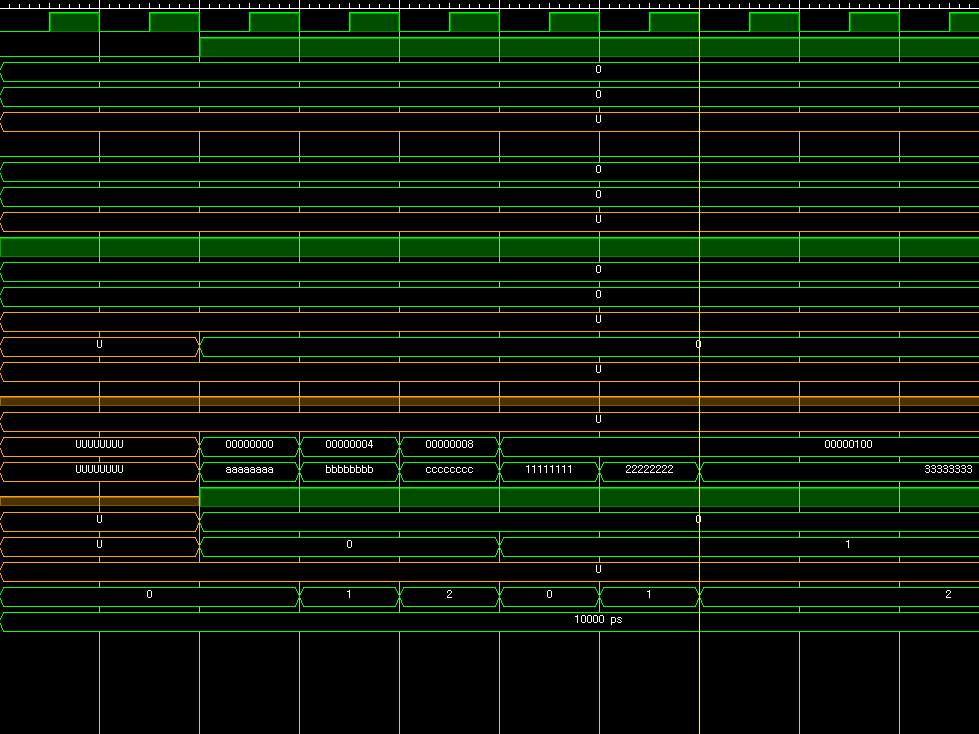

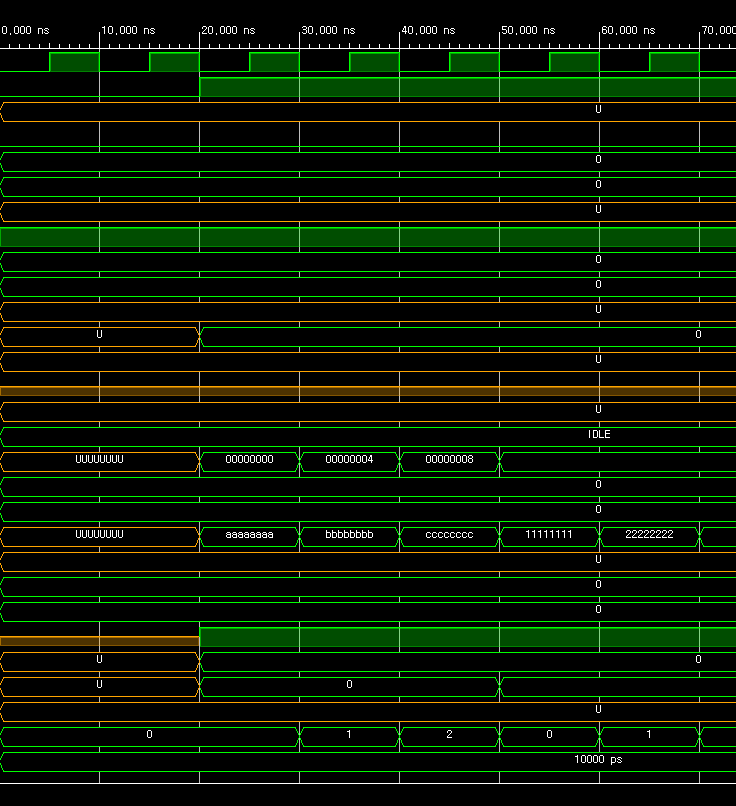

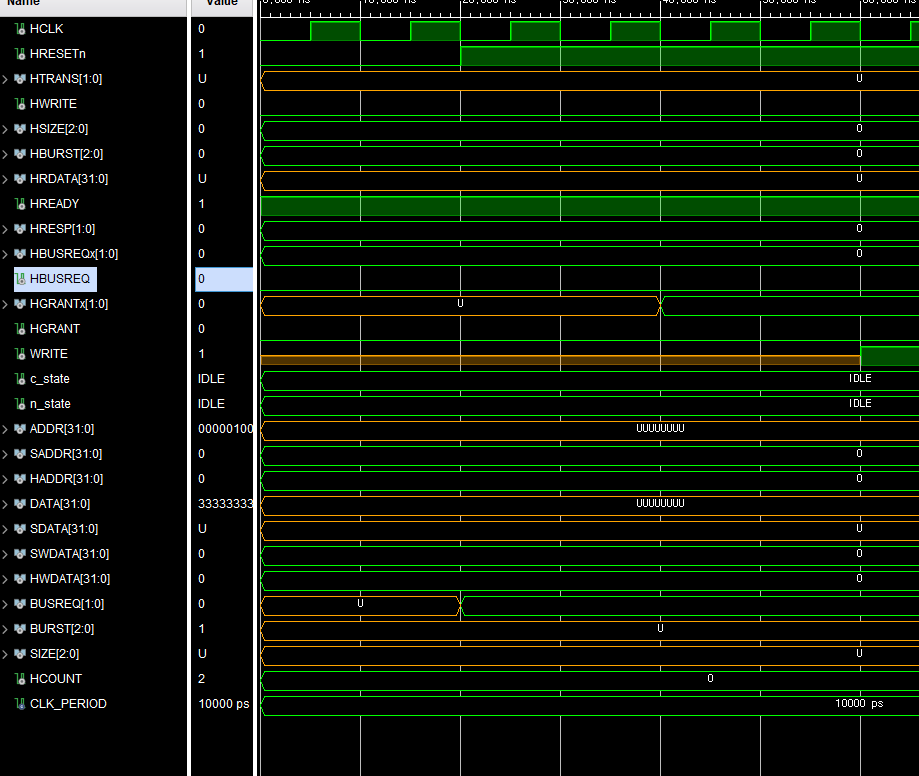

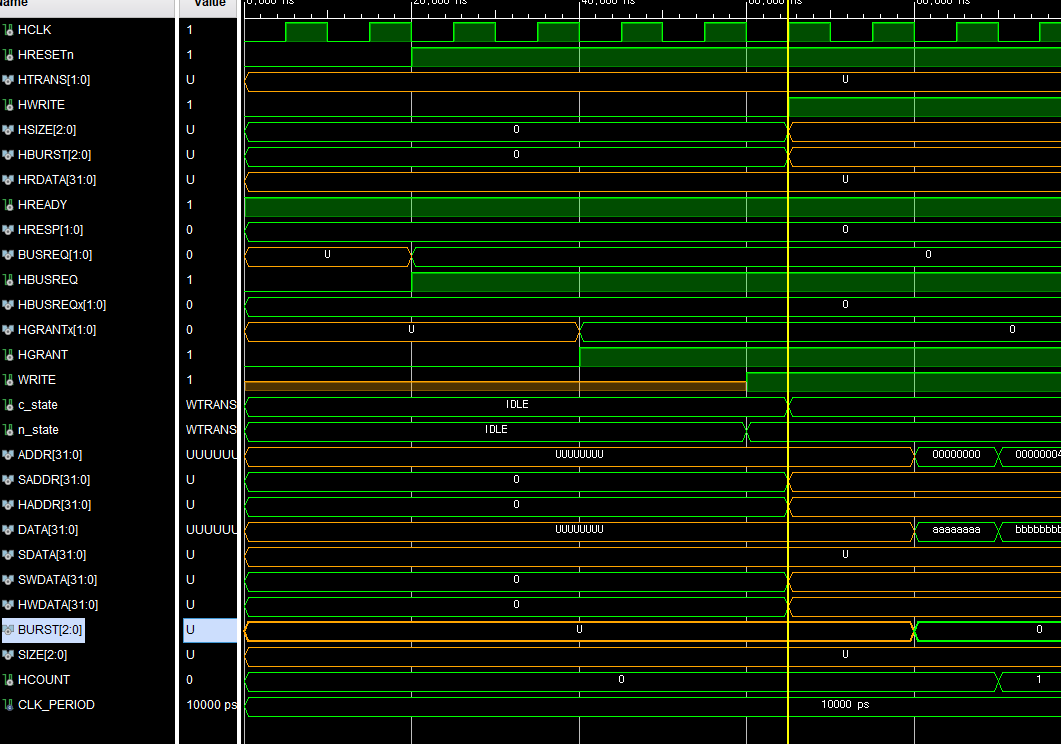

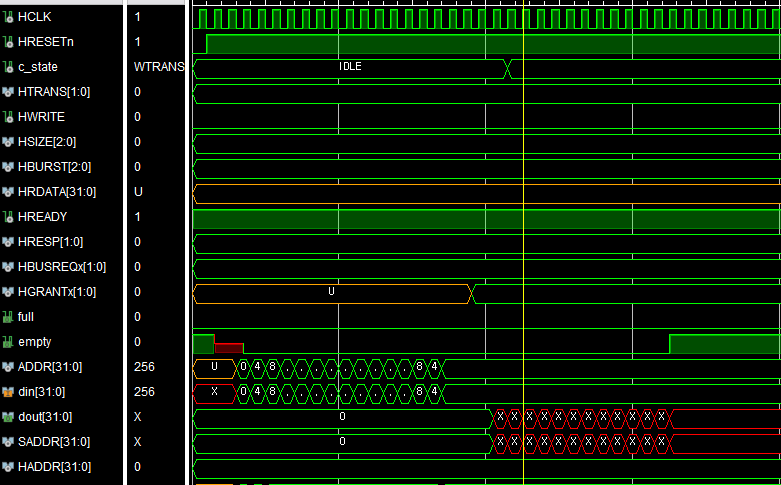

시뮬레이션은 작동했다

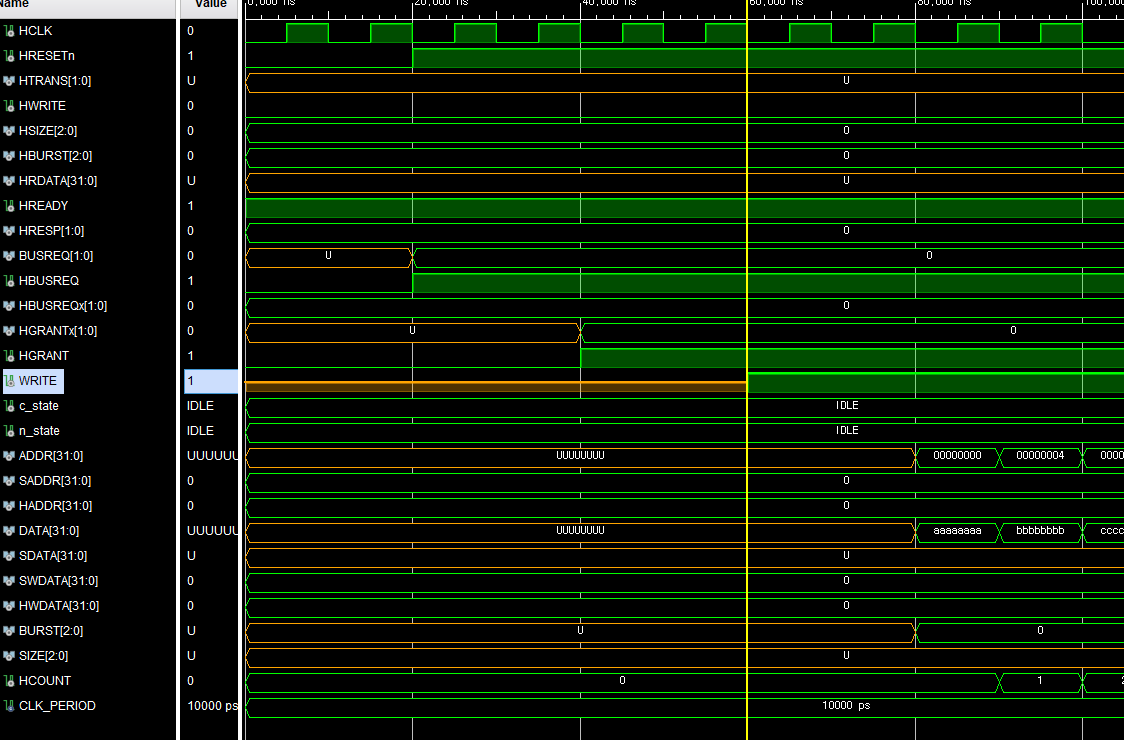

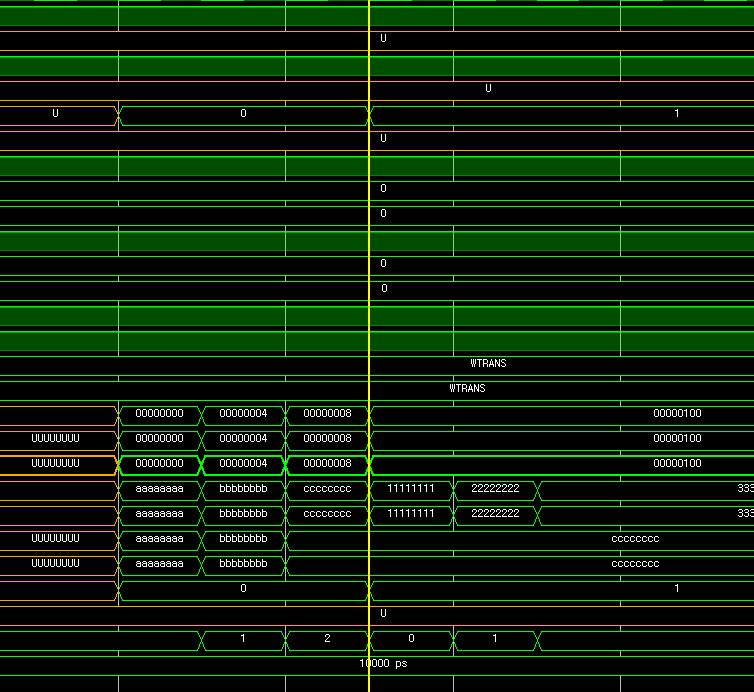

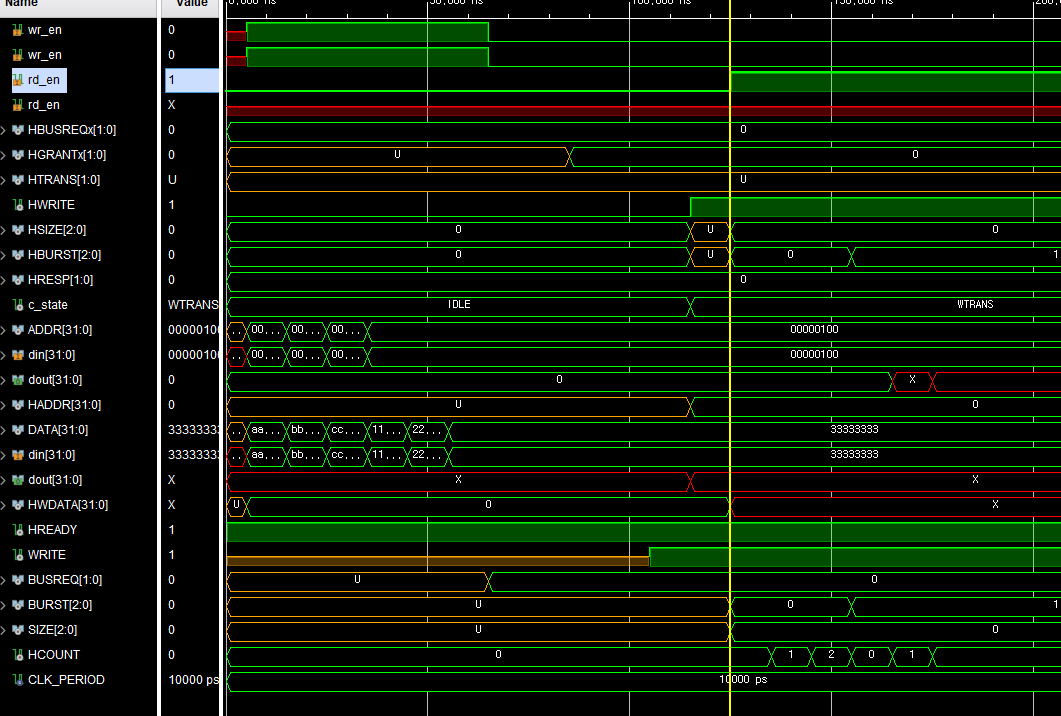

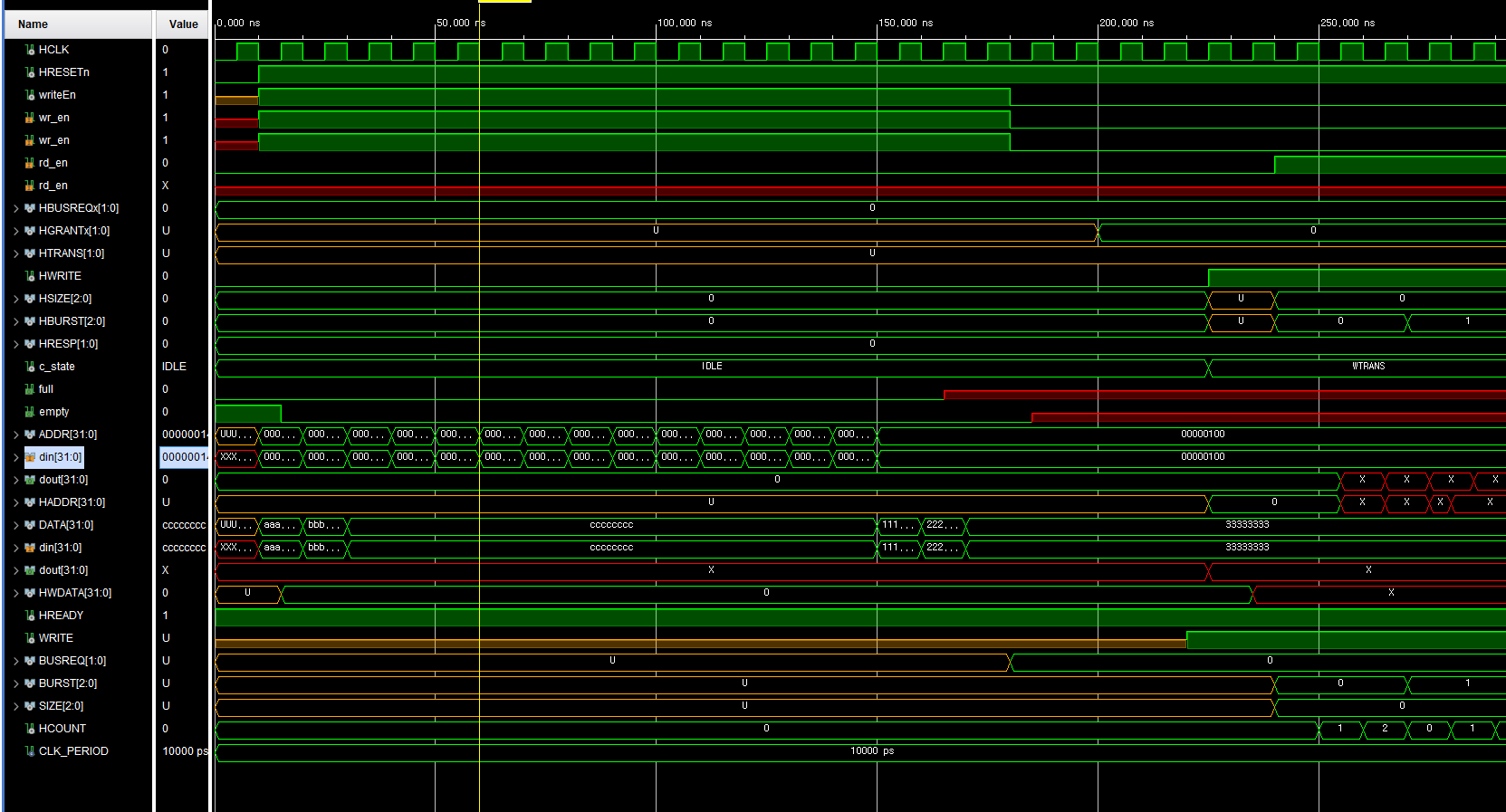

state가 안돈다.. 뭔가 문제가 있다

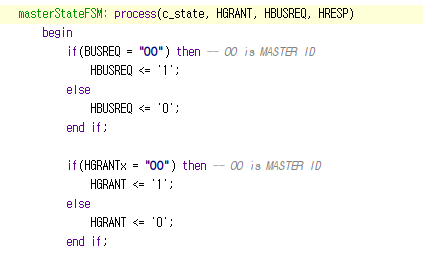

HBUSREQ신호와 HGRANT가 죽어있다!!

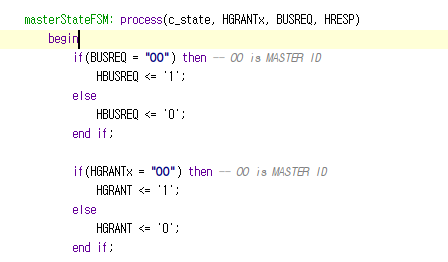

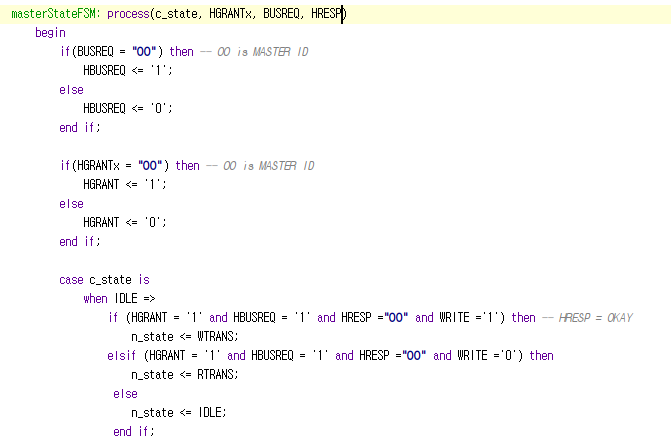

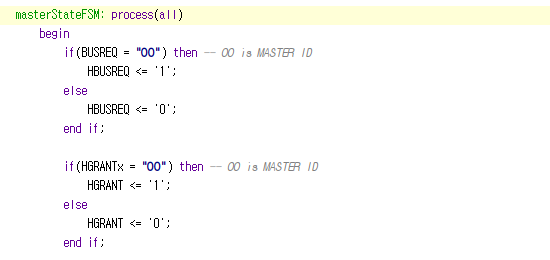

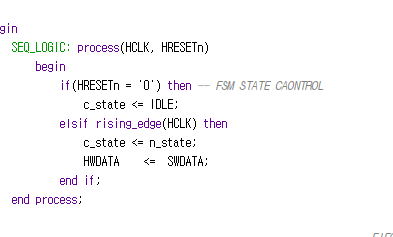

이 if문이 동작을 못하는듯 하다

process내부의 입력신호를 잘못줬다 ㅋㅋㅋ

이래서 비슷한 이름으로하면 안되는듯하다

그래도 안됨 ㅋㅋㅋ

일단 조건을 보자

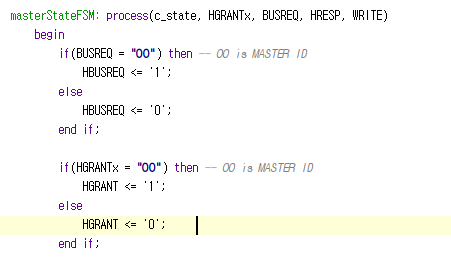

signla 목록에 WRITE가 없어서 그런가?

추가해줬다

state가 넘어간다 ㅎㅎㅎ

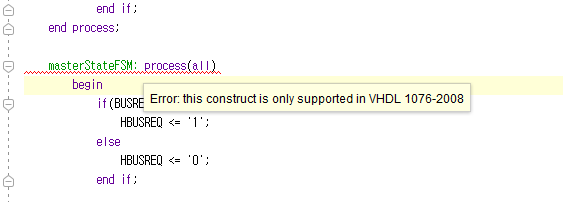

신호를 일일히 넣기 싫어서 all을 쓸라고 하니, VHDL 2008에서만 호환된다고 한다

출처:https://vhdlwhiz.com/snippets/vivado-set-vhdl-2019-or-2008-for-all-vhd-files/

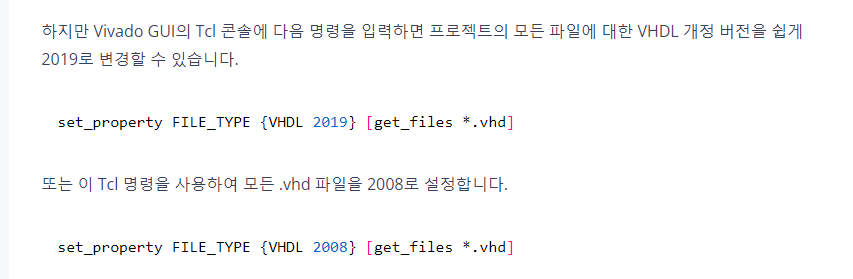

set_property FILE_TYPE {VHDL 2008} [get_files *.vhd]

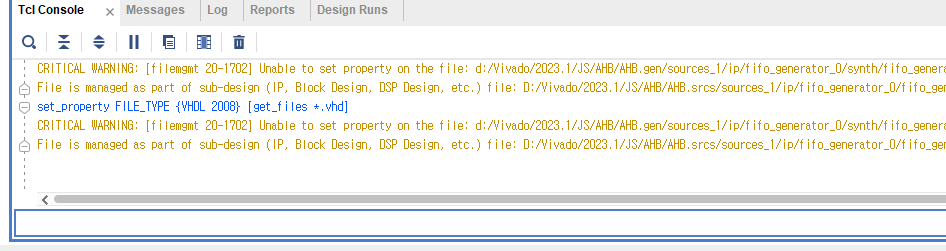

2008 버전으로 하기위해 위의 명령어르 TCL콘솔에 입력하자

여기에 입력하면

더는 에러가 안나온다

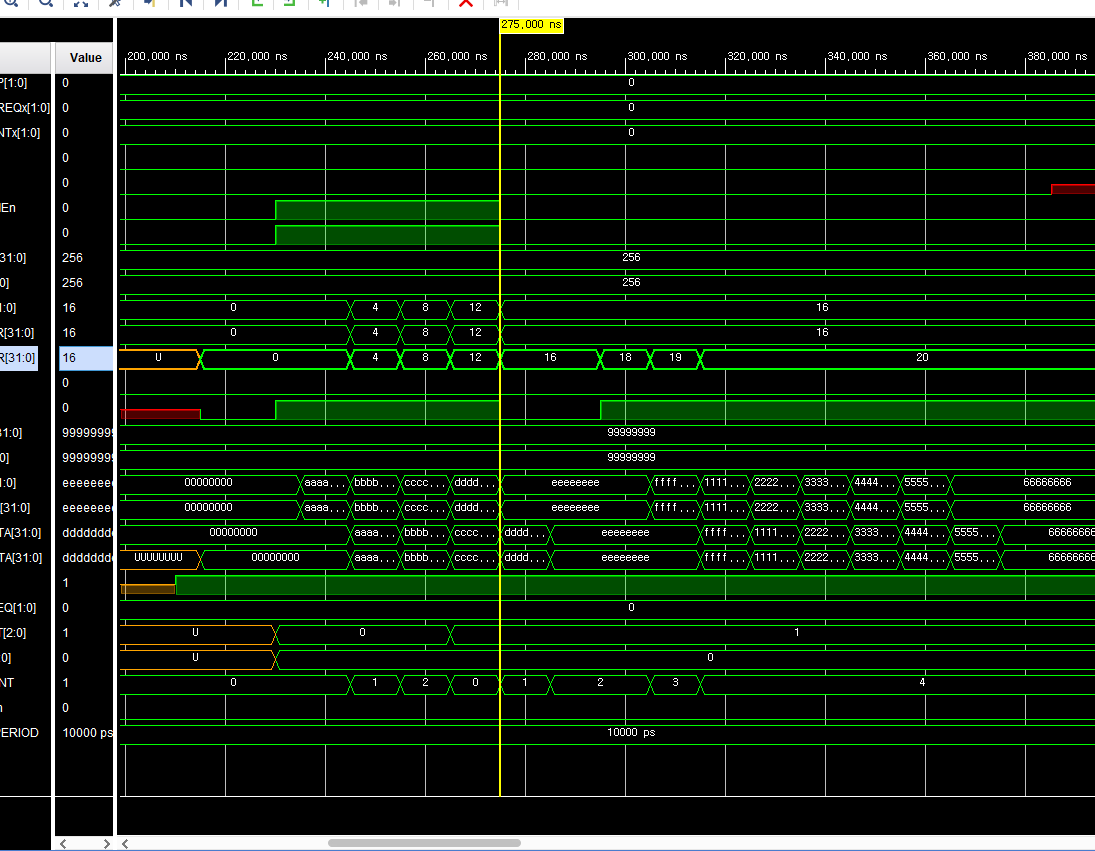

출력은 이제 잘되는데 addr과 data가 같은 타이밍에 나오고 burst는 제대로 동작을 안한다...

표준 라이브러리인 use IEEE.NUMERIC_STD.ALL;만 사용하기 위해 수정

IEEE.STD_LOGIC_ARITH와 IEEE.STD_LOGIC_UNSIGNED를 제거했다

BURST의 경우, Counter의 형식과 ADDR의 형식을 맞춰주었더니 잘된다

data 출력을 한클럭 늦췄다

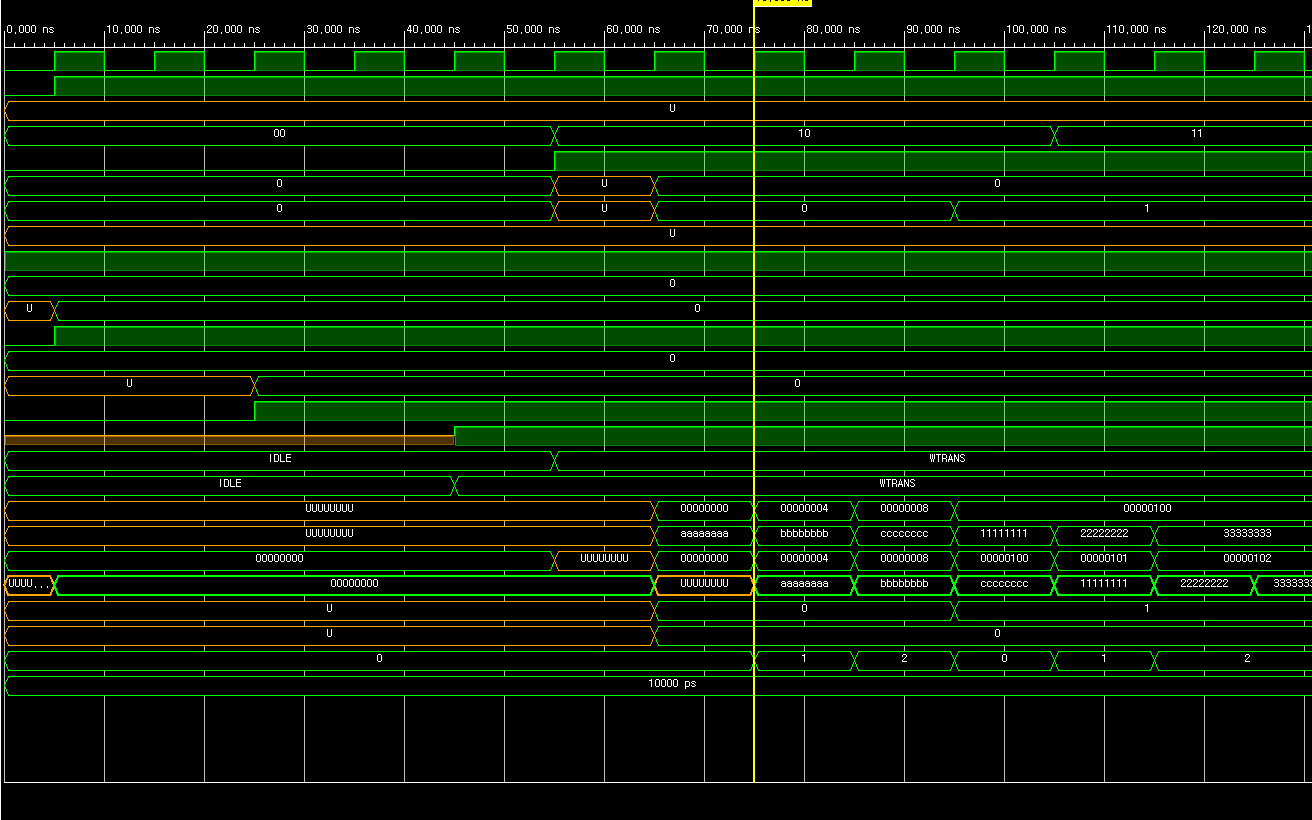

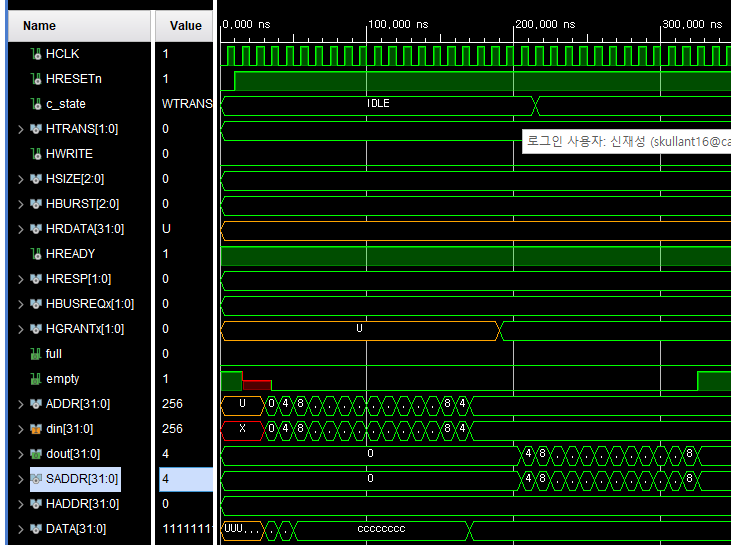

FIFO를 합쳐보았다...

신호는 정상적으로 준것 같은데 안나온다...

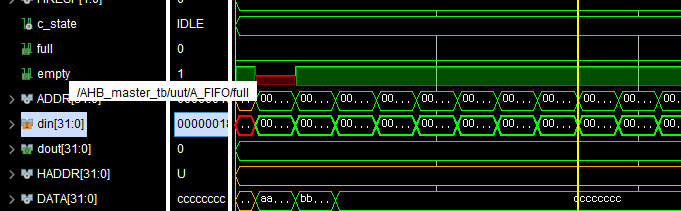

확인결과 FIFO에 값이 아예 안들어간다

FIFO단독 검증에서는 Empty가 0으로 된것을 볼 수 있다

즉, write enable 관련 문제인듯 싶은데..

알았다..

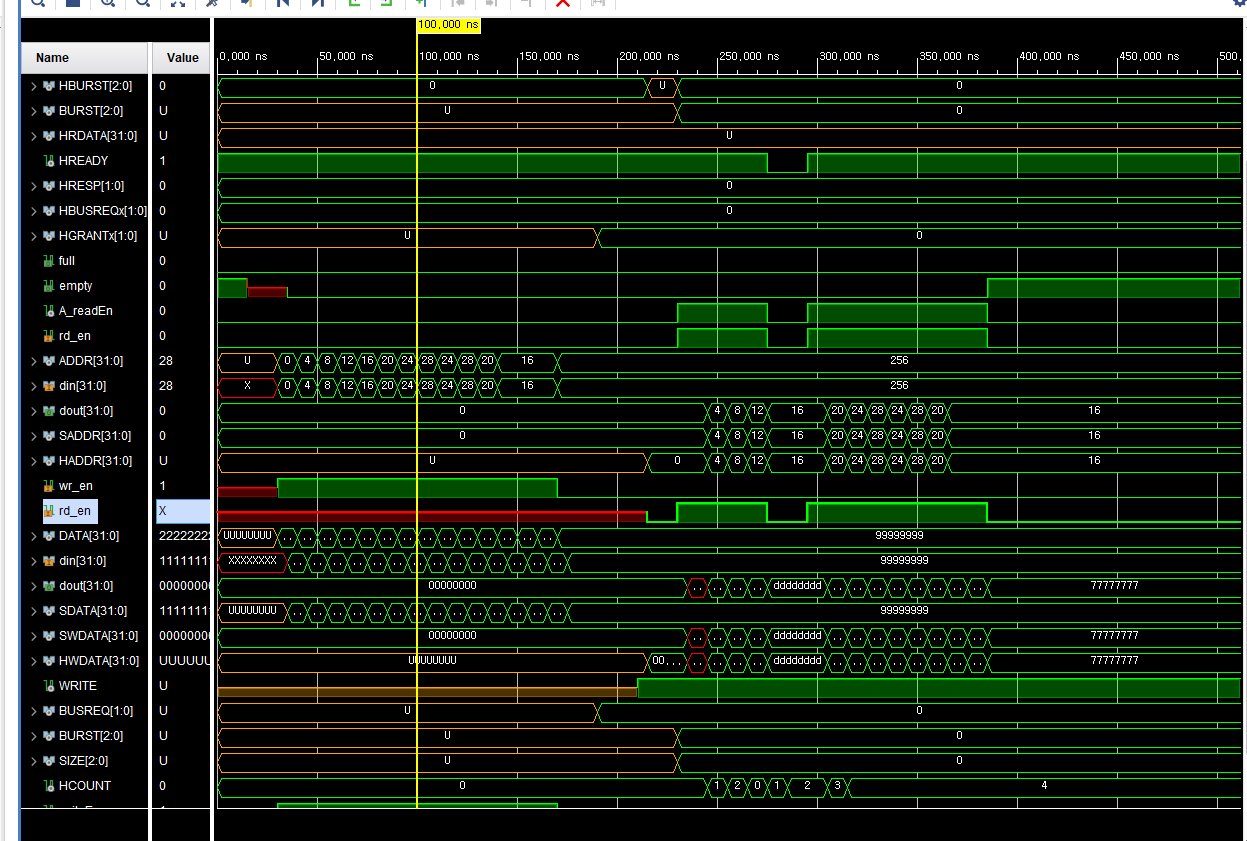

AHB는 negative reset인데 FIFO는 Positive reset이었다

rst라는 signal을 만들어주어 RESETn의 반대 값을 넣어주어 FIFO를 동작시켰다

근데도 출력데이터는 X가 나온다...

아무래도 FIFO의 out과 연결된 것에 간섭하면 out값이 터지는 것같다...

모든 코드를 주석걸고 문제가 되는 코드를 제외해야겠다.

ex)

SADDR을 주석걸면 잘나오던 출력이

주석을 풀면 죽어버린다...

아무래도 FIFO out에 관여하는 신호에 input을 넣어 racing 상태가 된듯하다

코드 수정후, Data가 잘 나오지만 이제는 타이밍을 맞춰주어야한다.

FIFO입력을 1clk 미뤄주었더니 잘된다.

이제 Count를 추가하자