9/14(목) 요약정리

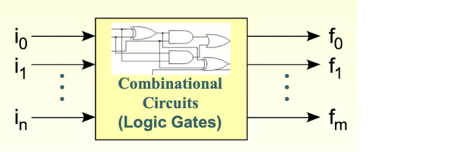

1-5. Combinational Circuits(조합 회로)

- 입력 변수들의 신호값들이 들어오는 즉시 출력값으로 바로 결정됨.

- 논리 소자들로 구성된 조합 회로를 통과하는데 걸리는 시간 → 없다 라고 간주.

순차 회로

- 조합 회로 중간 중간에 기억소자가 들어가는 것 : Flip Flop(1비트짜리 정보를 기억함) 이라고 함

- ex) 자판기를 생각하면 됨. 100원 투입 → 아무것도 선택 불가능, 1000원 넣음 → 콜라 먹을 수 있음. 입력값들이 계속 들어오고, 그걸 저장해놨다가 만족할 만한 값이 들어오면 그때 출력.

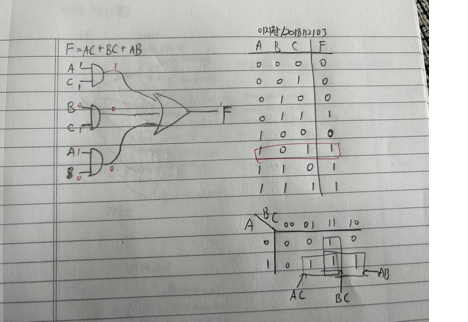

Analysis(분석)

- Logic circuits diagram —>. Boolean function(불리언 함수식) of Truth Table(진리표)

- 회로가 주어지고, 어떻게 동작하는지 찾아내는 것

Design(설계) : Analysis의 반대

- 문제 이해

- 입출력 변수의 이름 걀정

- 진리표(Truth Table) 작성

- 간소화 (Simplify Boolean Function) : K-Map / Boolean 대수 이용

- 논리 회로(Logic circuit diagram) 그리기

Ex)

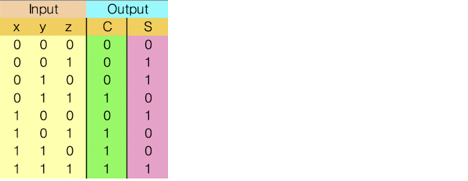

- Design Example : Half Adder

-

조합 회로. 한 비트짜리 입력 두개를 받아서 더하는 것.

-

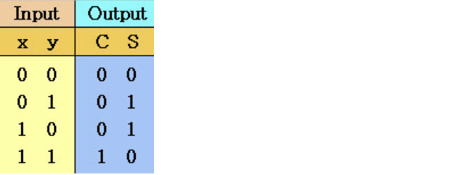

2 Input (x, y), 2 Output( S : sum, C : carry )

-

진리표(Truth Table)

여기서 carry 값은 두 입력값이 1,1 일 때만 생김

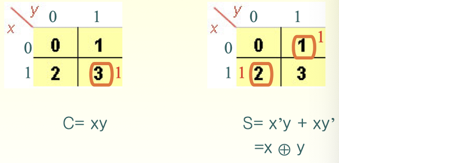

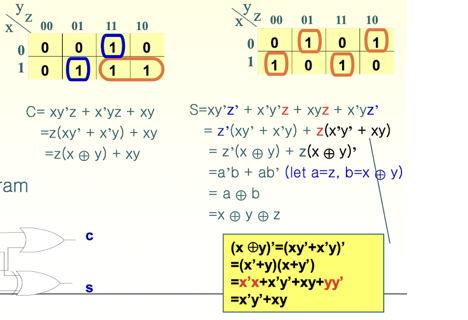

- 간소화 (Simplification)

두번째 그림에선 compliment 때문에 carry가 생기는 경우가 더 있음

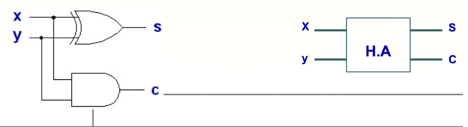

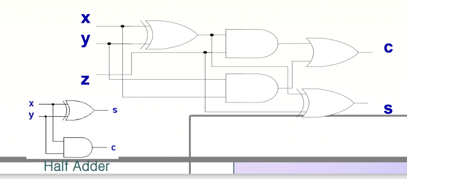

- 논리 회로 (Logic circuit diagram) / 6. Block diagram

5. or 게이트 통과시키면 sum, and 게이트 통과시키면 carry 6. x, y 입력, 출력은 sum과 carry, 가운데는 Half Adder의 약자- Full Adder

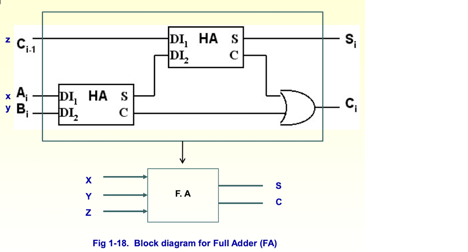

- 조합 회로인데, 3개의 입력값들을 서로 더하는 것. 전 단에서 올라오는 Carry값도 같이 공유.

- 3개의 input, 2개의 Output

- 진리표 (Truth table)

- 간소화 (Simplification)

왼쪽 K-Map의 경우 정석의 그루핑이 아님(최대한 크지가 않음). 여기선 Full Adder는 Half Adder 두개를 이용해서 구성할 수 있다는 걸 보여주기 위해서 이렇게 함.

오른쪽 그림은 네 개의 민텀들로 표현할 수밖에 없음. 노란색 박스는 Exclusive NOR에 해당하는 부분이 안의 내용과 같이 전개해서 나온다는 것을 보여줌.

- 논리 회로 (Logic circuit diagram)

XOR를 이용해서 x, y를 입력으로 넣고, z값과 AND 시킴. xy를 AND로 묶는 것은 그 아래 AND게이트에서 해줌. 그것의 출력 값을 OR, XOR로 묶어서 carry, sum 값 나오게 함.

Half Adder 두개로 Full Adder를 보여줄 수 있다는 것이 설명됨.

입력값 x,y,z 세 개, 출력값은 sum, carry 두 개.

ex )

출력값이 1이면 입력으로 1의 개수가 더 많이 들어왔다는 것. 0이 더 많다 - 2, 3개의 입력 값이 0이면 0으로 튀어나온다. 짜장면 1, 짬뽕 0으로 생각하면 이해 쉬움.

1-6. Flip-Flops

한 비트짜리 기억 소자. 순차 회로는 논리 소자 + F/F

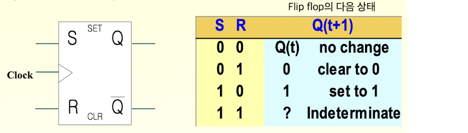

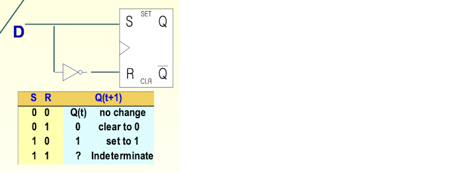

- SR(Set/Rest) F/F

Clock값이 들어와야 Flip Flop이 동작함.

Q : 들어온 값을 그대로 내보내는 것.

Q 바 : 0들어오면 1, 1들어오면 0을 내보냄

CLR : 신호 들어오면 값이 다 0으로 clear

SET : 1로 set 시켜줌

Q(t+1) : 다음 상태

Q(t) : 현재 상태.

? : 다음 상태는 1이 될지 0이 될지 모른다. 랜덤 결정.

난수 발생에 SR 여러개 갖다붙혀서 이용할 수도 있음.

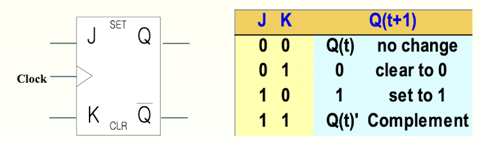

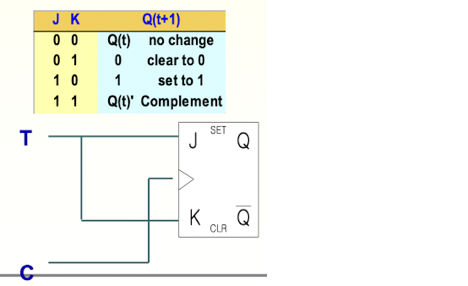

- JK(Jack/King) F/F

J는 SET, K는 RESET으로 이해하면 쉬움.

단자는 다 비슷함.

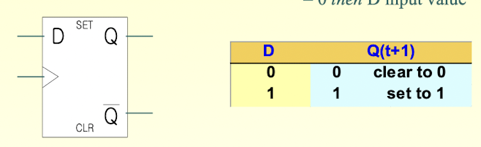

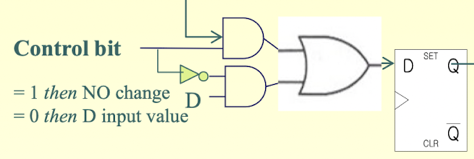

- D(Data) F/F

입력 단자가 위의 것들보다 하나 적고, 간단히 동작함.

0들어오면 0, 1들어오면 1.

특징

‘no change’ condition이 없음. 그냥 D에 값이 물리면 값이 결정되어버림.

해결법

1) Disalbe Clcok (Clock에 신호값이 안 물리도록)

2) Feedback output into input (출력 값을 피드백 시켜서 다시 입력으로 넣어주면)

Control bit라는 입력 신호가 들어옴.

1이 물리면 변화 없음. D F/F 때문에 이미 들어간 값을 다시 돌려서 D로 들어가게 해줌.

새로운 값 받아들이고 싶으면 0을 물림. 위에 있는 AND게이트는 동작 안 하는 것과 같음. AND Gate의 출력이 무조건 0이 나오기 때문임.

밑에 있는 것은 출력값이 , NOT Gate를 통해 1이 들어오면 나머지 입력 값은 새로운 값 주고 싶은 것을 AND Gate로 들어오게 함. 두 개의 입력값 중 하나는 이미 1이라서 D값이 1이면 출력은 1, 0이면 0이 나옴. 그 값이 D단자로 들어가고, 이런 방식으로 동작함.

D값이 0 —> S단자에 0, R에 1 들어감. 두번째 case.

D값이 1 —> S단자에 1, R에 0이 들어감. 세번쨰 case

결국 D F/F처럼 동작하게 됨. SR F/F도 D F/F처럼 동작하게 만들어줄 수 있는 것임.

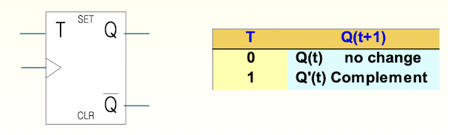

- T(Toggle) F/F

토글 → 바뀐다 의 의미.

T단자에 0 오면 현상태 그대로. 1이 들어오면 Complement 값이 옴.

이것 역시, 두 F/F를 동일하게 동작하도록 만들어줄 수 있다는 것.

T에 들어오는 게 똑같이 J, K에 다 물리게 만들어줌.

- 수식 표현

- T=1(J=K=1), T=0(J=K=0) 이면 JK F/F

-Edge-Triggered F/F

F/F들은 Clock에 맞춰서 값이 바뀜.

State Change

- Rising Edge (positive-edge transition)

- Falling Edge (negative-edge transition)

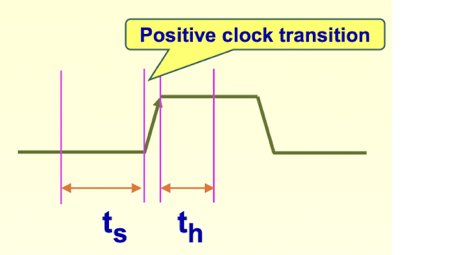

Setup time(20ns)

D F/F를 사용한다 치면, D단자로 들어오는 값은 20ns만큼의 신호값이 유지가 되어야 한다는 것.

Hold time(5ns)

상태변화가 이루어진 이후에 5ns의 hold time만큼은 변화가 없어야 한다.

setup, hold time은 F/F에서만 정의되며 일반 논리 gate에서는 정의되지 않음.

Propagation delay(max 50ns)

Clock 동작 시작 이후, 안의 상태 값이 바뀔 때까지의 시간을 말함.

-

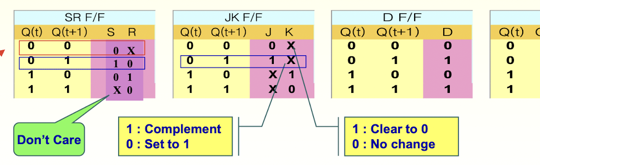

Excitation Table

현 상태가 뭐고, 다음 상태를 뭐로 받고 싶은지 —> 이 때 SR, JK 단자에 무엇을 물려줘야 원하는 상태 변화를 이끌어낼 수 있는지 알려주는 것임.